- 制造厂商:TI

- 产品类别:数据转换器

- 技术类目:模数转换器 (ADC) - 高速模数转换器 (>10MSPS)

- 功能描述:具有双通道 5.2GSPS 或单通道 10.4GSPS 的射频采样 12 位 ADC

- 点击这里打开及下载ADC12DJ5200RF的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

ADC12DJ5200RF 器件是一款射频采样千兆采样模数转换器 (ADC),可对从直流到 10GHz 以上的输入频率进行直接采样。 ADC12DJ5200RF 可配置为双通道 5.2GSPS ADC 或单通道 10.4GSPS ADC。支持高达 10GHz 的可用输入频率范围,可对频率捷变系统的 L、S、C 和 X 频带进行直接射频采样。

ADC12DJ5200RF 使用具有多达 16 个串行通道的高速 JESD204C 输出接口,支持高达 17.16Gbps 的线路速率。通过 JESD204C 子类 1 支持确定性延迟和多器件同步。JESD204C 接口可进行配置,对线路速率和通道数进行权衡。支持 8b/10b 和 64b/66b 数据编码方案。64b/66b 编码支持前向纠错 (FEC),可改进误码率。接口向后兼容 JESD204B 接收器。

无噪声孔径延迟调节和 SYSREF 窗口等创新的同步特性可简化多通道应用的系统设计。提供可选的数字下变频器 (DDC),以便将数字信号频谱下变频到基带信号并降低接口速率。可编程 FIR 滤波器可实现片上均衡。

- ADC 内核:

- 12 位分辨率

- 单通道模式下的采样率高达 10.4 GSPS

- 双通道模式下的采样率高达 5.2 GSPS

- 性能规格:

- 本底噪声(-20 dBFS,VFS = 1VPP-DIFF):

- 双通道模式:-151.8 dBFS/Hz

- 单通道模式:-154.4 dBFS/Hz

- ENOB(双通道,FIN = 2.4 GHz):8.6 位

- 本底噪声(-20 dBFS,VFS = 1VPP-DIFF):

- VCMI 为 0V 时的缓冲模拟输入:

- 模拟输入带宽 (-3dB):8 GHz

- 可用输入频率范围:> 10 GHz

- 满量程输入电压(VFS,默认值):0.8 VPP

- 无噪声孔径延迟 (tAD) 调节:

- 精确采样控制:19 fs 步长

- 简化同步和交错

- 温度和电压不变延迟

- 简便易用的同步特性:

- 自动 SYSREF 计时校准

- 样片标记时间戳

- JESD204C 串行数据接口:

- 最大通道速率:17.16 Gbps

- 支持 64b/66b 和 8b/10b 编码

- 8b/10b 模式兼容 JESD204B

- 可选数字下变频器 (DDC):

- 4 倍、8 倍、16 倍和 32 倍复杂抽取

- 每个 DDC 均具有四个独立的 32 位 NCO

- 峰值射频输入功率 (Diff):+26.5 dBm(+ 27.5 dBFS,560x 满量程功率)

- 可实现均衡的可编程 FIR 滤波器

- 功耗:4W

- 电源:1.1V/1.9V

- Sample rate (Max) (MSPS)

- 5200, 10400

- Resolution (Bits)

- 12

- Number of input channels

- 2, 1

- Interface type

- JESD204B, JESD204C

- Analog input BW (MHz)

- 7900

- Features

- Ultra High Speed

- Rating

- Catalog

- Input range (Vp-p)

- 0.825

- Power consumption (Typ) (mW)

- 4000

- Architecture

- Folding Interpolating

- SNR (dB)

- 55.6

- ENOB (Bits)

- 8.8

- SFDR (dB)

- 65

- Operating temperature range (C)

- -40 to 85

- Input buffer

- Yes

ADC12DJ5200RF的完整型号有:ADC12DJ5200RFAAV、ADC12DJ5200RFAAVT、ADC12DJ5200RFZEG、ADC12DJ5200RFZEGT,以下是这些产品的关键参数及官网采购报价:

ADC12DJ5200RFAAV,工作温度:-40 to 85,封装:FCBGA (AAV)-144,包装数量MPQ:168个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:SNAGCU,TI官网ADC12DJ5200RFAAV的批量USD价格:2696(1000+)

ADC12DJ5200RFAAVT,工作温度:-40 to 85,封装:FCBGA (AAV)-144,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:SNAGCU,TI官网ADC12DJ5200RFAAVT的批量USD价格:2696(1000+)

ADC12DJ5200RFZEG,工作温度:-40 to 85,封装: (ZEG)-144,包装数量MPQ:168个,MSL 等级/回流焊峰值温度:Level-3-235C-168 HR,引脚镀层/焊球材料:SN/PB,TI官网ADC12DJ5200RFZEG的批量USD价格:2898(1000+)

ADC12DJ5200RFZEGT,工作温度:-40 to 85,封装: (ZEG)-144,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-3-235C-168 HR,引脚镀层/焊球材料:SN/PB,TI官网ADC12DJ5200RFZEGT的批量USD价格:2898(1000+)

ADC12DJ5200RFEVM ― ADC12DJ5200RF 射频采样 12 位双通道 5.2GSPS 或单通道 10.4GSPS ADC 评估模块

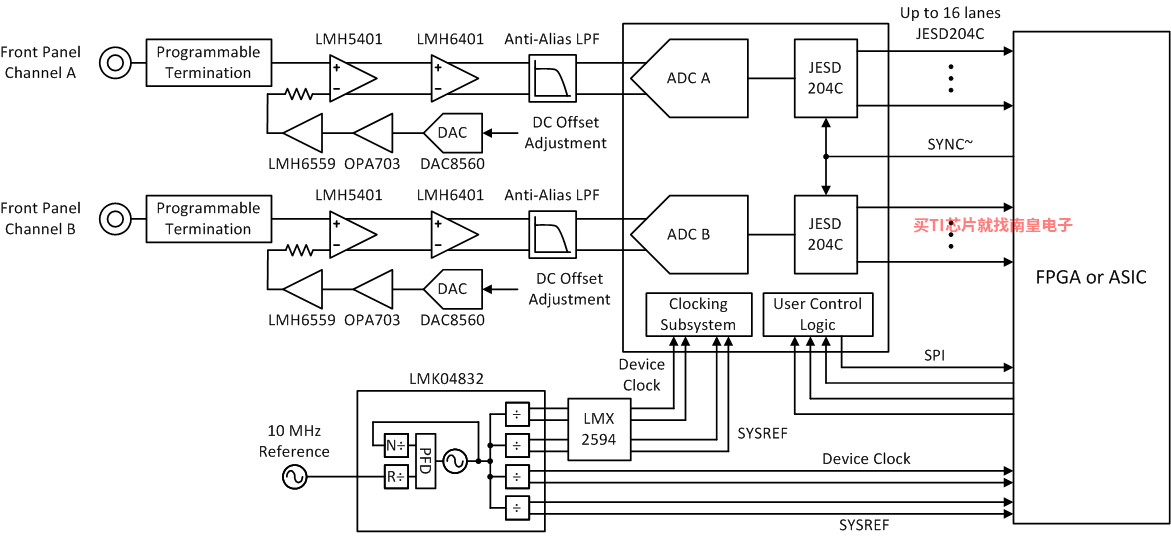

ADC12DJ5200RF 评估模块 (EVM) 可用于评估 ADC12DJ5200RF 器件。ADC12DJ5200RF 是一款具有缓冲模拟输入的低功耗、12 位、双通道 5.2GSPS/单通道 10.4GSPS、射频采样模数转换器 (ADC),集成了具有可编程 NCO 和抽取设置(包括非抽取 12 位和 8 位 ADC 输出)的数字下变频器,该变频器具有 JESD204B/C 接口。该 EVM 具有变压器耦合模拟输入,可适应各种信号源和频率。

EVM 中包含 LMX2582 时钟合成器和 LMK04828 JESD204B/C 时钟生成器,可以将其配置为超低抖动 ADC 器件时钟和 (...)

ANNAP-3P-WWDM60 ― Annapolis Microsystems 4-channel ADC, 2-channel DAC FPGA mezzanine card up to 10GSPS

This high performance WILD FMC+ DM60 ADC & DAC has two input bandwidth options, internal sample clock options and internal 10MHz reference clock options. The WWDM60 has a choice of speed grades that utilize the ADC12DJ2700, ADC12DJ3200 and ADC12DJ5200RF up to 10GSPS. It allows for ADC and DAC (...) 发件人: Annapolis Micro SystemsTI-JESD204-IP ― JESD204 快速设计 IP,用于连接到 TI 高速数据转换器的 FPGA

JESD204 快速设计 IP 旨在为 FPGA 工程师提供一条快速通往运行中的 JESD204 系统的路径。该 IP 经过特别设计,可将下游数字处理和其他应用逻辑与 JESD204 协议的大多数性能和时序关键型限制因素隔离开。该 IP将帮助设计人员节省固件开发时间并简化 FPGA 集成。JESD204 快速设计 IP 免专利费,可与 TI 高速数据转换器配合使用。TI 将协助用户配置初始链路,该链路可定制,以便在特定 FPGA 平台和 TI 数据转换器 JMODE 之间使用。 在对该 IP 进行测试并确定其可以用于部署工作之后,TI 将会通过安全的下载链接提供该 IP。

JESD204 (...)

DATACONVERTERPRO-SW ― High Speed Data Converter Pro 软件

此高速数据转换器专业 GUI 是一款 PC 程序(兼容 Windows XP/7/10),旨在帮助评估大多数 TI 高速数据转换器和模拟前端 (AFE) 平台。DATACONVERTERPRO-SW 支持整个 TSW14xxx 系列的数据采集和模式生成卡,为分析时域和频域中的数据转换器提供了快速强大的解决方案以及单音调、多音调和调制信号支持。此 GUI 还兼容用于快速合成单音调、多音调和调制信号的 TI 模式生成 GUI。用户可以为 DATACONVERTERPRO-SW 提供定制模式,以加载到 TI 数模转换器 (DAC)。支持从模数转换器 (ADC) 采集内导出 CSV (...)

ADC12DJ5200RF IBIS Model

PSpice for TI 可提供帮助评估模拟电路功能的设计和仿真环境。此功能齐全的设计和仿真套件使用 Cadence 的模拟分析引擎。PSpice for TI 可免费使用,包括业内超大的模型库之一,涵盖我们的模拟和电源产品系列以及精选的模拟行为模型。借助?PSpice for TI 的设计和仿真环境及其内置的模型库,您可对复杂的混合信号设计进行仿真。创建完整的终端设备设计和原型解决方案,然后再进行布局和制造,可缩短产品上市时间并降低开发成本。

在?PSpice for TI 设计和仿真工具中,您可以搜索 TI (...)

FREQ-DDC-FILTER-CALC ― 射频采样频率规划器、模拟滤波器和 DDC Excel 计算器

此 Excel 计算器为系统设计人员提供了一种方法,可用于简化直接射频采样接收器的设计和调试过程。它提供三种功能:频率规划、模拟滤波和抽取滤波器杂散位置。在概念阶段,频率规划工具可微调 ADC 采样率和输入频率位置,以便在出现阻塞事件时优化无杂散动态范围 (SFDR)。一些设计在这两个方面都很灵活;而 L 波段接收器或无线基础设施基站等其他设计则处理固定频段,且只提供采样率调优。

外部射频滤波器响应很大程度上取决于系统 SFDR 目标和 ADC 本身的 SFDR 性能;模拟滤波器工具可在设计阶段提供相关帮助。

在系统启动期间,如果快速傅里叶变换 (FFT) (...)

ADC12DJ5200RF-EVM Assembly Package (Rev. A)

此参考设计介绍采用时序交错配置射频采样模数转换器 (ADC) 的 20.8GSPS 采样系统。时序交错法是一种经实践检验可提高采样率的传统方法,然而,匹配个别 ADC 失调电压、增益和采样时间不匹配是实现性能的关键。随着采样时钟频率的增加,交错复杂性也随之增加。ADC 之间的相位匹配是实现更出色的 SFDR 和 ENOB 的关键规格之一。本参考设计通过采用简化 20.8GSPS 交错实施的 19fs 精确相位控制措施,在 ADC12DJ5200RF 上应用了无噪声孔径延迟调节功能。本参考设计基于符合 12 位系统性能要求的 LMK04828 和 LMX2594,采用了板载低噪声 (...)TIDA-01028 ― 适用于高速示波器和宽带数字转换器的 12.8-GSPS 模拟前端参考设计

此参考设计提供了一个用于实现 12.8GSPS 采样率的交错射频采样模数转换器 (ADC) 的实用示例。这可通过对两个射频采样 ADC 进行时序交错来实现。交错需要在 ADC 之间进行相移,此参考设计通过 ADC12DJ3200 的无噪声孔径延迟调节(tAD 调节)功能来实现相移。此功能还可用于最大限度地减少交错 ADC 常见的失配问题:最大程度地提升 SNR、ENOB 和 SFDR 性能。此参考设计还采用了支持 JESD204B 的低相位噪声时钟树,该时钟树通过 LMX2594 宽带 PLL、LMK04828 合成器以及抖动清除器来实现。TIDA-01027 ― 可最大限度提升 12.8GSPS 数据采集系统性能的低噪声电源参考设计

此参考设计显示了适用于能超过 12.8GSPS 的极高速 DAQ 系统的高效率、低噪声 5 轨电源设计。该电源的直流/直流转换器进行了频率同步和相移,从而使输入电流纹波最小并控制频率成分。此外,它还使用高性能 HotRod封装技术将任何潜在的辐射电磁干扰 (EMI) 降到了最低。