- 制造厂商:TI

- 产品类别:数据转换器

- 技术类目:模数转换器 (ADC) - 高速模数转换器 (>10MSPS)

- 功能描述:12 位、4.0GSPS、射频采样模数转换器 (ADC)

- 点击这里打开及下载ADC12J4000的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

ADC12J4000 器件为宽带采样和数字调谐器件。德州仪器 (TI) 的千兆次采样模数转换器 (ADC) 技术支持采用射频直接对大范围频谱采样。集成 DDC(数字下变频器)可进行数字滤波和下变频转换。所选频率块适用于 JESD204B 串行接口。数据以基带 15 位复数信息形式输出,以减轻下游处理压力。根据数字下变频器 (DDC) 抽取率和链接输出率设置,该数据将通过串行接口的 1 至 5 通道输出。

DDC 旁路模式还支持输出全速率 12 位原始 ADC 数据。此运行模式需要 8 个串行输出通道。

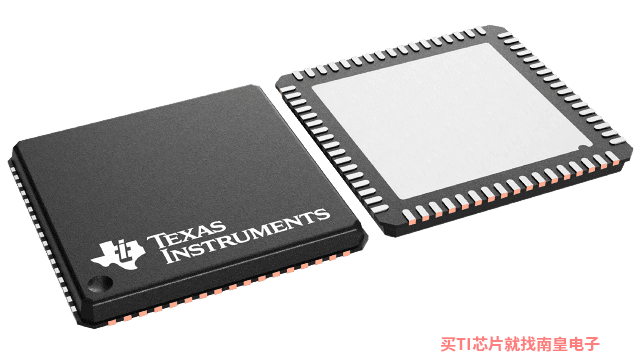

ADC12J4000 器件采用68 引脚超薄四方扁平无引线 (VQFN) 封装。该器件的工业环境运行温度范围为 –40°C ≤ TA ≤ 85°C。

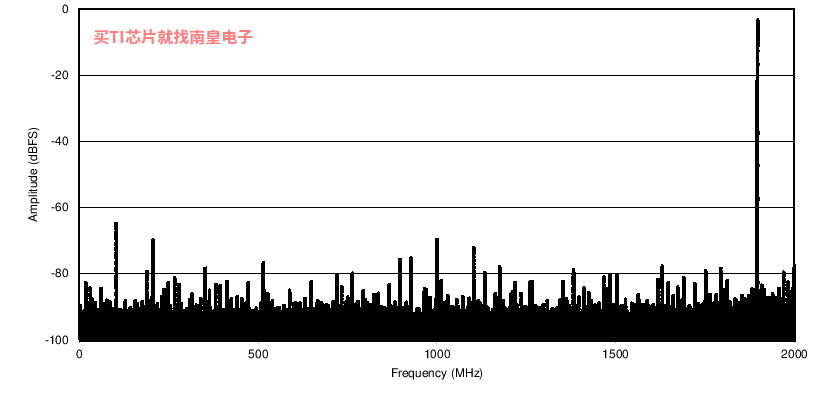

- 出色的噪声和线性性能,最高可达 FIN = 3GHz 以上

- 可配置数字下变频器 (DDC)

- 抽取因数范围为 4 至 32(复杂基带输出)

- 在 4x 抽取率和 4000MSPS 条件下,可用输出带宽为 800MHz

- 在 32x 抽取率和 4000MSPS 条件下,可用输出带宽为 100MHz

- 旁路模式适用于整个奈奎斯特输出带宽

- 低引脚数目 JESD204B 子类 1 接口

- 自动优化输出通道计数

- 嵌入式低延迟信号范围指示

- 低功耗

- 主要规格:

- 最大采样率:4000MSPS

- 最小采样率:1000MSPS

- DDC 输出字大小:15 位复数(共 30 位)

- 旁路输出字大小:12 位偏移二进制数

- 噪底:?149dBFS/Hz 或 ?150.8dBm/Hz

- 三阶互调失真 (IMD3):?64dBc(?13dBFS 时,FIN = 2140MHz ± 30MHz)

- 全功率带宽 (FPBW) (–3dB):3.2GHz))

- 峰值噪声功率比 (NPR):46dB

- 电源电压:1.9V 和 1.2V

- 功耗

- 旁路 (4000MSPS):2W

- 10 倍抽取率 (4000MSPS):2W

- 断电模式:< 50mW

- Sample rate (Max) (MSPS)

- 4000

- Resolution (Bits)

- 12

- Number of input channels

- 1

- Interface type

- JESD204B

- Analog input BW (MHz)

- 3200

- Features

- Ultra High Speed

- Rating

- Catalog

- Input range (Vp-p)

- 0.725

- Power consumption (Typ) (mW)

- 2000

- Architecture

- Folding Interpolating

- SNR (dB)

- 55

- ENOB (Bits)

- 8.8

- SFDR (dB)

- 71

- Operating temperature range (C)

- -40 to 85

- Input buffer

- Yes

ADC12J4000的完整型号有:ADC12J4000NKE、ADC12J4000NKER、ADC12J4000NKET,以下是这些产品的关键参数及官网采购报价:

ADC12J4000NKE,工作温度:-40 to 85,封装:VQFN (NKE)-68,包装数量MPQ:168个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:SN,TI官网ADC12J4000NKE的批量USD价格:1802.88(1000+)

ADC12J4000NKER,工作温度:-40 to 85,封装:VQFN (NKE)-68,包装数量MPQ:2000个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:SN,TI官网ADC12J4000NKER的批量USD价格:1800.88(1000+)

ADC12J4000NKET,工作温度:-40 to 85,封装:VQFN (NKE)-68,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:SN,TI官网ADC12J4000NKET的批量USD价格:1802.88(1000+)

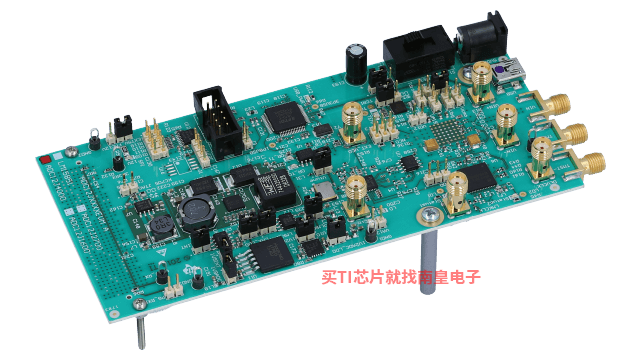

ADC12J4000EVM — ADC12J4000 12 位 4.0MSPS 射频采样模数转换器评估模块

ADC12J4000EVM 是一款用于评估 TI 的 ADC12J4000 的评估模块 (EVM)。ADC12J4000 是一款低功耗、12 位、4GSPS 射频采样模数转换器(ADC),具有缓冲模拟输入、具有可编程 NCO 和抽取设置(包括非抽取 12 位 ADC 输出)的集成数字下变频器,并采用 JESD204B 接口。该 EVM 具有变压器耦合模拟输入,可适应各种信号源和频率。EVM 中包含 LMX2581 时钟合成器和 LMK04828 JESD204B 时钟生成器,可以进行配置,以提供超低抖动 ADC 器件时钟和 SYSREF,从而实现完整的 JESD204B 子类 1 (...)

TSW12J54EVM — 宽带射频接收器参考设计

采用 8GHz 直流耦合全差分放大器的射频采样 4GSPS ADC。提供宽带宽、高性能的交流或直流耦合采集平台,其连续捕获带宽高达 2GHz。内置的 DDC 功能支持对捕获的信号进行调谐、降频转换和带宽缩减,从而实现灵活的射频采样应用开发。高带宽和直流耦合输入功能还支持高频时域应用。

TI-JESD204-IP — JESD204 快速设计 IP,用于连接到 TI 高速数据转换器的 FPGA

JESD204 快速设计 IP 旨在为 FPGA 工程师提供一条快速通往运行中的 JESD204 系统的路径。该 IP 经过特别设计,可将下游数字处理和其他应用逻辑与 JESD204 协议的大多数性能和时序关键型限制因素隔离开。该 IP将帮助设计人员节省固件开发时间并简化 FPGA 集成。JESD204 快速设计 IP 免专利费,可与 TI 高速数据转换器配合使用。TI 将协助用户配置初始链路,该链路可定制,以便在特定 FPGA 平台和 TI 数据转换器 JMODE 之间使用。 在对该 IP 进行测试并确定其可以用于部署工作之后,TI 将会通过安全的下载链接提供该 IP。

JESD204 (...)

DATACONVERTERPRO-SW — High Speed Data Converter Pro 软件

此高速数据转换器专业 GUI 是一款 PC 程序(兼容 Windows XP/7/10),旨在帮助评估大多数 TI 高速数据转换器和模拟前端 (AFE) 平台。DATACONVERTERPRO-SW 支持整个 TSW14xxx 系列的数据采集和模式生成卡,为分析时域和频域中的数据转换器提供了快速强大的解决方案以及单音调、多音调和调制信号支持。此 GUI 还兼容用于快速合成单音调、多音调和调制信号的 TI 模式生成 GUI。用户可以为 DATACONVERTERPRO-SW 提供定制模式,以加载到 TI 数模转换器 (DAC)。支持从模数转换器 (ADC) 采集内导出 CSV (...)

ADC12J4000 IBIS-AMI Model (Rev. A)

PSpice for TI 可提供帮助评估模拟电路功能的设计和仿真环境。此功能齐全的设计和仿真套件使用 Cadence 的模拟分析引擎。PSpice for TI 可免费使用,包括业内超大的模型库之一,涵盖我们的模拟和电源产品系列以及精选的模拟行为模型。借助?PSpice for TI 的设计和仿真环境及其内置的模型库,您可对复杂的混合信号设计进行仿真。创建完整的终端设备设计和原型解决方案,然后再进行布局和制造,可缩短产品上市时间并降低开发成本。

在?PSpice for TI 设计和仿真工具中,您可以搜索 TI (...)

FREQ-DDC-FILTER-CALC — 射频采样频率规划器、模拟滤波器和 DDC Excel 计算器

此 Excel 计算器为系统设计人员提供了一种方法,可用于简化直接射频采样接收器的设计和调试过程。它提供三种功能:频率规划、模拟滤波和抽取滤波器杂散位置。在概念阶段,频率规划工具可微调 ADC 采样率和输入频率位置,以便在出现阻塞事件时优化无杂散动态范围 (SFDR)。一些设计在这两个方面都很灵活;而 L 波段接收器或无线基础设施基站等其他设计则处理固定频段,且只提供采样率调优。

外部射频滤波器响应很大程度上取决于系统 SFDR 目标和 ADC 本身的 SFDR 性能;模拟滤波器工具可在设计阶段提供相关帮助。

在系统启动期间,如果快速傅里叶变换 (FFT) (...)

TIDA-00431 — 参考设计 - 采用 8GHz 直流耦合全差分放大器的 RF 采样 4GSPS ADC

宽带射频 (RF) 接收器有助于极大提升无线电设计中的灵活性。较宽的瞬时带宽支持灵活调节而无需改动硬件且能够以间隔较大的频率捕获多个通道。此参考设计介绍了一个宽带射频接收器,该接收器利用 4 GSPS 模数转换器 (ADC) 并具有一个 8GHz 直流耦合全差动放大器前端。放大器前端提供信号增益并允许采集下行到直流的信号,而平衡-非平衡变压器耦合输入则做不到这一点。

TIDA-01017 — 适用于示波器、无线测试器和雷达的高速多通道 ADC 时钟参考设计

TIDA-01017 参考设计展示了适用于高速多通道系统的时钟解决方案的性能,通过测量射频采样 ADC 的整个输入频率范围的通道间偏差进行分析。通道间偏差对于相控阵雷达和示波器应用至关重要。ADC12J4000 是一款低功耗、12 位、4GSPS 射频采样模数转换器 (ADC),具有缓冲模拟输入、集成式数字下变频器,采用 JESD204B 接口,并可捕获高达 4GHz 的信号。此设计展示了使用 LMK04828 的时钟解决方案,可使用同步 SYSREF 在多个 ADC12J4000 信号链之间实现同步。TIDA-01015 — 适用于数字示波器和无线测试器中的 12 位高速 ADC 的 4GHz 时钟参考设计

TIDA-01015 是一款适合高速直接射频采样 GSPS ADC 的时钟解决方案参考设计。该参考设计展示了采样时钟在为第二奈奎斯特区域输入信号频率实现高 SNR 方面的重要性。ADC12J4000 是一款 12 位 4GSPS 射频采样 ADC,具有 3.2GHz 的 3dB 输入带宽,能够捕获高达 4GHz 的信号。此参考设计突出了一款适合 ADC12J4000 的时钟解决方案,该器件采用 TRF3765,以在高输入频率条件下实现高 SNR 性能,适用于数字存储示波器 (DSO) 和无线测试仪等应用。TIDEP0034 — 66AK2L06 JESD 实现与宽带 ADC 和 DAC 的连接

此参考设计适用于目前使用 FPGA 或 ASIC 连接到高速数据转换器、需要在缩短上市时间的同时提高性能并显著降低成本、功耗和尺寸的开发人员,其中包含集成了 JESD204B 接口和数字前端 (DFE) 处理功能的首个广泛可用的处理器。通过连接 12J4000 ADC 和 38J84 DAC 可为测试和测量以及国防应用提供高效的解决方案。TIDA-00826 — 50Ω 2GHz 示波器前端参考设计

此参考设计是 50Ω 输入示波器应用的模拟前端的一部分。系统设计人员可轻松使用此评估平台来处理频域和时域应用中的直流到 2GHz 的输入信号。TIDA-00467 — 通过同步多个 JESD204B ADC 实现发射器定位参考设计

一种估算发射器位置的常用技术是使用在空间中分布的传感器阵列所发出的信号的振幅和相移数据。对于此类系统,必须保证传感器之间的确定性相位关系来减少实际测得的数据的误差,这一点十分重要。此应用设计将探讨如何同步多个带 JESD204B 接口的模数转换器 (ADC) 以便确保从 ADC 采样的数据在相位上一致。

TIDA-00432 — 将 Xilinx 平台应用于相位阵列雷达系统以实现 JESD204B 千兆次采样 ADC 的同步

此系统级设计展示了如何使用 Xilinx VC707 平台一起同步两个 ADC12J4000 评估模块 (EVM)。此设计文档介绍了必要的硬件修改和器件配置,包括时钟方案。此设计显示了每个 EVM 的示例配置文件。此设计介绍了 FPGA 固件,并显示相关的 Xilinx IP 块配置参数。此外还显示并分析了在实际硬件上采集的数据,测试结果显示出 50ps 内的同步,未使用特性化电缆,也未校准传播延迟。TIDA-00359 — 面向 GSPS ADC 的时钟解决方案参考设计

适用于 GSPS 数据转换器的低成本、高性能时钟解决方案。此参考设计讨论如何使用低噪声频率合成器 TRF3765 为 4 GSPS 模数转换器 (ADC12J4000) 生成采样时钟。实验展示了与数据表相当的 SNR 和 SFDR 性能。