- 制造厂商:TI

- 产品类别:数据转换器

- 技术类目:模数转换器 (ADC) - 高速模数转换器 (>10MSPS)

- 功能描述:12 位、170MSPS、1.1GHz 输入带宽模数转换器 (ADC)

- 点击这里打开及下载ADC12V170的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

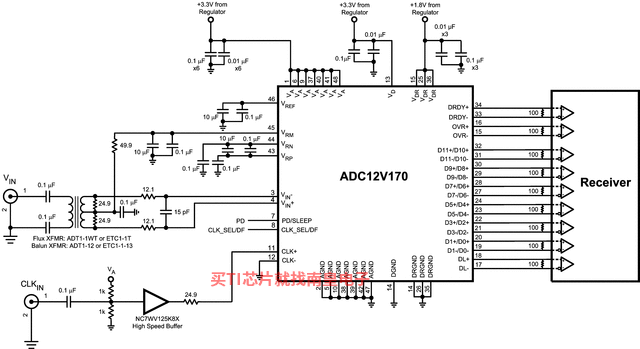

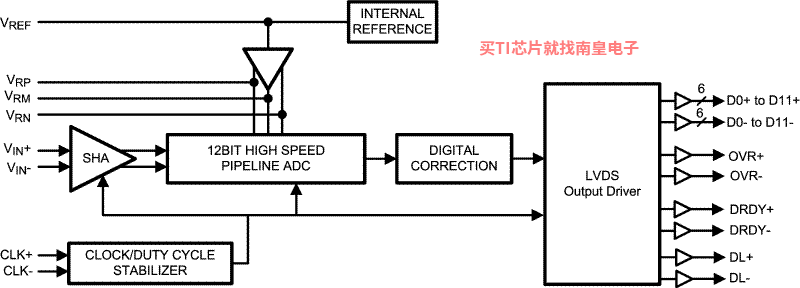

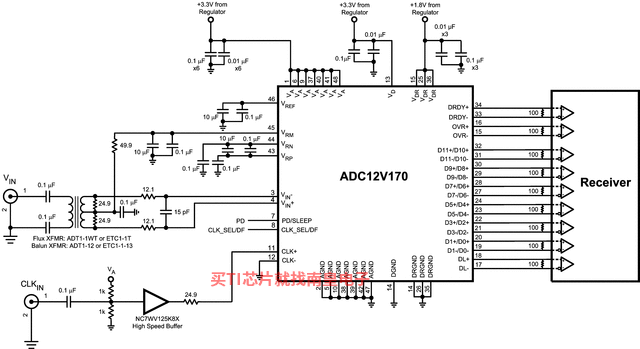

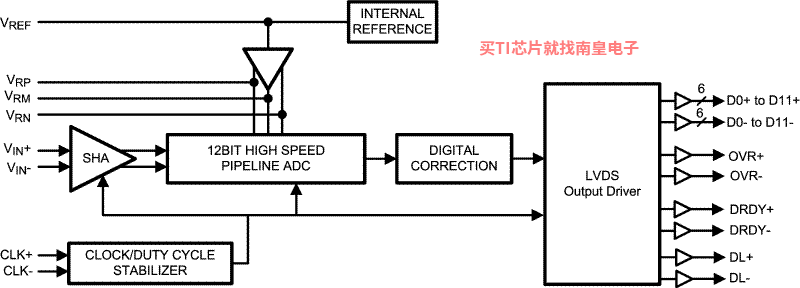

The ADC12V170 is a high-performance CMOS analog-to-digital converter with LVDS outputs. It is capable of converting analog input signals into 12-Bit digital words at rates up to 170 Mega Samples Per Second (MSPS). Data leaves the chip in a DDR (Dual Data Rate) format; this allows both edges of the output clock to be utilized while achieving a smaller package size. This converter uses a differential, pipelined architecture with digital error correction and an on-chip sample-and-hold circuit to minimize power consumption and the external component count, while providing excellent dynamic performance. A unique sample-and-hold stage yields a full-power bandwidth of 1.1 GHz. The ADC12V170 operates from dual +3.3V and +1.8V power supplies and consumes 781 mW of power at 170 MSPS.

The separate +1.8V supply for the digital output interface allows lower power operation with reduced noise. A power-down feature reduces the power consumption to 15 mW while still allowing fast wake-up time to full operation. In addition there is a sleep feature which consumes 50 mW of power and has a faster wake-up time.

The differential inputs provide a full scale differential input swing equal to 2 times the reference voltage. A stable 1.0V internal voltage reference is provided, or the ADC12V170 can be operated with an external reference.

Clock mode (differential versus single-ended) and output data format (offset binary versus 2's complement) are pin-selectable. A duty cycle stabilizer maintains performance over a wide range of input clock duty cycles.

The ADC12V170 is pin-compatible with the ADC14V155. It is available in a 48-lead WQFN package and operates over the industrial temperature range of −40°C to +85°C.

- 1.1 GHz Full Power Bandwidth

- Internal Sample-and-Hold Circuit

- Internal Precision 1.0V Reference

- Single-Ended or Differential Clock Modes

- Clock Duty Cycle Stabilizer

- Dual +3.3V and +1.8V Supply Operation

- Power-Down and Sleep Modes

- Offset Binary or 2's Complement Output Data Format

- LVDS Outputs

- Pin-Compatible: ADC14V155

- 48-Pin WQFN Package, (7x7x0.8mm, 0.5mm Pin-Pitch)

- Resolution: 12 Bits

- Conversion Rate: 170 MSPS

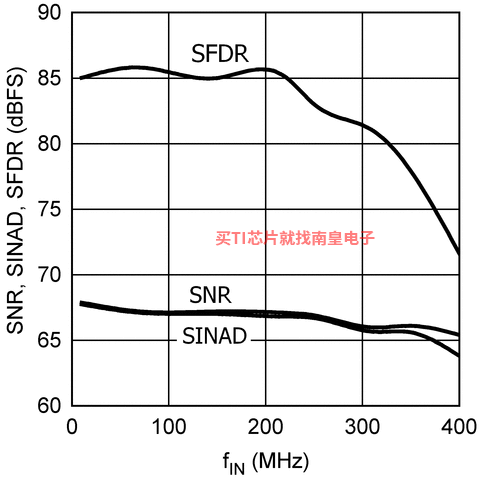

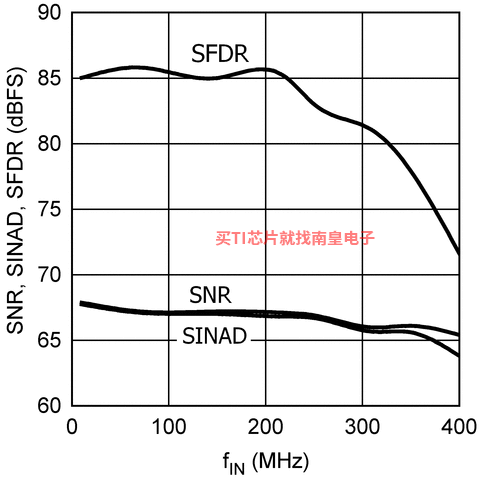

- SNR (fIN = 70 MHz): 67.2 dBFS (Typ)

- SFDR (fIN = 70 MHz): 85.8 dBFS (Typ)

- ENOB (fIN = 70 MHz): 10.9 Bits (Typ)

- Full Power Bandwidth: 1.1 GHZ (Typ)

- Power Consumption: 781 mW (Typ)

All trademarks are the property of their respective owners.

- Sample rate (Max) (MSPS)

- 170

- Resolution (Bits)

- 12

- Number of input channels

- 1

- Interface type

- DDR LVDS, Parallel LVDS

- Analog input BW (MHz)

- 1100

- Features

- Low Power

- Rating

- Catalog

- Input range (Vp-p)

- 2

- Power consumption (Typ) (mW)

- 781

- Architecture

- Pipeline

- SNR (dB)

- 67.9

- ENOB (Bits)

- 11

- SFDR (dB)

- 85.8

- Operating temperature range (C)

- -40 to 85

- Input buffer

- No

ADC12V170的完整型号有:ADC12V170CISQ/NOPB,以下是这些产品的关键参数及官网采购报价:

ADC12V170CISQ/NOPB,工作温度:-40 to 85,封装:WQFN (RHS)-48,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:SN,TI官网ADC12V170CISQ/NOPB的批量USD价格:33.541(1000+)

PSPICE-FOR-TI ― 适用于 TI 设计和模拟工具的 PSpice

PSpice for TI 可提供帮助评估模拟电路功能的设计和仿真环境。此功能齐全的设计和仿真套件使用 Cadence 的模拟分析引擎。PSpice for TI 可免费使用,包括业内超大的模型库之一,涵盖我们的模拟和电源产品系列以及精选的模拟行为模型。借助?PSpice for TI 的设计和仿真环境及其内置的模型库,您可对复杂的混合信号设计进行仿真。创建完整的终端设备设计和原型解决方案,然后再进行布局和制造,可缩短产品上市时间并降低开发成本。

在?PSpice for TI 设计和仿真工具中,您可以搜索 TI (...)