- ���쳧�̣�TI

- ��Ʒ�������ת����

- ������Ŀ��ģ��ת���� (ADC) - ����ģ��ת���� (>10MSPS)

- ����������14 λ 3GSPS ��Ƶ���������������ͷ������ɵ�·

- ������������ADC31RF80�ļ����ĵ�����

- TI�����������ṩ���շ������ϸ������������������Ŀ��۸�

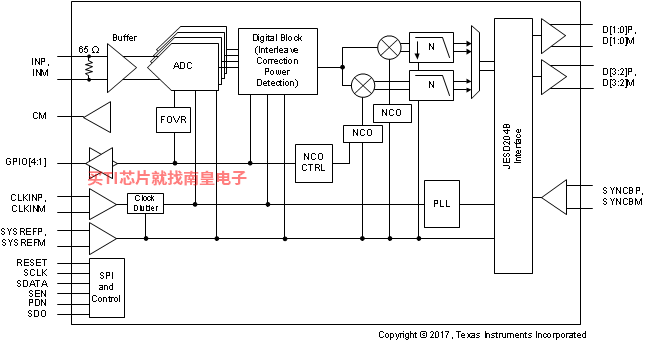

The ADC31RF80 device is a 14-bit, 3-GSPS, single-channel telecom receiver and feedback device that supports RF sampling with input frequencies up to 4 GHz and beyond. Designed for high signal-to-noise ratio (SNR), the ADC31RF80 delivers a noise spectral density of –155 dBFS/Hz as well as dynamic range over a large input frequency range. The buffered analog input with on-chip termination provides uniform input impedance across a wide frequency range and minimizes sample-and-hold glitch energy.

The ADC31RF80 comes with a dual-band, digital down-converter (DDC) with up to three independent, 16-bit numerically-controlled oscillators (NCOs) per DDC for phase-coherent frequency hopping. Additionally, the ADC is equipped with front-end peak and RMS power detectors and alarm functions to support external automatic gain control (AGC) algorithms.

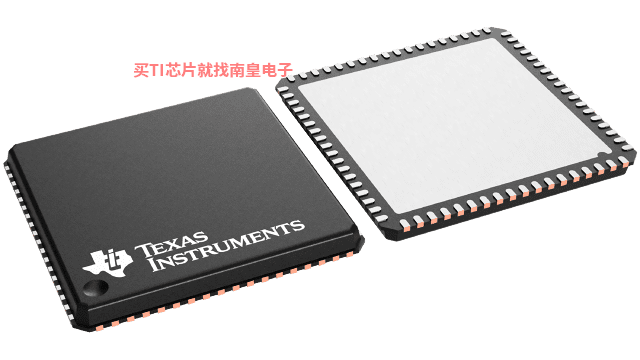

The ADC31RF80 supports the JESD204B serial interface with subclass 1-based deterministic latency using data rates up to 12.5 Gbps with up to four lanes. The device is offered in a 72-pin VQFN package (10 mm × 10 mm) and supports the industrial temperature range (–40°C to +85°C).

- 14-Bit, 3-GSPS ADC

- Noise Floor: �C155 dBFS/Hz

- RF Input Supports Up To 4.0 GHz

- Aperture Jitter: 90 fS

- Spectral Performance (fIN = 900 MHz, �C2 dBFS):

- SNR: 61.4 dBFS

- SFDR: 71-dBc HD2, HD3

- SFDR: 76-dBc Worst Spur

- Spectral Performance (fIN = 1.85 GHz, �C2 dBFS):

- SNR: 58.5 dBFS

- SFDR: 65-dBc HD2, HD3

- SFDR: 75-dBc Worst Spur

- On-Chip Digital Down-Converters:

- Up to 2 DDCs (Dual-Band Mode)

- Up to 3 Independent NCOs per DDC

- On-Chip Input Clamp for Overvoltage Protection

- Programmable On-Chip Power Detectors With Alarm Pins for AGC Support

- On-Chip Dither

- On-Chip Input Termination

- Input Full-Scale: 1.35 VPP

- Support for Multi-Chip Synchronization

- JESD204B Interface:

- Subclass 1-Based Deterministic Latency

- 4 Lanes Support at 12.5 Gbps

- Total Power Dissipation: 3.2 W at 3.0 GSPS

- 72-Pin VQFN Package (10 mm �� 10 mm)

- Sample rate (Max) (MSPS)

- 3000

- Resolution (Bits)

- 14

- Number of input channels

- 1

- Interface type

- JESD204B

- Analog input BW (MHz)

- 3200

- Features

- Ultra High Speed

- Rating

- Catalog

- Input range (Vp-p)

- 1.35

- Power consumption (Typ) (mW)

- 3200

- Architecture

- Pipeline

- SNR (dB)

- 61.4

- ENOB (Bits)

- 9.8

- SFDR (dB)

- 71

- Operating temperature range (C)

- -40 to 85

- Input buffer

- Yes

ADC31RF80�������ͺ��У�ADC31RF80IRMP��ADC31RF80IRMPT����������Щ��Ʒ�Ĺؼ������������ɹ����ۣ�

ADC31RF80IRMP�������¶ȣ�-40 to 85����װ��VQFN (RMP)-72����װ����MPQ��168����MSL �ȼ�/��������ֵ�¶ȣ�Level-3-260C-168 HR�����ŶƲ�/������ϣ�NIPDAU��TI����ADC31RF80IRMP������USD�۸�582.151��1000+��

ADC31RF80IRMPT�������¶ȣ�-40 to 85����װ��VQFN (RMP)-72����װ����MPQ��250����MSL �ȼ�/��������ֵ�¶ȣ�Level-3-260C-168 HR�����ŶƲ�/������ϣ�NIPDAU��TI����ADC31RF80IRMPT������USD�۸�582.151��1000+��

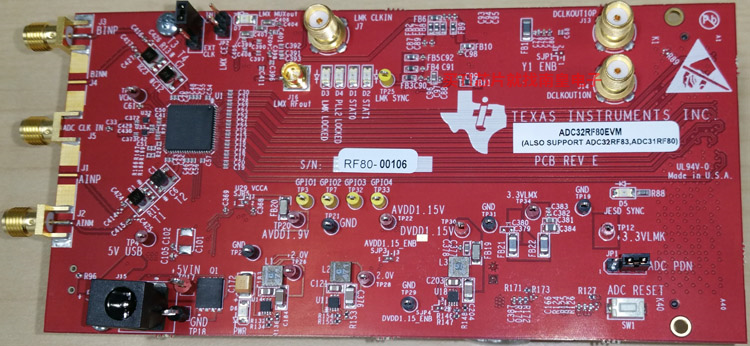

ADC32RF80EVM �� ������ ADC32RF80 ˫ͨ����14 λ��3GSPS����Ƶ��������������������ģ��

ADC32RF80 ����ģ�� (EVM) չʾ�˾��� JESD204B �ӿڵ�˫ͨ����3GSPS��14 λģ��ת���� (ADC) �����ܡ��� EVM ���� ADC32RF80 �������� LMK04828 �ṩ�� JESD204B ʱ�Ӻ������ṩ�����ѹ�� TI ��ѹ��ѹ������ ADC ÿ��ͨ��������Ĭ�����ӵ�һ����ѹ�������·���õ�·�����ӵ� 50Ω �����ź�Դ��

ʱ�ӻ�����ͨ����ѹ�������ṩ������ʱ�ӻ���������ӵ� 50Ω ����ʱ��Դ����ʹ�ð��� LMK04828 ���ɱ���� JESD204B ʱ�ӡ�

ͨ������ USB ���Ӻͻ��� Windows® �� GUI (...)

TI-JESD204-IP �� JESD204 ������� IP���������ӵ� TI ��������ת������ FPGA

JESD204 ������� IP ּ��Ϊ FPGA ����ʦ�ṩһ������ͨ�������е� JESD204 ϵͳ��·������ IP �����ر���ƣ��ɽ��������ִ���������Ӧ������ JESD204 Э��Ĵ�������ܺ�ʱ��ؼ����������ظ��뿪���� IP�����������Ա��ʡ�̼�����ʱ�䲢�� FPGA ���ɡ�JESD204 ������� IP ��ר���ѣ����� TI ��������ת�������ʹ�á�TI ��Э���û����ó�ʼ��·������·�ɶ��ƣ��Ա����ض� FPGA ƽ̨�� TI ����ת���� JMODE ֮��ʹ�á� �ڶԸ� IP ���в��Բ�ȷ����������ڲ�����֮��TI ����ͨ����ȫ�����������ṩ�� IP��

JESD204 (...)

ADC32RF45 IBIS Model

PSpice for TI ���ṩ��������ģ���·���ܵ���ƺͷ��滷�����˹�����ȫ����ƺͷ�����ʹ�� Cadence ��ģ��������档PSpice for TI �����ʹ�ã�����ҵ�ڳ����ģ�Ϳ�֮һ���������ǵ�ģ��͵�Դ��Ʒϵ���Լ���ѡ��ģ����Ϊģ�͡�����?PSpice for TI ����ƺͷ��滷���������õ�ģ�Ϳ⣬���ɶԸ��ӵĻ���ź���ƽ��з��档�����������ն��豸��ƺ�ԭ�ͽ��������Ȼ���ٽ��в��ֺ����죬�����̲�Ʒ����ʱ�䲢���Ϳ����ɱ���

��?PSpice for TI ��ƺͷ��湤���У����������� TI (...)

FREQ-DDC-FILTER-CALC �� ��Ƶ����Ƶ�ʹ滮����ģ���˲����� DDC Excel ������

�� Excel ������Ϊϵͳ�����Ա�ṩ��һ�ַ����������ڼ�ֱ����Ƶ��������������ƺ͵��Թ��̡����ṩ���ֹ��ܣ�Ƶ�ʹ滮��ģ���˲��ͳ�ȡ�˲�����ɢλ�á��ڸ���Σ�Ƶ�ʹ滮���߿��� ADC �����ʺ�����Ƶ��λ�ã��Ա��ڳ��������¼�ʱ�Ż�����ɢ��̬��Χ (SFDR)��һЩ��������������涼������ L ���ν���������������ʩ��վ��������������̶�Ƶ�Σ���ֻ�ṩ�����ʵ��š�

�ⲿ��Ƶ�˲�����Ӧ�ܴ�̶���ȡ����ϵͳ SFDR Ŀ��� ADC ������ SFDR ���ܣ�ģ���˲������߿�����ƽ��ṩ��ذ�����

��ϵͳ�����ڼ䣬������ٸ���Ҷ�任 (FFT) (...)