- 制造厂商:TI

- 产品类别:数据转换器

- 技术类目:模数转换器 (ADC) - 高速模数转换器 (>10MSPS)

- 功能描述:四通道、12 位、50MSPS 模数转换器 (ADC)

- 点击这里打开及下载ADC34J22的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

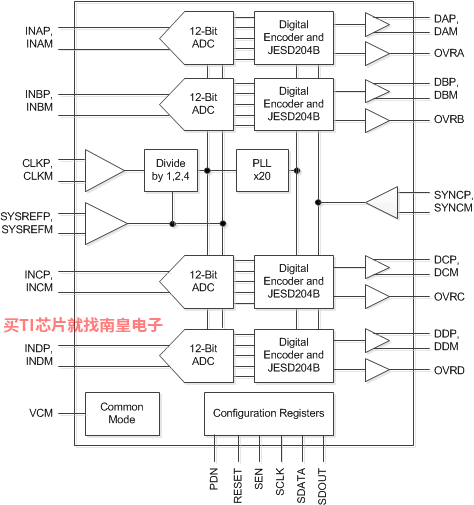

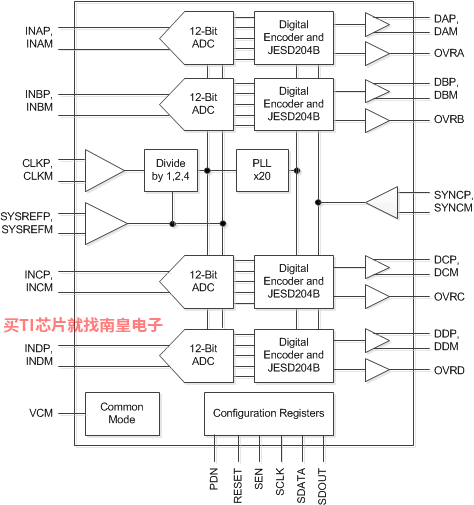

ADC34J2x 属于高线性度、超低功耗、双通道、12 位、50MSPS 至 160MSPS 模数转换器 (ADC) 系列。 此类器件专门设计用于支持具有宽动态范围需求且要求苛刻的高输入频率信号。 当 SYSREF 输入实现整个系统同步时,时钟输入分频器将给予系统时钟架构设计更高的灵活性。 该器件支持 JESD204B 接口,从而减少接口线路的数量,实现高系统集成度。 JESD204B 接口是串行接口,仅通过一个差分对即可串行输出每个 ADC 的数据。 内部锁相环 (PLL) 会将传入的 ADC 采样时钟乘以 20,以获得串行输出各通道的 12 位数据时所使用的位时钟。 该器件支持子类 1,接口速率高达 3.2Gbps。

- 四通道

- 12 位分辨率

- 1.8V 单电源

- 支持 1 分频,2 分频和 4 分频的灵活输入时钟缓冲器

- fIN = 70MHz 时,信噪比 (SNR) = 69.6dBFS,无杂散动态范围 (SFDR) = 86dBc

- 超低功耗:

- 160MSPS 时为每通道 203mW

- 通道隔离:105dB

- 内部抖动

- JESD204B 串口:

- 兼容子类 0、1、2,速率最高达 3.2Gbps

- 支持每个 ADC 一条通道(高达 160MSPS)

- 支持多芯片同步

- 与 14 位版本器件引脚到引脚兼容

- 封装:超薄四方扁平无引线 (VQFN)-48 (7mm x 7mm)

- 多载波、多模式蜂窝基站

- 雷达和智能天线阵列

- 炮弹制导

- 电机控制反馈

- 网络和矢量分析器

- 通信测试设备

- 无损检测

- 微波接收器

- 软件定义无线电 (SDR)

- 正交和分集无线电接收器

All trademarks are the property of their respective owners.

- Sample rate (Max) (MSPS)

- 50

- Resolution (Bits)

- 12

- Number of input channels

- 4

- Interface type

- JESD204B

- Analog input BW (MHz)

- 450

- Features

- Low Power

- Rating

- Catalog

- Input range (Vp-p)

- 2

- Power consumption (Typ) (mW)

- 491

- Architecture

- Pipeline

- SNR (dB)

- 70.5

- ENOB (Bits)

- 11.4

- SFDR (dB)

- 95

- Operating temperature range (C)

- -40 to 85

- Input buffer

- No

ADC34J22的完整型号有:ADC34J22IRGZR、ADC34J22IRGZT,以下是这些产品的关键参数及官网采购报价:

ADC34J22IRGZR,工作温度:-40 to 85,封装:VQFN (RGZ)-48,包装数量MPQ:2500个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:NIPDAUAG,TI官网ADC34J22IRGZR的批量USD价格:16.234(1000+)

ADC34J22IRGZT,工作温度:-40 to 85,封装:VQFN (RGZ)-48,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:NIPDAUAG,TI官网ADC34J22IRGZT的批量USD价格:18.234(1000+)

DEV-ADC34J22 — DEV-ADC34J22 评估模块

DEV-ADC34J22 是一款四通道 50MSPS ADC 模块,旨在与 Altera HSMC 标准接轨。DEV-ADC34J22 采用 TI 符合 JESD204B 标准的全新 ADC34J22 模数转换器 (ADC),结合使用 TI LMK04828 抖动清除器的时钟调节功能。它可通过 TI 的 THS4541 850MHz 带宽全差动放大器,在 2 个通道(共 4 个)中提供单端直流耦合输入。

该模块可提供 6 个前面板 SMA 连接器:1 个 EXT 触发器、1 个 EXT 时钟和 4 个模拟输入通道,同时提供一个用于单独时钟生成的板载 10MHz TCXO,其 100MHz (...)

发件人: Dallas Logic CorporationTI-JESD204-IP — JESD204 快速设计 IP,用于连接到 TI 高速数据转换器的 FPGA

JESD204 快速设计 IP 旨在为 FPGA 工程师提供一条快速通往运行中的 JESD204 系统的路径。该 IP 经过特别设计,可将下游数字处理和其他应用逻辑与 JESD204 协议的大多数性能和时序关键型限制因素隔离开。该 IP将帮助设计人员节省固件开发时间并简化 FPGA 集成。JESD204 快速设计 IP 免专利费,可与 TI 高速数据转换器配合使用。TI 将协助用户配置初始链路,该链路可定制,以便在特定 FPGA 平台和 TI 数据转换器 JMODE 之间使用。 在对该 IP 进行测试并确定其可以用于部署工作之后,TI 将会通过安全的下载链接提供该 IP。

JESD204 (...)

ADC34J45 IBIS Model

PSpice for TI 可提供帮助评估模拟电路功能的设计和仿真环境。此功能齐全的设计和仿真套件使用 Cadence 的模拟分析引擎。PSpice for TI 可免费使用,包括业内超大的模型库之一,涵盖我们的模拟和电源产品系列以及精选的模拟行为模型。借助?PSpice for TI 的设计和仿真环境及其内置的模型库,您可对复杂的混合信号设计进行仿真。创建完整的终端设备设计和原型解决方案,然后再进行布局和制造,可缩短产品上市时间并降低开发成本。

在?PSpice for TI 设计和仿真工具中,您可以搜索 TI (...)

TIDA-00294 — 适用于高速 ADC 的高性能单端转差分有源接口参考设计

此参考设计使用 ADC34J22 12b 50Msps JESD204B 数据转换器和 THS4541 全差分放大器来演示如何为高速 ADC 设计高性能有源接口。这种电路可用于传感器前端、电机控制以及测试和测量应用。这里介绍了电路模型和设计公式的推导以及 PCB 的实际实施。与无源交流耦合变压器接口相比,该实施的结果显示可提供非常相似的性能。 发件人: Dallas Logic Corporation