- 制造厂商:TI

- 产品类别:数据转换器

- 技术类目:模数转换器 (ADC) - 高速模数转换器 (>10MSPS)

- 功能描述:八通道、12 位、65MSPS 模数转换器 (ADC)

- 点击这里打开及下载ADS5282的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

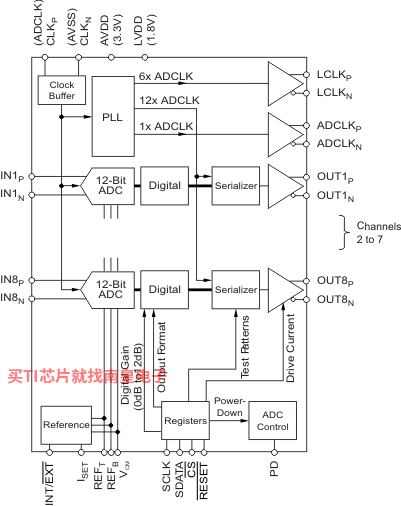

The ADS528x is a family of high-performance, low-power, octal channel analog-to-digital converters (ADCs). Available in either a 9mm × 9mm QFN package or an HTQFP-80 package, with serialized low-voltage differential signaling (LVDS) outputs and a wide variety of programmable features, the ADS528x is highly customizable for a diversity of applications and offers an unprecedented level of system integration. An application note, XAPP774 (available at www.xilinx.com), describes how to interface the serial LVDS outputs of TI&3146;s ADCs to Xilinx field-programmable gate arrays (FPGAs). The ADS528x family is specified over the industrial temperature range of –40°C to +85°C.

- Speed and Resolution Grades:

- ADS5281: 12-bit, 50MSPS

- ADS5282: 12-bit, 65MSPS

- Power Dissipation:

- 48mW/Channel at 30MSPS

- 55mW/Channel at 40MSPS

- 64mW/Channel at 50MSPS

- 77mW/Channel at 65MSPS

- 70dBFS SNR at 10MHz IF

- Analog Input Full-Scale Range: 2VPP

- Low-Frequency Noise Suppression Mode

- 6dB Overload Recovery In One Clock

- External and Internal (Trimmed) Reference

- 3.3V Analog Supply, 1.8V Digital Supply

- Single-Ended or Differential Clock:

- Clock Duty Cycle Correction Circuit (DCC)

- Programmable Digital Gain: 0dB to 12dB

- Serialized DDR LVDS Output

- Programmable LVDS Current Drive, Internal Termination

- Test Patterns for Enabling Output Capture

- Straight Offset Binary or Two’s Complement Output

- Package Options:

- 9mm × 9mm QFN-64

- HTQFP-80 PowerPAD Compatible with ADS527x Family

- Sample rate (Max) (MSPS)

- 65

- Resolution (Bits)

- 12

- Number of input channels

- 8

- Interface type

- Serial LVDS

- Analog input BW (MHz)

- 520

- Features

- Low Power

- Rating

- Catalog

- Input range (Vp-p)

- 2

- Power consumption (Typ) (mW)

- 616

- Architecture

- Pipeline

- SNR (dB)

- 70

- ENOB (Bits)

- 11.3

- SFDR (dB)

- 85

- Operating temperature range (C)

- -40 to 85

- Input buffer

- No

ADS5282的完整型号有:ADS5282IRGCR、ADS5282IRGCT,以下是这些产品的关键参数及官网采购报价:

ADS5282IRGCR,工作温度:-40 to 85,封装:VQFN (RGC)-64,包装数量MPQ:2000个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:NIPDAU,TI官网ADS5282IRGCR的批量USD价格:58.54(1000+)

ADS5282IRGCT,工作温度:-40 to 85,封装:VQFN (RGC)-64,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:NIPDAU,TI官网ADS5282IRGCT的批量USD价格:60.54(1000+)

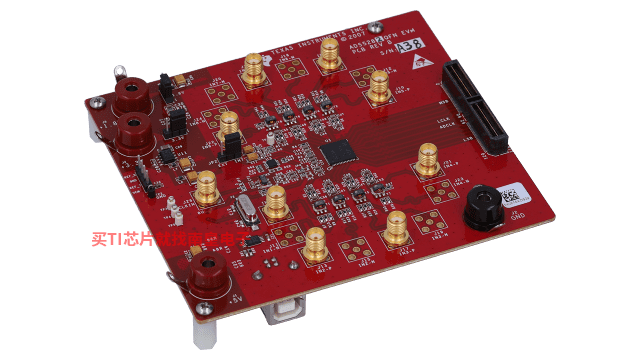

ADS5282EVM ― ADS5282 八通道 12 位 65MSPS 模数转换器评估模块

特别说明:希望评估 ADS528x 的客户应订购 ADS528xEVM、ADSDESER-50EVM 和 ADSDESER-50EVM 适配卡。

ADS5282EVM 提供一个平台,用于在各种信号、基准和电源条件下对八通道 ADS5282 模数转换器 (ADC) 进行评估。

该 EVM 提供了一个外部 SMA 连接器,用于连接 ADC 的八个模拟输入和 ADC 时钟的输入。可使用单端或差分时钟为 ADC 提供计时,EVM 上的配置允许用户使用单端 PECL 时钟或差分变压器耦合时钟来评估 ADC。

EVM 通过高速、高密度 Samtec 输出接头提供数字输出。数字输出连接器直接连接到 (...)

HSADC-SPI-UTILITY ― 高速 ADC SPI 编程工具

此高速数据转换器专业 GUI 是一款 PC 程序(兼容 Windows XP/7/10),旨在帮助评估大多数 TI 高速数据转换器和模拟前端 (AFE) 平台。DATACONVERTERPRO-SW 支持整个 TSW14xxx 系列的数据采集和模式生成卡,为分析时域和频域中的数据转换器提供了快速强大的解决方案以及单音调、多音调和调制信号支持。此 GUI 还兼容用于快速合成单音调、多音调和调制信号的 TI 模式生成 GUI。用户可以为 DATACONVERTERPRO-SW 提供定制模式,以加载到 TI 数模转换器 (DAC)。支持从模数转换器 (ADC) 采集内导出 CSV (...)

ADS5281/82/87 IBIS Model

PSpice for TI 可提供帮助评估模拟电路功能的设计和仿真环境。此功能齐全的设计和仿真套件使用 Cadence 的模拟分析引擎。PSpice for TI 可免费使用,包括业内超大的模型库之一,涵盖我们的模拟和电源产品系列以及精选的模拟行为模型。借助?PSpice for TI 的设计和仿真环境及其内置的模型库,您可对复杂的混合信号设计进行仿真。创建完整的终端设备设计和原型解决方案,然后再进行布局和制造,可缩短产品上市时间并降低开发成本。

在?PSpice for TI 设计和仿真工具中,您可以搜索 TI (...)

ADC-HARMONIC-CALC ― 模数转换器 (ADC) 谐波计算器

ADC 谐波计算工具是基于 excel 的计算器,用于确定当模数转换器中出现奈奎斯特混叠后高次谐波的频率空间的位置。

如果给定 ADC 采样速率和有用信号的范围,该计算器可以确定第 2 至第 9 谐波是否会返送到有用信号的频带中。图表以图形方式显示了在出现奈奎斯特混叠后基本信号以及第 2 至第 9 谐波的位置。

JITTER-SNR-CALC ― 用于 ADC 的抖动和 SNR 计算器

JITTER-SNR-CALC 可用于根据输入频率和时钟抖动来计算 ADC 的理论信噪比 (SNR) 性能。TIDA-00078 ― 具有 I/Q 校正的直接降压转换系统

TSW6011EVM 的现场可编程门阵列 (FPGA) 中实施的 I/Q 校正块可帮助用户在无线系统中采用直接降压转换接收器架构。I/Q 校正块包含一个单头盲算法,该算法可以校正零中频接收器系统中与频率无关的 I/Q 不平衡。除了 I/Q 校正块,FPGA 还包括一个数字增益块、一个数字功率测量块、两个内插块、一个 I/Q 偏移校正块和一个正交混频块。