- 制造厂商:TI

- 产品类别:数据转换器

- 技术类目:模数转换器 (ADC) - 高速模数转换器 (>10MSPS)

- 功能描述:双通道、12 位、105MSPS 模数转换器 (ADC)

- 点击这里打开及下载ADS62P24的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

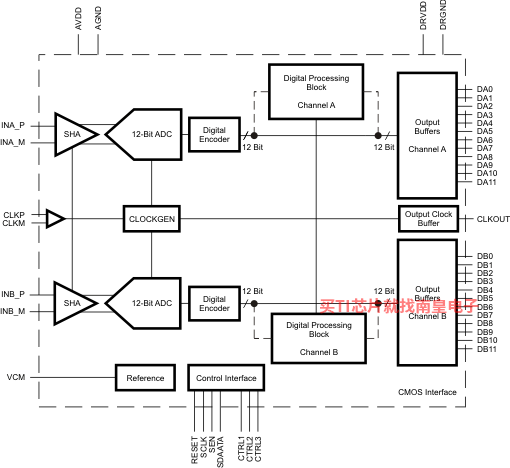

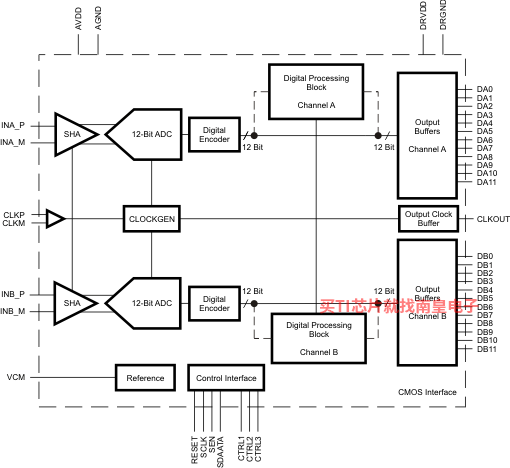

ADS62P2X is a dual channel 12-bit A/D converter family with maximum sample rates up to 125 MSPS. It combines high performance and low power consumption in a compact 64 QFN package. Using an internal sample and hold and low jitter clock buffer, the ADC supports high SNR and high SFDR at high input frequencies. It has coarse and fine gain options that can be used to improve SFDR performance at lower full-scale input ranges.

ADS62P2X includes a digital processing block that consists of several useful and commonly used digital functions such as ADC offset correction, fine gain correction (in steps of 0.05 dB), decimation by 2,4,8 and in-built and custom programmable filters. By default, the digital processing block is bypassed, and its functions are disabled.

Two output interface options exist – parallel CMOS and DDR LVDS (Double Data Rate). ADS62P2X includes internal references while traditional reference pins and associated decoupling capacitors have been eliminated. Nevertheless, the device can also be driven with an external reference. The device is specified over the industrial temperature range (–40°C to 85°C).

- Maximum Sample Rate: 125 MSPS

- 12-Bit Resolution with No Missing Codes

- 95 dB Crosstalk

- Parallel CMOS and DDR LVDS Output Options

- 3.5 dB Coarse Gain and Programmable Fine Gain up to 6 dB for SNR/SFDR Trade-Off

- Digital Processing Block with:

- Offset Correction

- Fine Gain Correction, in Steps of 0.05 dB

- Decimation by 2/4/8

- Built-in and Custom Programmable 24-Tap Low-/High-/Band-Pass Filters

- Supports Sine, LVPECL, LVDS, and LVCMOS Clocks and Amplitude Down to 400 mVPP

- Clock Duty Cycle Stabilizer

- Internal Reference; Supports External Reference also

- 64-QFN Package (9mm × 9mm)

- Pin Compatible 14-Bit Family (ADS62P4X)

- Sample rate (Max) (MSPS)

- 105

- Resolution (Bits)

- 12

- Number of input channels

- 2

- Interface type

- DDR LVDS, Parallel CMOS

- Analog input BW (MHz)

- 450

- Features

- High Performance

- Rating

- Catalog

- Input range (Vp-p)

- 2

- Power consumption (Typ) (mW)

- 700

- Architecture

- Pipeline

- SNR (dB)

- 71.5

- ENOB (Bits)

- 11.5

- SFDR (dB)

- 92

- Operating temperature range (C)

- -40 to 85

- Input buffer

- No

ADS62P24的完整型号有:ADS62P24IRGCR、ADS62P24IRGCT,以下是这些产品的关键参数及官网采购报价:

ADS62P24IRGCR,工作温度:-40 to 85,封装:VQFN (RGC)-64,包装数量MPQ:2000个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:NIPDAU,TI官网ADS62P24IRGCR的批量USD价格:33.648(1000+)

ADS62P24IRGCT,工作温度:-40 to 85,封装:VQFN (RGC)-64,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:NIPDAU,TI官网ADS62P24IRGCT的批量USD价格:35.648(1000+)

ADS62P24EVM ― ADS62P24 评估模块

ADS62P24 EVM 是能让设计者评估德州仪器 (TI) ADS62P24 器件(双通道 12 位 105MSPS 模数转换器)的电路板。ADC 具有用户可选的并行 CMOS 或 DDR LVDS 输出。用户可以使用 TSW1100(CMOS 模式)或 TSW1200EVM(DDR LVDS 模式)从转换器采集数据。EVM 提供了可在各种时钟、输入和电源条件下测试 ADS62P24 的灵活环境。

评估板还能让设计者在 ADC 中使用变压器耦合输入或基于德州仪器 (TI) THS4509 的放大器输入。由于 ADC EVM 提供 THS4509,用户可以轻松评估所有与封装兼容的 ADC (...)

HSADC-SPI-UTILITY ― 高速 ADC SPI 编程工具

此高速数据转换器专业 GUI 是一款 PC 程序(兼容 Windows XP/7/10),旨在帮助评估大多数 TI 高速数据转换器和模拟前端 (AFE) 平台。DATACONVERTERPRO-SW 支持整个 TSW14xxx 系列的数据采集和模式生成卡,为分析时域和频域中的数据转换器提供了快速强大的解决方案以及单音调、多音调和调制信号支持。此 GUI 还兼容用于快速合成单音调、多音调和调制信号的 TI 模式生成 GUI。用户可以为 DATACONVERTERPRO-SW 提供定制模式,以加载到 TI 数模转换器 (DAC)。支持从模数转换器 (ADC) 采集内导出 CSV (...)

ADS62Pxx Family TINA-TI Transient Spice Model

PSpice for TI 可提供帮助评估模拟电路功能的设计和仿真环境。此功能齐全的设计和仿真套件使用 Cadence 的模拟分析引擎。PSpice for TI 可免费使用,包括业内超大的模型库之一,涵盖我们的模拟和电源产品系列以及精选的模拟行为模型。借助?PSpice for TI 的设计和仿真环境及其内置的模型库,您可对复杂的混合信号设计进行仿真。创建完整的终端设备设计和原型解决方案,然后再进行布局和制造,可缩短产品上市时间并降低开发成本。

在?PSpice for TI 设计和仿真工具中,您可以搜索 TI (...)

ADC-HARMONIC-CALC ― 模数转换器 (ADC) 谐波计算器

ADC 谐波计算工具是基于 excel 的计算器,用于确定当模数转换器中出现奈奎斯特混叠后高次谐波的频率空间的位置。

如果给定 ADC 采样速率和有用信号的范围,该计算器可以确定第 2 至第 9 谐波是否会返送到有用信号的频带中。图表以图形方式显示了在出现奈奎斯特混叠后基本信号以及第 2 至第 9 谐波的位置。