- 制造厂商:TI

- 产品类别:射频与微波

- 技术类目:宽带收发器、接收器、发射器 - 射频采样收发器

- 功能描述:具有无旁路模式 14 位 9GSPS DAC 和 3GSPS ADC 的四通道射频采样 AFE

- 点击这里打开及下载AFE7444的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

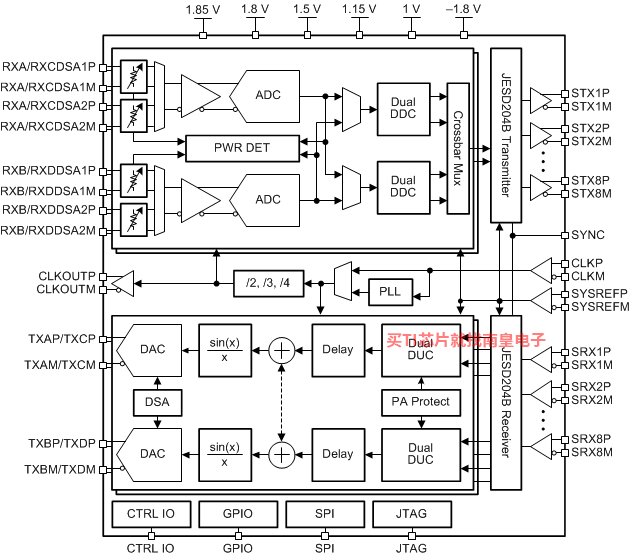

AFE7444 是具有 14 位 9GSPS DAC 和 14 位 3GSPS ADC 的四路通道宽频带射频采样模拟前端 (AFE)。可在高达 6GHz 的射频下工作,此器件支持直接射频采样到 C 频带,无需其他频率转换阶段。密度和灵活性的改进实现了对高通道数、多任务系统的支持。

DAC 信号路径支持插值和数字上变频选项,提供高达 800MHz 信号带宽。差动输出路径包括支持输出功率调优的数字步进衰减器 (DSA)。

每个 ADC 输入路径包括一个双通道 DSA 和射频数字功率检测器。灵活的抽取选项提供数据带宽优化。

8 通道 (8 TX + 8 RX) 子类 1 兼容性 JESD204B 接口运行速度高达 15Gbps。可旁路片上 PLL 通过可选时钟输出简化时钟运行。

- 四通道、14 位 9GSPS DAC

- 信号带宽高达 800MHz

- 每通道 1个 DSA 调节输出功率

- 四通道、14 位 3GSPS ADC

- 信号带宽高达 800MHz

- NSD:–151dBFS/Hz

- fIN = 2.6GHz、–3dBFS 时的交流性能

- SNR:55dBFS

- SFDR:73dBc HD2 和 HD3

- SFDR:91dBc(最严重毛刺)

- 每通道 2 个 DSA 扩展动态范围

- 射频和数字功率检测器

- 射频频率范围:10MHz 至 6GHz

- 快速跳频 < 1μs

- 接收数字信号路径:

- 每个 ADC 连接双通道 DDC

- 每个 DDC 有 3 个相位同调 32 位 NCO

- 抽取率:3 倍至 32 倍

- 发送数字信号路径:

- 每个带有 32 位 NCO 的 DAC 连接双通道 DUC

- 插值率:8 倍至 36 倍

- Sin(x)/x 校正和可配置延迟

- 功率放大器保护 (PAP)

- JESD204B 接口:

- 8 个高达 15Gbps 的收发器

- 子类 1 多芯片同步

- 时钟:

- 具有旁路选项的内部 PLL 和 VCO

- 利用时钟分频器产生最高为 3GHz 的时钟输出

- DAC 功耗:9GSPS 时为 1.7W/ch

- ADC 功耗:3GSPS 时为 1.8W/ch

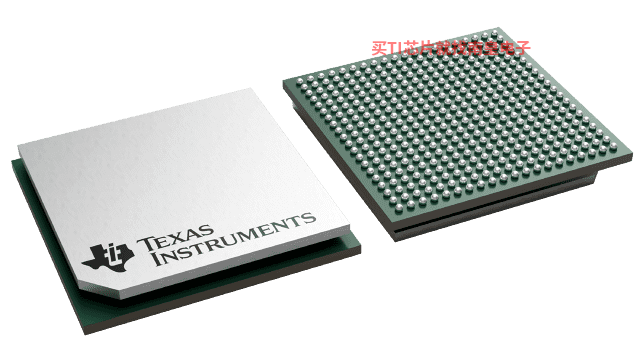

- 封装:17mm x 17mm FC BGA,0.8mm 间距

- Applications

- General Purpose

- # of TX/RX

- 4T4R

- # of DUCs/TX

- 2

- # of DDCs/RX

- 2

- Data rate (MSPS)

- 750

- RF frequency (Max) (MHz)

- 6000

- RF frequency (Min) (MHz)

- 10

- Operating temperature range (C)

- -40 to 85

- Rating

- Catalog

AFE7444的完整型号有:AFE7444IABJ、AFE7444IALK,以下是这些产品的关键参数及官网采购报价:

AFE7444IABJ,工作温度:-40 to 85,封装:FCBGA (ABJ)-400,包装数量MPQ:90个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:SNAGCU,TI官网AFE7444IABJ的批量USD价格:1693.903(1000+)

AFE7444IALK,工作温度:-40 to 85,封装:FCBGA (ALK)-400,包装数量MPQ:90个,MSL 等级/回流焊峰值温度:Level-3-220C-168 HR,引脚镀层/焊球材料:SNPB,TI官网AFE7444IALK的批量USD价格:2093.903(1000+)

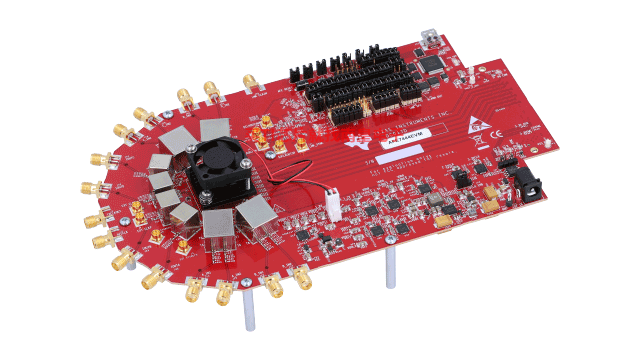

AFE7444EVM — 具有 14 位 9GSPS DAC 和 3GSPS ADC 的 AFE7444 四通道射频采样 AFE 评估模块

AFE7444 评估模块 (EVM) 是一个射频采样收发器平台,经配置后可同时支持最多四个发射和四个接收 (4T4R) 通道。 此模块可评估AFE7444器件,这是一款四通道、射频采样模拟前端 (AFE),具有 14 位 9GSPS 数模转换器 (DAC)、14 位 3GSPS 模数转换器 (ADC) 以及为 DAC 和 ADC 生成高频时钟的片上集成 PLL/VCO。

AFE7444EVM 可在每个通道使用双频带数字升压转换器和降压转换器,从而同时将具有高动态范围的多个宽带信号合成并实现数字化。接收通道支持片上集成数字步进衰减器(DSA),发射通道支持与 DSA (...)

TI-JESD204-IP — JESD204 快速设计 IP,用于连接到 TI 高速数据转换器的 FPGA

JESD204 快速设计 IP 旨在为 FPGA 工程师提供一条快速通往运行中的 JESD204 系统的路径。该 IP 经过特别设计,可将下游数字处理和其他应用逻辑与 JESD204 协议的大多数性能和时序关键型限制因素隔离开。该 IP将帮助设计人员节省固件开发时间并简化 FPGA 集成。JESD204 快速设计 IP 免专利费,可与 TI 高速数据转换器配合使用。TI 将协助用户配置初始链路,该链路可定制,以便在特定 FPGA 平台和 TI 数据转换器 JMODE 之间使用。 在对该 IP 进行测试并确定其可以用于部署工作之后,TI 将会通过安全的下载链接提供该 IP。

JESD204 (...)

FREQ-DDC-FILTER-CALC — 射频采样频率规划器、模拟滤波器和 DDC Excel 计算器

此 Excel 计算器为系统设计人员提供了一种方法,可用于简化直接射频采样接收器的设计和调试过程。它提供三种功能:频率规划、模拟滤波和抽取滤波器杂散位置。在概念阶段,频率规划工具可微调 ADC 采样率和输入频率位置,以便在出现阻塞事件时优化无杂散动态范围 (SFDR)。一些设计在这两个方面都很灵活;而 L 波段接收器或无线基础设施基站等其他设计则处理固定频段,且只提供采样率调优。

外部射频滤波器响应很大程度上取决于系统 SFDR 目标和 ADC 本身的 SFDR 性能;模拟滤波器工具可在设计阶段提供相关帮助。

在系统启动期间,如果快速傅里叶变换 (FFT) (...)

TIDA-010132 — 适用于雷达和电子战应用的多通道射频收发器参考设计

该参考设计展示了一款 8 通道模拟前端 (AFE),它使用了两个 AFE7444 4 通道射频收发器和基于 LMK04828-LMX2594 的时钟子系统,该子系统可支持将设计扩展至 16 通道或更多通道。每个 AFE 通道都包含 14 位 9GSPS DAC 和 3GSPS ADC,该 ADC 可在 2.6GHz 下同步至低于 10ps 偏移并且动态范围大于 75dB。TIDA-010131 — 适用于雷达和无线 5G 测试仪的多通道射频收发器时钟参考设计

相控阵雷达、无线通信测试仪和电子战等高速终端设备的模拟前端需要同步的多收发器信号链。每个收发器信号链都包括高速模数转换器 (ADC)、数模转换器 (DAC) 和时钟子系统。时钟子系统提供低噪声采样时钟,具备精细的延迟调节功能,可实现最低的通道间偏差和最佳的系统性能,如信噪比 (SNR)、无杂散动态范围 (SFDR)、IMD3 和有效位数 (ENOB) 等。此参考设计通过 AFE7444 EVM 展示了多通道 JESD204B 时钟生成和系统性能。通过高达 2.6GHz 射频的 6GSPS/3GSPS DAC/ADC 时钟实现的优于 10ps 的通道间偏差以及 SNR 和 SFDR (...)