- 制造厂商:TI

- 产品类别:逻辑和电压转换

- 技术类目:触发器、锁存器和寄存器 - 计数器

- 功能描述:CMOS 8 级可预置 8 位二进制同步递减计数器

- 点击这里打开及下载CD40103B的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

CD40102B, and CD40103B consist of an 8-stage synchronous down counter with a single output which is active when the internal count is zero. The CD40102B is configured as two cascaded 4-bit BCD counters, and the CD40103B contains a single 8-bit binary counter. Each type has control inputs for enabling or disabling the clock, for clearing the counter to its maximum count, and for presetting the counter either synchronously or asynchronously. All control inputs and the CARRY-OUT/ZERO-DEFECT output are active-low logic.

In normal operation, the counter is decremented by one count on each positive transition of the CLOCK. Counting is inhibited when the CARRY-IN/COUNTER ENABLE (CI/CE)\ input is high. The CARRY-OUT/ZERO-DEFECT (CO/ZD)\ output goes low when the count reaches zero if the CI/CE\ input is low, and remains low for one full clock period.

When the SYNCHRONOUS PRESET-ENABLE (SPE)\ input is low, data at the JAM input is clocked input the counter on the next positive clock transition regardless of the state of the CI/CE\ input. When the ASYNCHRONOUS PRESET-ENABLE (APE)\ input is low, data at the JAM inputs is asynchronously forced into the counter regardless of the state of the SPE\, CI/CE\, or CLOCK inputs. JAM inputs JO-J7 represent two 4-bit BCD words for the CD40102B and a single 8-bit binary word for the CD40103B. When the CLEAR (CLR)\ input is low, the counter is asynchronously cleared to its maximum count (9910 for the CD40102B and 25510 for the CD40103B) regardless of the state of any other input. The precedence relationship between control inputs is indicated in the truth table.

If all control inputs except CI/CE\ are high at the time of zero count, the counters will jump to the maximum count, giving a counting sequence of 100 or 256 clock pulses long.

This causes the CO/ZD\ output to go low to enable the clock on each succeeding clock pulse.

The CD40102B and CD40103B may be cascaded using the CI/CE\ input and CO/ZD\ output, in either a synchronous or ripple mode as shown in Figs. 21 and 22.

The CD40102B and CD40103B types are supplied in 16-lead dual-in-line plastic packages (E suffix), 16-lead small-outline packages (NSR suffix), and 16-lead thin shrink small-outline packages (PW and PWR suffixes). The CD40103B types also are supplied in 16-lead hermetic dual-in-line ceramic packages (F3A suffix).

- Synchronous or asynchronous preset

- Medium-speed operation: fCL = 3.6 MHz (typ.) @ VDD = 10V

- Cascadable

- 100% tested for quiescent current at 20 V

- Maximum input current of 1 μA at 18 V over full package-temperature range; 100 nA at 18 V and 25°C

- Noise margin (full package-temperature range) = 1 V at VDD = 5 V 2 V at VDD = 10 V 2.5 V at VDD = 15 V

- Standardized, symmetrical output characteristics

- 5-V, 10-V, and 15-V parametric ratings

- Meets all requirements of JEDEC Tentative Standard No. 13B, "Standard Specifications for Description of ’B’ Series CMOS Devices"

- Applications:

- Divide-by-"N" counters

- Programmable timers

- Interrupt timers

- Cycle/program counter

CD40102B - 2-Decade BCD Type CD40103B - 8-Bit Binary Type

- Function

- Counter

- Bits (#)

- 8

- Technology Family

- CD4000

- Supply voltage (Min) (V)

- 3

- Supply voltage (Max) (V)

- 18

- Input type

- Standard CMOS

- Output type

- Push-Pull

- Features

- Balanced outputs, Standard speed (tpd > 50ns), Positive input clamp diode, Presettable

CD40103B的完整型号有:CD40103BE、CD40103BNSR、CD40103BPW,以下是这些产品的关键参数及官网采购报价:

CD40103BE,工作温度:-55 to 125,封装:PDIP (N)-16,包装数量MPQ:25个,MSL 等级/回流焊峰值温度:N/A for Pkg Type,引脚镀层/焊球材料:NIPDAU,TI官网CD40103BE的批量USD价格:.481(1000+)

CD40103BNSR,工作温度:-55 to 125,封装:SO (NS)-16,包装数量MPQ:2000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网CD40103BNSR的批量USD价格:.462(1000+)

CD40103BPW,工作温度:-55 to 125,封装:TSSOP (PW)-16,包装数量MPQ:90个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网CD40103BPW的批量USD价格:.424(1000+)

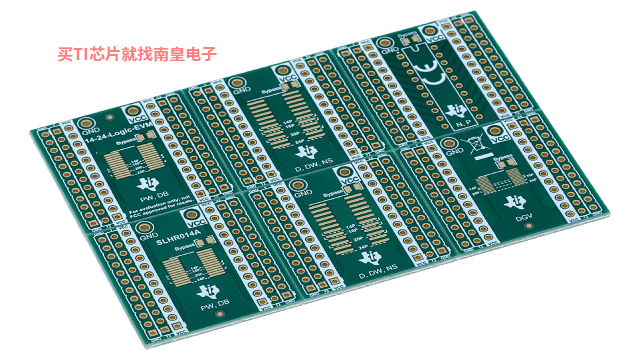

14-24-LOGIC-EVM ― 支持 14 到 24 引脚 PW、DB、D、DW、NS、DYY 和 DGV 封装的通用逻辑 EVM

该 EVM 设计用于支持采用 14 至 24 引脚 D、DW、DB、NS、PW、DYY 或 DGV 封装的任何逻辑器件。