- ���쳧�̣�TI

- ��Ʒ������͵�ѹת��

- ������Ŀ�����������������ͼĴ��� - ������

- ����������CMOS ��Ԥ�ü�/��������

- ������������CD4029B�ļ����ĵ�����

- TI�����������ṩ���շ������ϸ������������������Ŀ��۸�

CD4029B consists of a four-stage binary or BCD-decade up/down counter with provisions for look-ahead carry in both counting modes. The inputs consist of a single CLOCK, CARRY-IN\ (CLOCK ENABLE\), BINARY/DECADE, UP/DOWN, PRESET ENABLE, and four individual JAN signals, Q1, Q2, Q3, Q4 and a CARRY OUT\ signal are provided as outputs.

A high PRESET ENABLE signal allows information on the JAM INPUTS to preset the counter to any state asynchronously with the clock. A low on each JAM line, when the PRESET-ENABLE signal is high, resets the counter to its zero count. The counter is advanced one count at the positive transition of the clock when the CARRY-IN\ and PRESET ENALBE signals are low. Advancement is inhibited when the CARRY-IN\ or PRESET ENABLE signals are high. The CARRY-OUT\ signal is normally high and goes low when the counter reaches its maximum count in the UP mode or the minimum count in the DOWN mode provided the CARRY-IN\ signal is low. The CARRY-IN\ signal in the low state can thus be considered a CLOCK ENABLE\. The CARRY-IN\ terminal must be connected to VSS when not in use.

Binary counting is accomplished when the BINARY/DECADE input is high; the counter counts in the decade mode when the BINARY/DECADE input is low. The counter counts up when the UP/DOWN input is high, and down when the UP/DOWN input is low. Multiple packages can be connected in either a parallel-clocking or a ripple-clocking arrangement as shown in Fig. 17.

Parallel clocking provides synchronous control and hence faster response from all counting outputs. Ripple-clocking allows for longer clock input rise and fall times.

The CD4029B-series types are supplied in 16-lead hermetic dual-in-line ceramic packages (F3A suffix), 16-lead dual-in-line plastic packages (E suffix), 16-lead small-outline packages (M, M96, MT and NSR suffixes), and 16-lead thin shrink small-outline packages (PW and PWR suffixes).

- Medium-speed operation�� 8 MHz (typ.) @ CL = 50 pF and VDD�CVSS = 10 V

- Multi-package parallel clocking for synchronous high speed output response or ripple clocking for slow clock input rise and fall times

- "Preset Enable" and individual "Jam" inputs provided

- Binary or decade up/down counting

- BCD outputs in decade mode

- 100% tested for quiescent current at 20 V

- 5-V, 10-V, and 15-V parametric ratings

- Standardized, symmetrical output characteristics

- Maximum input current of 1 ��A at 18 V over full package-temperature range; 100 nA at 18 V and 25��C

- Noise margin (full package-temperature range) = 1 V at VDD = 5 V 2 V at VDD = 10 V 2.5 V at VDD = 15 V

- Meets all requirements of JEDEC Tentative Standard No. 13B, "Standard Specifications for Description of ��B�� Series CMOS Devices"

- Applications:

- Programmable binary and decade counting/frequency synthesizers-BCD output

- Analog to digital and digital to analog conversion

- Up/Down binary counting

- Magnitude and sign generation

- Up/Down decade counting

- Difference counting

- Function

- Counter

- Bits (#)

- 4

- Technology Family

- CD4000

- Supply voltage (Min) (V)

- 3

- Supply voltage (Max) (V)

- 18

- Input type

- Standard CMOS

- Output type

- Push-Pull

- Features

- Balanced outputs, Standard speed (tpd > 50ns), Positive input clamp diode, Presettable

CD4029B�������ͺ��У�CD4029BE��CD4029BM��CD4029BM96��CD4029BNSR��CD4029BPWR����������Щ��Ʒ�Ĺؼ������������ɹ����ۣ�

CD4029BE�������¶ȣ�-55 to 125����װ��PDIP (N)-16����װ����MPQ��25����MSL �ȼ�/��������ֵ�¶ȣ�N/A for Pkg Type�����ŶƲ�/������ϣ�NIPDAU��TI����CD4029BE������USD�۸�.146��1000+��

CD4029BM�������¶ȣ�-55 to 125����װ��SOIC (D)-16����װ����MPQ��40����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�NIPDAU��TI����CD4029BM������USD�۸�.311��1000+��

CD4029BM96�������¶ȣ�-55 to 125����װ��SOIC (D)-16����װ����MPQ��2500����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�NIPDAU��TI����CD4029BM96������USD�۸�.111��1000+��

CD4029BNSR�������¶ȣ�-55 to 125����װ��SO (NS)-16����װ����MPQ��2000����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�NIPDAU��TI����CD4029BNSR������USD�۸�.131��1000+��

CD4029BPWR�������¶ȣ�-55 to 125����װ��TSSOP (PW)-16����װ����MPQ��2000����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�NIPDAU��TI����CD4029BPWR������USD�۸�.111��1000+��

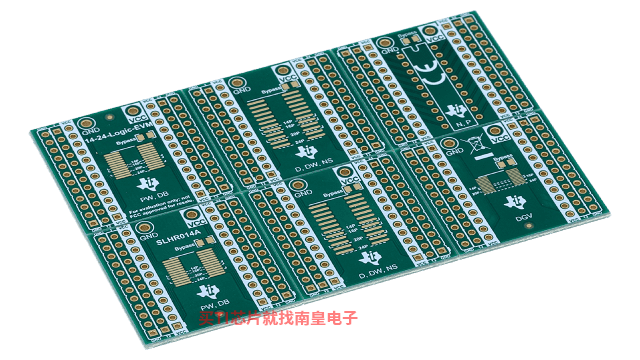

14-24-LOGIC-EVM �� ֧�� 14 �� 24 ���� PW��DB��D��DW��NS��DYY �� DGV ��װ��ͨ���� EVM

�� EVM �������֧�ֲ��� 14 �� 24 ���� D��DW��DB��NS��PW��DYY �� DGV ��װ���κ���������