- 制造厂商:TI

- 产品类别:逻辑和电压转换

- 技术类目:触发器、锁存器和寄存器 - 计数器

- 功能描述:CMOS 可预置 BCD 加/减计数器

- 点击这里打开及下载CD4510B的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

CD4510B Presettable BCD Up/Down Counter and the CD4516 Presettable Binary Up/Down Counter consist of four synchronously clocked D-type flip-flops (with a gating structure to provide T-type flip-flop capability) connected as counters. These counters can be cleared by a high level on the RESET line, and can be preset to any binary number present on the jam inputs by a high level on the PRESET ENABLE line. The CD4510B will count out of non-BCD counter states in a maximum of two clock pulses in the up mode, and a maximum of four clock pulses in the down mode.

If the CARRY-IN input is held low, the counter advances up or down on each positive-going clock transition. Synchronous cascading is accomplished by connecting all clock inputs in parallel and connecting the CARRY-OUT of a less significant stage to the CARRY-IN of a more significant stage.

The CD4510B and CD4516B can be cascaded in the ripple mode by connecting the CARRY-OUT to the clock of the next stage. If the UP/DOWN input changes during a terminal count, the CARRY-OUT must be gated with the clock, and the UP/DOWN input must change while the clock is high. This method provides a clean clock signal to the subsequent counting stage. (See Fig.15).

These devices are similar to types MC14510 and MC14516.

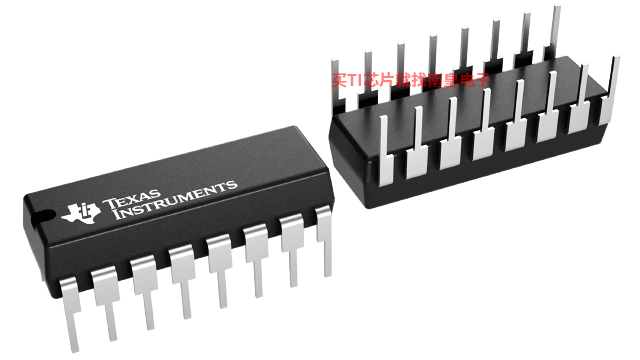

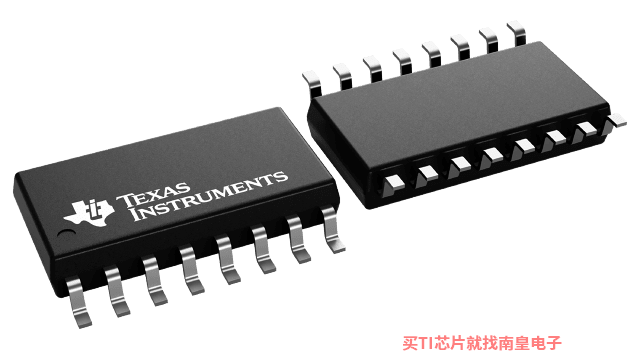

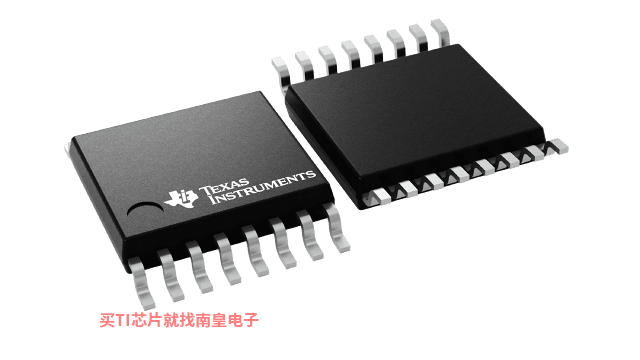

The CD4510B and CD4516B types are supplied in 16-lead dual-in-line plastic packages (E suffix), 16-lead small-outline packages (NSR suffix), and 16-lead thin shrink small-outline packages (PW and PWR suffixes). The CD4516B types also are supplied in 16-lead hermetic dual-in-line ceramic packages (F3A suffix).

- Medium-speed operation - fCL = 8 NHz typ. at 10 V

- Synchronous internal carry propagation

- Reset and Preset capability

- 100% tested for quiescent current at 20 V

- 5-V, 10-V, and 15-V parametric ratings

- Standardized, symmetrical output characteristics

- Maximum input current of 1 μA at 18 V over full package-temperature range; 100 nA at 18 V and 25°C

- Noise margin (full package-temperature range) = 1 V at VDD = 5 V 2 V at VDD = 10 V 2.5 V at VDD = 15 V

- Meets all requirements of JEDEC Tentative Standard No. 13B, "Standard Specifications for Description of ’B’ Series CMOS Devices"

- Applications:

- Up/Down difference counting

- Multistage synchronous counting

- Multistage ripple counting

- Synchronous frequency dividers

CD4510B ---BCD Type CD4516B ---Binary Type

- Function

- Counter

- Bits (#)

- 4

- Technology Family

- CD4000

- Supply voltage (Min) (V)

- 3

- Supply voltage (Max) (V)

- 18

- Input type

- Standard CMOS

- Output type

- Push-Pull

- Features

- Balanced outputs, Standard speed (tpd > 50ns), Positive input clamp diode, Presettable

CD4510B的完整型号有:CD4510BE、CD4510BNSR、CD4510BPWR,以下是这些产品的关键参数及官网采购报价:

CD4510BE,工作温度:-55 to 125,封装:PDIP (N)-16,包装数量MPQ:25个,MSL 等级/回流焊峰值温度:N/A for Pkg Type,引脚镀层/焊球材料:NIPDAU,TI官网CD4510BE的批量USD价格:.146(1000+)

CD4510BNSR,工作温度:-55 to 125,封装:SO (NS)-16,包装数量MPQ:2000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网CD4510BNSR的批量USD价格:.14(1000+)

CD4510BPWR,工作温度:-55 to 125,封装:TSSOP (PW)-16,包装数量MPQ:2000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网CD4510BPWR的批量USD价格:.127(1000+)

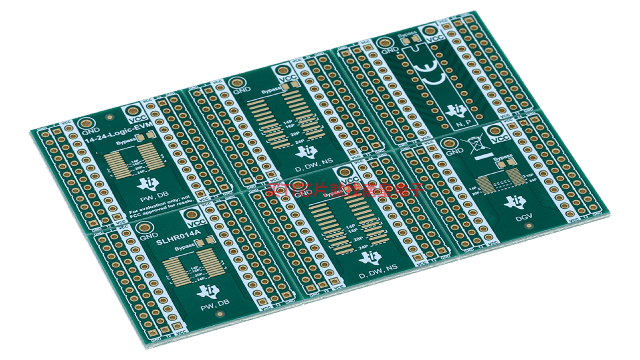

14-24-LOGIC-EVM ― 支持 14 到 24 引脚 PW、DB、D、DW、NS、DYY 和 DGV 封装的通用逻辑 EVM

该 EVM 设计用于支持采用 14 至 24 引脚 D、DW、DB、NS、PW、DYY 或 DGV 封装的任何逻辑器件。