- 制造厂商:TI

- 产品类别:逻辑和电压转换

- 技术类目:专用逻辑 IC - 数字多路信号分离器和解码器

- 功能描述:CMOS 4 位锁存器/4 至 16 线解码器

- 点击这里打开及下载CD4515B的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

CD4514B and CD4515B consist of a 4-bit strobed latch and a 4-to-16-line decoder. The latches hold the last input data presented prior to the strobe transition from 1 to 0. Inhibit control allows all outputs to be placed at 0 (CD4514B) or 1 (CD4515B) regardless of the state of the data or strobe inputs.

The decode truth table indicates all combinations of data inputs and appropriate selected outputs.

These devices are similar to industry types MC14514 and MC14515.

The CD4514B and CD4515B types are supplied in 16-lead hermetic dual-in-line ceramic packages (F3A suffix), 16-lead dual-in-line plastic packages (E suffix), and 16-lead small-outline packages (M and M96 suffixes).

- Strobed input latch

- Inhibit control

- 100% tested for quiescent current at 20 V

- Maximum input current of 1 μA at 18 V over full package-temperature range; 100 nA at 18 V and 25°C

- Noise margin (over full package temperature range):

- 1 V at VDD = 5 V

- 2 V at VDD = 10 V

- 2.5 V at VDD = 15 V

- 5-V, 10-V, and 15-V parametric ratings

- Standardized, symmetrical output characteristics

- Meets all requirements of JEDEC Tentative Standard No. 13B, "Standard Specifications for Description of ’B’ Series CMOS Devices"

- Applications:

- Digital multiplexing

- Address decoding

- Hexadecimal/BCD decoding

- Program-counter decoding

- Control decoder

Data sheet acquired from Harris Semiconductor.

- Technology Family

- CD4000

- Number of channels (#)

- 1

- Operating temperature range (C)

- -55 to 125

- Rating

- Catalog

- ICC (Max) (uA)

- 3000

CD4515B的完整型号有:CD4515BM、CD4515BM96,以下是这些产品的关键参数及官网采购报价:

CD4515BM,工作温度:-55 to 125,封装:SOIC (DW)-24,包装数量MPQ:25个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网CD4515BM的批量USD价格:.353(1000+)

CD4515BM96,工作温度:-55 to 125,封装:SOIC (DW)-24,包装数量MPQ:2000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网CD4515BM96的批量USD价格:.294(1000+)

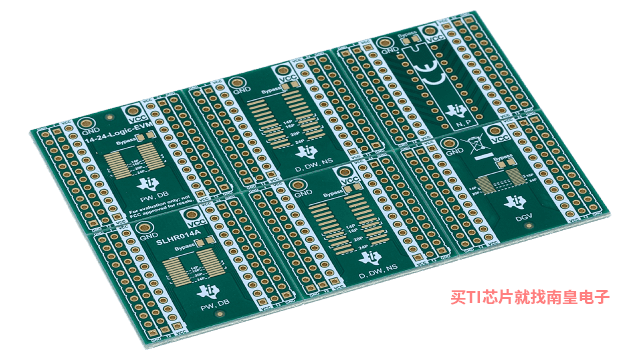

14-24-LOGIC-EVM ― 支持 14 到 24 引脚 PW、DB、D、DW、NS、DYY 和 DGV 封装的通用逻辑 EVM

该 EVM 设计用于支持采用 14 至 24 引脚 D、DW、DB、NS、PW、DYY 或 DGV 封装的任何逻辑器件。