- 制造厂商:TI

- 产品类别:逻辑和电压转换

- 技术类目:触发器、锁存器和寄存器 - D 型触发器

- 功能描述:具有复位功能的六路 D 型触发器

- 点击这里打开及下载CD74ACT174的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

The ’ACT174 devices are positive-edge-triggered D-type flip-flops with a direct clear (CLR)\ input and are designed for 4.5-V to 5.5-V VCC operation.

Information at the data (D) inputs that meets the setup time requirements is transferred to the outputs on the positive-going edge of the clock (CLK) pulse. Clock triggering occurs at a particular voltage level and is not directly related to the transition time of the positive-going edge of CLK. When CLK is at either the high or low level, the D input has no effect at the output.

- Inputs Are TTL-Voltage Compatible

- Contain Six Flip-Flops With Single-Rail Outputs

- Buffered Inputs

- Speed of Bipolar F, AS, and S, With Significantly Reduced Power Consumption

- Balanced Propagation Delays

- ±24-mA Output Drive Current

- Fanout to 15 F Devices

- SCR-Latchup-Resistant CMOS Process and Circuit Design

- Exceeds 2-kV ESD Protection Per MIL-STD-883, Method 3015

- Applications Include:

- Buffer/Storage Registers

- Shift Registers

- Number of channels (#)

- 6

- Technology Family

- ACT

- Supply voltage (Min) (V)

- 4.5

- Supply voltage (Max) (V)

- 5.5

- Input type

- TTL-Compatible CMOS

- Output type

- Push-Pull

- Clock Frequency (Max) (MHz)

- 91

- IOL (Max) (mA)

- 24

- IOH (Max) (mA)

- -24

- ICC (Max) (uA)

- 80

- Features

- Balanced outputs, Very high speed (tpd 5-10ns), Positive input clamp diode

CD74ACT174的完整型号有:CD74ACT174E、CD74ACT174M、CD74ACT174M96,以下是这些产品的关键参数及官网采购报价:

CD74ACT174E,工作温度:-55 to 125,封装:PDIP (N)-16,包装数量MPQ:25个,MSL 等级/回流焊峰值温度:N/A for Pkg Type,引脚镀层/焊球材料:NIPDAU,TI官网CD74ACT174E的批量USD价格:.447(1000+)

CD74ACT174M,工作温度:-55 to 125,封装:SOIC (D)-16,包装数量MPQ:40个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网CD74ACT174M的批量USD价格:.463(1000+)

CD74ACT174M96,工作温度:-55 to 125,封装:SOIC (D)-16,包装数量MPQ:2500个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网CD74ACT174M96的批量USD价格:.397(1000+)

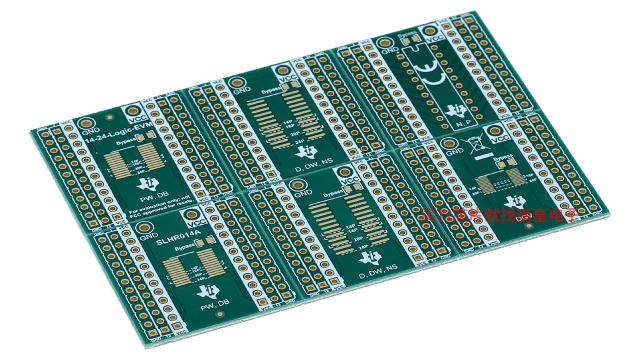

14-24-LOGIC-EVM ― 支持 14 到 24 引脚 PW、DB、D、DW、NS、DYY 和 DGV 封装的通用逻辑 EVM

该 EVM 设计用于支持采用 14 至 24 引脚 D、DW、DB、NS、PW、DYY 或 DGV 封装的任何逻辑器件。