- 制造厂商:TI

- 产品类别:逻辑和电压转换

- 技术类目:缓冲器、驱动器和收发器 - 通用收发器

- 功能描述:具有三态输出的 BiCMOS FCT 接口逻辑八路同向总线收发器

- 点击这里打开及下载CD74FCT623的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

The CD74FCT623 is an octal bus transceiver that uses a small-geometry BiCMOS technology. The output stage is a combination of bipolar and CMOS transistors that limits the output high level to two diode drops below VCC. This resultant lowering of output swing (0 V to 3.7 V) reduces power-bus ringing [a source of electromagnetic interference (EMI)] and minimizes VCC bounce and ground bounce and their effects during simultaneous output switching. The output configuration also enhances switching speed and is capable of sinking 64 mA.

This device is a noninverting, 3-state, bidirectional transceiver-buffer intended for two-way transmission from A bus to B bus or B bus to A bus, depending on the logic levels of the output-enable (OEAB, OEBA\) inputs.

The dual output-enable provision gives these devices the capability to store data by simultaneously enabling OEAB and OEBA\. Each output reinforces its input under these conditions, and when all other data sources to the bus lines are at high impedance, both sets of bus lines remain in their last states.

The CD74FCT623 is characterized for operation from 0°C to 70°C.

- BiCMOS Technology With Low Quiescent Power

- Buffered Inputs

- Noninverted Outputs

- Input/Output Isolation From VCC

- Controlled Output Edge Rates

- 64-mA Output Sink Current

- Output Voltage Swing Limited to 3.7 V

- SCR Latch-Up-Resistant BiCMOS Process and Circuit Design

- Package Options Include Plastic Small-Outline (M) and Shrink Small-Outline (SM) Packages and Standard Plastic (E) DIP

- IOL (Max) (mA)

- 64

- IOH (Max) (mA)

- -15

- Technology Family

- FCT

- Rating

- Catalog

- Operating temperature range (C)

- 0 to 70

CD74FCT623的完整型号有:CD74FCT623M,以下是这些产品的关键参数及官网采购报价:

CD74FCT623M,工作温度:0 to 70,封装:SOIC (DW)-20,包装数量MPQ:25个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网CD74FCT623M的批量USD价格:2.772(1000+)

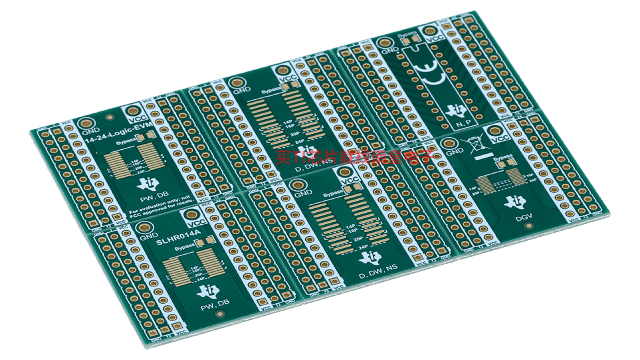

14-24-LOGIC-EVM ― 支持 14 到 24 引脚 PW、DB、D、DW、NS、DYY 和 DGV 封装的通用逻辑 EVM

该 EVM 设计用于支持采用 14 至 24 引脚 D、DW、DB、NS、PW、DYY 或 DGV 封装的任何逻辑器件。