- 制造厂商:TI

- 产品类别:逻辑和电压转换

- 技术类目:触发器、锁存器和寄存器 - 移位寄存器

- 功能描述:高速 CMOS 逻辑 4 位双向通用移位寄存器

- 点击这里打开及下载CD74HC194的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

The ’HC194 and CD74HCT194 are 4-bit shift registers with Asynchronous Master Reset (MR)\. In the parallel mode (S0 and S1 are high), data is loaded into the associated flip-flop and appears at the output after the positive transition of the clock input (CP). During parallel loading serial data flow is inhibited. Shift left and shift right are accomplished synchronously on the positive clock edge with serial data entered at the shift left (DSL) serial input for the shift right mode, and at the shift right (DSR) serial input for the shift left mode. Clearing the register is accomplished by a Low applied to the Master Reset (MR)\ pin.

- Four Operating Modes

- Shift Right, Shift Left, Hold and Reset

- Synchronous Parallel or Serial Operation

- Typical fMAX = 60MHz at VCC = 5V, CL = 15pF, TA = 25°C

- Asynchronous Master Reset

- Fanout (Over Temperature Range)

- Standard Outputs . . . . . . . . . . . . . . . 10 LSTTL Loads

- Bus Driver Outputs . . . . . . . . . . . . . 15 LSTTL Loads

- Wide Operating Temperature Range . . . –55°C to 125°C

- Balanced Propagation Delay and Transition Times

- Significant Power Reduction Compared to LSTTL Logic ICs

- HC Types

- 2V to 6V Operation

- High Noise Immunity: NIL = 30%, NIH = 30% of VCC at VCC = 5V

- HCT Types

- 4.5V to 5.5V Operation

- Direct LSTTL Input Logic Compatibility, VIL = 0.8V (Max), VIH = 2V (Min)

- CMOS Input Compatibility, Il 1μA at VOL, VOH

- Configuration

- Universal

- Bits (#)

- 4

- Technology Family

- HC

- Supply voltage (Min) (V)

- 2

- Supply voltage (Max) (V)

- 6

- Input type

- Standard CMOS

- Output type

- Push-Pull

- Clock Frequency (MHz)

- 60

- IOL (Max) (mA)

- 5.2

- IOH (Max) (mA)

- -5.2

- ICC (Max) (uA)

- 160

- Features

- Balanced outputs, High speed (tpd 10-50ns), Positive input clamp diode

CD74HC194的完整型号有:CD74HC194E、CD74HC194M、CD74HC194M96、CD74HC194PW、CD74HC194PWR、CD74HC194PWT,以下是这些产品的关键参数及官网采购报价:

CD74HC194E,工作温度:-55 to 125,封装:PDIP (N)-16,包装数量MPQ:25个,MSL 等级/回流焊峰值温度:N/A for Pkg Type,引脚镀层/焊球材料:NIPDAU,TI官网CD74HC194E的批量USD价格:.161(1000+)

CD74HC194M,工作温度:-55 to 125,封装:SOIC (D)-16,包装数量MPQ:40个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网CD74HC194M的批量USD价格:.342(1000+)

CD74HC194M96,工作温度:-55 to 125,封装:SOIC (D)-16,包装数量MPQ:2500个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网CD74HC194M96的批量USD价格:.142(1000+)

CD74HC194PW,工作温度:-55 to 125,封装:TSSOP (PW)-16,包装数量MPQ:90个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网CD74HC194PW的批量USD价格:.342(1000+)

CD74HC194PWR,工作温度:-55 to 125,封装:TSSOP (PW)-16,包装数量MPQ:2000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网CD74HC194PWR的批量USD价格:.146(1000+)

CD74HC194PWT,工作温度:-55 to 125,封装:TSSOP (PW)-16,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网CD74HC194PWT的批量USD价格:.342(1000+)

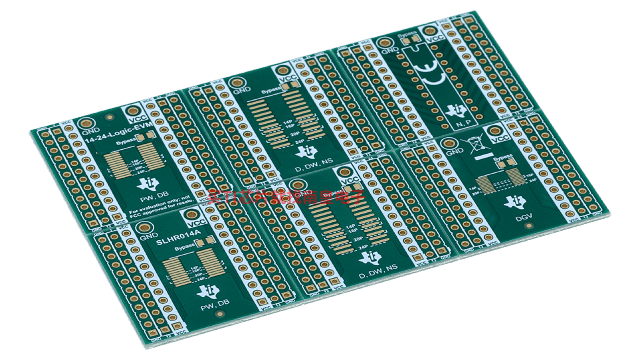

14-24-LOGIC-EVM — 支持 14 到 24 引脚 PW、DB、D、DW、NS、DYY 和 DGV 封装的通用逻辑 EVM

该 EVM 设计用于支持采用 14 至 24 引脚 D、DW、DB、NS、PW、DYY 或 DGV 封装的任何逻辑器件。