- 制造厂商:TI

- 产品类别:逻辑和电压转换

- 技术类目:专用逻辑 IC - 数字计时 IC

- 功能描述:高速 CMOS 逻辑数字锁相环

- 点击这里打开及下载CD74HCT297的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

The ’HC297 and CD74HCT297 are high-speed silicon gate CMOS devices that are pin-compatible with low power Schottky TTL (LSTTL).

These devices are designed to provide a simple, cost-effective solution to high-accuracy, digital, phase-locked-loop applications. They contain all the necessary circuits, with the exception of the divide-by-N counter, to build first-order phase-locked-loops.

Both EXCLUSIVE-OR (XORPD) and edge-controlled phase detectors (ECPD) are provided for maximum flexibility. The input signals for the EXCLUSIVE-OR phase detector must have a 50% duty factor to obtain the maximum lock-range.

Proper partitioning of the loop function, with many of the building blocks external to the package, makes it easy for the designer to incorporate ripple cancellation (see Figure 2) or to cascade to higher order phase-locked-loops.

The length of the up/down K-counter is digitally programmable according to the K-counter function table. With A, B, C and D all LOW, the K-counter is disabled. With A HIGH and B, C and D LOW, the K-counter is only three stages long, which widens the bandwidth or capture range and shortens the lock time of the loop. When A, B, C and D are all programmed HIGH, the K-counter becomes seventeen stages long, which narrows the bandwidth or capture range and lengthens the lock time. Real-time control of loop bandwidth by manipulating the A to D inputs can maximize the overall performance of the digital phase-locked-loop.

The ’HC297 and CD74HCT297 can perform the classic first order phase-locked-loop function without using analog components. The accuracy of the digital phase-locked-loop (DPLL) is not affected by VCC and temperature variations but depends solely on accuracies of the K-clock and loop propagation delays.

- Digital Design Avoids Analog Compensation Errors

- Easily Cascadable for Higher Order Loops

- Useful Frequency Range

- K-Clock...DC to 55MHz (Typ)

- I/D-Clock...DC to 35MHz (Typ)

- Dynamically Variable Bandwidth

- Very Narrow Bandwidth Attainable

- Power-On Reset

- Output Capability

- Standard...XORPDOUT, ECPDOUT

- Bus Driver...I/DOUT

- Fanout (Over Temperature Range)

- Standard Outputs...10 LSTTL Loads

- Bus Driver Outputs...15 LSTTL Loads

- Balanced Propagation Delay and Transition Times

- Significant Power Reduction Compared to LSTTL Logic ICs

- ’HC297 Types

- Operation Voltage...2 to 6V

- High Noise Immunity NIL = 30%, NIH = 30% of VCC at 5V

- CD74HCT297 Types

- Operation Voltage...4.5 to 5.5V

- Direct LSTTL Input Logic Compatibility VIL =0.8V (Max), VIH =2V (Min)

- CMOS Input Compatibility II 1μA at VOL , VOH

Data sheet acquired from Harris Semiconductor

- Technology Family

- HCT

- Bits (#)

- 1

- Supply voltage (Min) (V)

- 4.5

- Supply voltage (Max) (V)

- 5.5

- Input type

- TTL-Compatible CMOS

- Output type

- Push-Pull

- ICC (Max) (uA)

- 160

- IOL (Max) (mA)

- 4

- IOH (Max) (mA)

- -4

CD74HCT297的完整型号有:CD74HCT297E,以下是这些产品的关键参数及官网采购报价:

CD74HCT297E,工作温度:-55 to 125,封装:PDIP (N)-16,包装数量MPQ:25个,MSL 等级/回流焊峰值温度:N/A for Pkg Type,引脚镀层/焊球材料:NIPDAU,TI官网CD74HCT297E的批量USD价格:1.368(1000+)

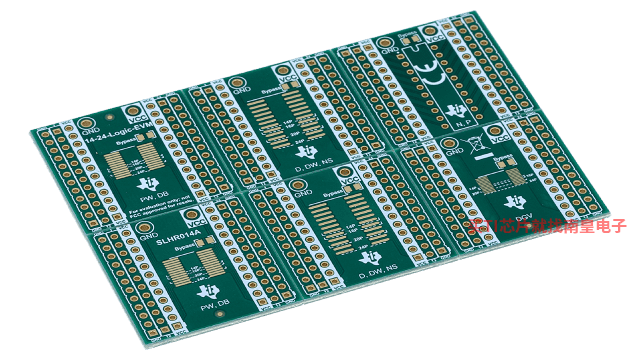

14-24-LOGIC-EVM ― 支持 14 到 24 引脚 PW、DB、D、DW、NS、DYY 和 DGV 封装的通用逻辑 EVM

该 EVM 设计用于支持采用 14 至 24 引脚 D、DW、DB、NS、PW、DYY 或 DGV 封装的任何逻辑器件。