- 制造厂商:TI

- 产品类别:时钟和计时

- 技术类目:时钟缓冲器

- 功能描述:双通道方波/正弦-方波时钟缓冲器

- 点击这里打开及下载CDC3RL02的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

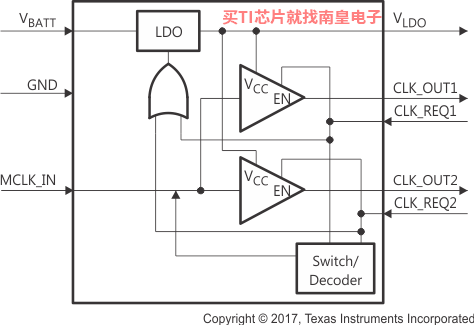

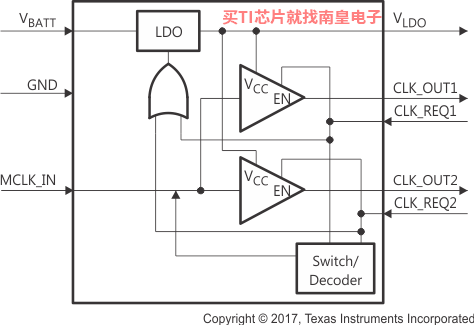

CDC3RL02 是一款双通道时钟扇出缓冲器,非常适用于需要时钟缓冲且具有最小附加相位噪声和扇出功能的便携式终端设备(如手机)。该器件将温度补偿晶体振荡器 (TCXO) 等单个主时钟缓冲至多个外设。该器件具有两个时钟请求输入(CLK_REQ1 和 CLK_REQ2),其中每个输入均支持单个时钟输出。

CDC3RL02 在主时钟输入 (MCLK_IN) 处接受方波或正弦波,无需交流耦合电容器。可接受的最小正弦波为 0.3V 信号(峰峰值)。CDC3RL02 旨在提供极小的通道间偏差、附加输出抖动和附加相位噪声。自适应时钟输出缓冲器可在宽电容负荷范围内提供受控的转换率,从而更大限度地降低 EMI 辐射、保持信号完整性,并更大限度地减少由时钟分配线上的信号反射造成的振铃效应。

CDC3RL02 具有集成的低压降 (LDO) 稳压器,该稳压器可接受 2.3V 至 5.5V 的输入电压,可输出 1.8 V、50mA。该 1.8V 电源可从外部获得,从而为 TCXO 等外围设备提供稳定电源。

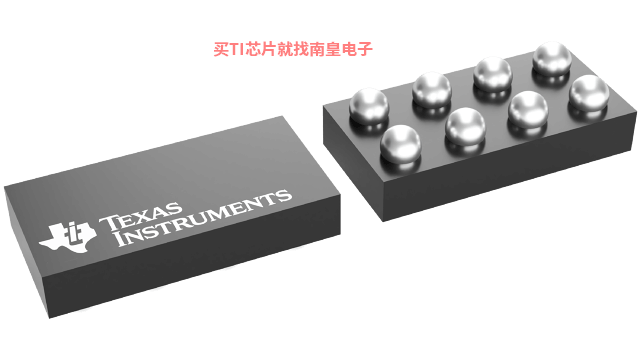

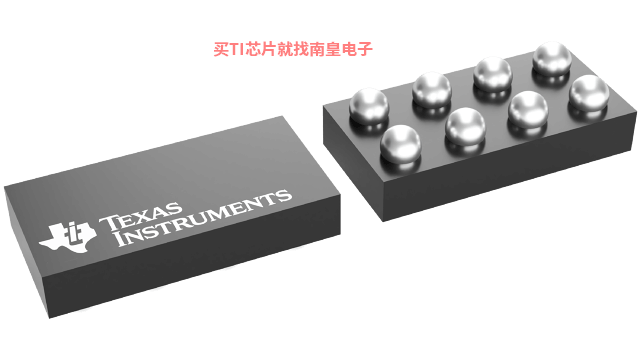

CDC3RL02 采用 0.4mm 间距晶圆级芯片规模 (WCSP) 封装(0.8mm × 1.6mm),并经优化可实现极低的待机电流消耗。

- 低附加噪声:

- 10kHz 偏移相位噪声时为 –149dBc/Hz

- 0.37ps (RMS) 输出抖动

- 限制输出转换率可降低 EMI(对于 10pF 至 50pF 的负载,上升/下降时间为 1ns 至 5ns)

- 自适应输出级控制反射

- 稳压 1.8V 外部可用 I/O 电源

- 超小型 8 凸点 YFP 0.4mm 间距 WCSP(0.8mm × 1.6mm)

- ESD 性能超过 JESD 22

- 2000V 人体放电模型 (A114-A)

- 1000V 带电器件模型(JESD22-C101-A III 级)

- Function

- Single-ended

- Additive RMS jitter (Typ) (fs)

- 370

- Output frequency (Max) (MHz)

- 52

- Number of outputs

- 2

- Output supply voltage (V)

- 1.8

- Core supply voltage (V)

- 1.8

- Output skew (ps)

- 500

- Features

- 1:2 fanout

- Operating temperature range (C)

- -40 to 85

- Rating

- Catalog

- Output type

- SQUARE

- Input type

- SINE, SQUARE

CDC3RL02的完整型号有:CDC3RL02BYFPR、CDC3RL02YFPR,以下是这些产品的关键参数及官网采购报价:

CDC3RL02BYFPR,工作温度:-40 to 85,封装:DSBGA (YFP)-8,包装数量MPQ:3000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:SNAGCU,TI官网CDC3RL02BYFPR的批量USD价格:.546(1000+)

CDC3RL02YFPR,工作温度:-40 to 85,封装:DSBGA (YFP)-8,包装数量MPQ:3000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:SNAGCU,TI官网CDC3RL02YFPR的批量USD价格:.546(1000+)

CDC3RL02 IBIS Model

PSpice for TI 可提供帮助评估模拟电路功能的设计和仿真环境。此功能齐全的设计和仿真套件使用 Cadence 的模拟分析引擎。PSpice for TI 可免费使用,包括业内超大的模型库之一,涵盖我们的模拟和电源产品系列以及精选的模拟行为模型。借助?PSpice for TI 的设计和仿真环境及其内置的模型库,您可对复杂的混合信号设计进行仿真。创建完整的终端设备设计和原型解决方案,然后再进行布局和制造,可缩短产品上市时间并降低开发成本。

在?PSpice for TI 设计和仿真工具中,您可以搜索 TI (...)

CLOCK-TREE-ARCHITECT — 时钟树架构编程软件

时钟树架构是一款时钟树综合工具,可根据您的系统要求生成时钟树解决方案,从而帮助您简化设计流程。该工具从庞大的时钟产品数据库中提取数据,然后生成系统级多芯片时钟解决方案。