- 制造厂商:TI

- 产品类别:时钟和计时

- 技术类目:时钟抖动清除器和同步器

- 功能描述:具有 2.5V 和 3.3V 输出的可编程 1-PLL 时钟合成器和抖动消除器

- 点击这里打开及下载CDCE813-Q1的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

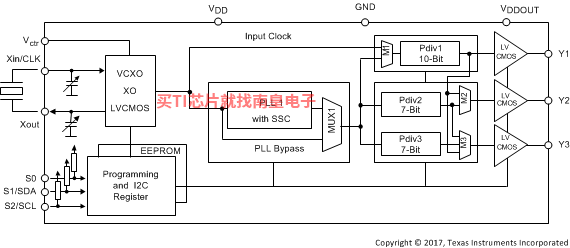

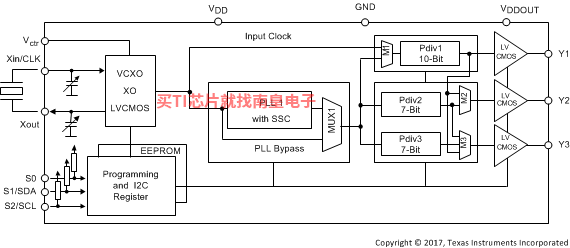

CDCE813-Q1 器件是一款基于模块化锁相环 (PLL) 的低成本、高性能、可编程时钟合成器。它们最多可从单个输入频率中生成 3 个输出时钟。借助集成的可配置 PLL,可在系统内针对任何时钟频率(高达 230MHz)对每个输出进行编程。

CDCE813-Q1 具有独立的输出电源引脚 VDDOUT,可提供 2.5V 至 3.3V 电压。

此输入接受外部晶振或 LVCMOS 时钟信号。凭借可选片载 VCXO,可将输出频率与外部控制信号同步。

PLL 支持 SSC(扩频时钟),从而改善抗电磁干扰 (EMI) 性能。

为了轻松实现器件自定义来满足应用需要,该器件支持使用非易失性 EEPROM 进行编程。所有器件设置均可通过 I2C 总线(一种两线制串行接口)进行编程。

CDCE813-Q1 在 1.8V 内核环境下运行,无需额外使用独立的 XTAL 振荡器,可减少组件数量并缩减电路板尺寸。它的运行温度范围为 –40°C 至 105°C。

- 符合汽车 应用要求

- 具有符合 AEC-Q100 标准的下列特性:

- 器件温度等级 2:–40°C 至 105°C 的环境工作温度范围

- 器件 HBM ESD 分类等级 H2

- 器件 CDM ESD 分类等级 C6

- 系统内可编程和 EEPROM

- 串行可编程易失性寄存器

- 用于存储客户设置的非易失性 EEPROM

- 灵活的输入计时理念

- 外部晶体:8MHz 至 32MHz

- 高达 160MHz 的单端 LVCMOS

- 高达 230MHz 的自由可选输出频率

- 低噪声 PLL 内核

- 已集成的 PLL 环路滤波器组件

- 低电平周期抖动(典型值 50ps)

- 1.8V 器件电源(内核电压)

- 独立的输出电源引脚:3.3V 和 2.5V

- 灵活的时钟驱动器

- 三个用户可定义的控制输入 [S0、S1、S2],例如 SSC 选择、频率切换、输出使能或断电

- 生成适用于视频、音频、USB、IEEE1394 和 RFID、 Bluetooth?、WLAN、以太网和 GPS 的高精度时钟

- 生成可与 TI-DaVinci?、 OMAP?和 DSP 配合使用的共同时钟频率

- 可编程 SSC 调制

- 启用 0-PPM 时钟生成功能

- 采用 TSSOP 封装

- 适用于简易 PLL 设计和编程的开发和编程套件(TI ClockPro?编程软件)

- Function

- Single-loop PLL

- Number of outputs

- 3

- RMS jitter (fs)

- 50000

- Output frequency (Min) (MHz)

- 0.07

- Output frequency (Max) (MHz)

- 230

- Input type

- LVCMOS (REF_CLK)

- Output type

- LVCMOS

- Supply voltage (Min) (V)

- 1.7

- Supply voltage (Max) (V)

- 3.6

- Features

- Integrated EEPROM

- Operating temperature range (C)

- -40 to 105

CDCE813-Q1的完整型号有:CDCE813QPWRQ1、CDCE813R02TPWRQ1,以下是这些产品的关键参数及官网采购报价:

CDCE813QPWRQ1,工作温度:-40 to 105,封装:TSSOP (PW)-14,包装数量MPQ:2000个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:NIPDAU,TI官网CDCE813QPWRQ1的批量USD价格:1.751(1000+)

CDCE813R02TPWRQ1,工作温度:-40 to 105,封装:TSSOP (PW)-14,包装数量MPQ:2000个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:NIPDAU,TI官网CDCE813R02TPWRQ1的批量USD价格:1.751(1000+)

CDCE813 IBIS Model

PSpice for TI 可提供帮助评估模拟电路功能的设计和仿真环境。此功能齐全的设计和仿真套件使用 Cadence 的模拟分析引擎。PSpice for TI 可免费使用,包括业内超大的模型库之一,涵盖我们的模拟和电源产品系列以及精选的模拟行为模型。借助?PSpice for TI 的设计和仿真环境及其内置的模型库,您可对复杂的混合信号设计进行仿真。创建完整的终端设备设计和原型解决方案,然后再进行布局和制造,可缩短产品上市时间并降低开发成本。

在?PSpice for TI 设计和仿真工具中,您可以搜索 TI (...)

CLOCK-TREE-ARCHITECT — 时钟树架构编程软件

时钟树架构是一款时钟树综合工具,可根据您的系统要求生成时钟树解决方案,从而帮助您简化设计流程。该工具从庞大的时钟产品数据库中提取数据,然后生成系统级多芯片时钟解决方案。