- 制造厂商:TI

- 产品类别:时钟和计时

- 技术类目:时钟缓冲器

- 功能描述:具有单个输出使能/禁用功能的 1.8V 1:10 高性能差动时钟缓冲器

- 点击这里打开及下载CDCL1810A的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

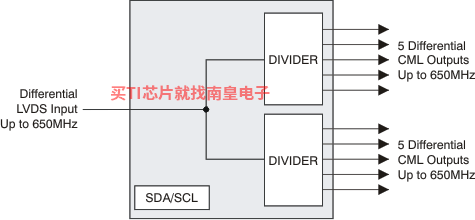

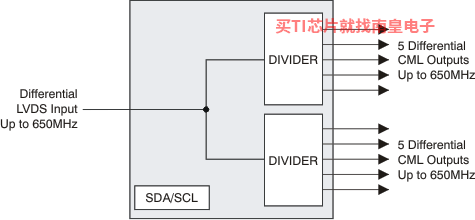

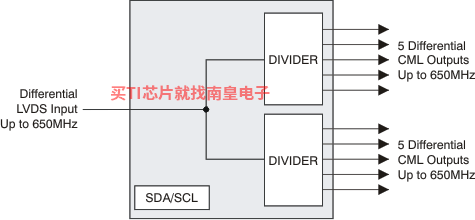

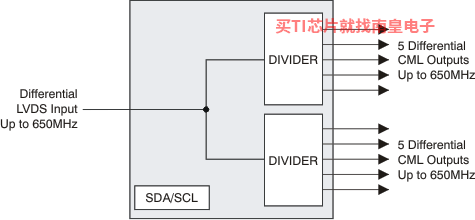

CDCL1810A 是一款高性能时钟分配器。 可编程分频器(P0 和 P1)为输出输入频率比的设置提供了较高的灵活性:FOUT = FIN/P,其中 P(P0 或 P1)= 1、2、4、5、8、10、16、20、32、40、80。

CDCL1810A 支持 1 个差分 LVDS 时钟输入以及总共 10 个差分 CML 输出。 CML 输出为交流耦合时,可兼容 LVDS 接收器。

在认真遵守输入电压摆幅和共模电压限制的情况下,CDCL1810A 可支持中概述的单端时钟输入。

所有器件设置均可通过两线制串口 SDA/SCL 进行编程。 该串口只能承受 1.8V 电压。

此器件在 1.8V 电源供电环境下运行,额定工作温度范围为 –40°C 至 +85°C。 CDCL1810A 采用 48 引脚 QFN (RGZ) 封装。

- 1.8V 单电源

- 具有 10 输出的高性能时钟分配器

- 低输入输出附加抖动:低至 10fs 均方根 (RMS)

- 低压差分信令 (LVDS) 输入,100? 差分片上端接,频率高达 650MHz

- 差分电流模式逻辑 (CML) 输出、50? 单端片上端接、频率高达 650MHz

- 两组输出,每组有 5 个且均具有独立的频分比

- 输出频率可采用 1、2、4、5、8、10、16、20、32、40 和 80 频分比

- 符合 ANSI TIA/EIA-644-A-2001 LVDS 标准要求

- 功耗:410mW(典型值)

- 针对每个输出的输出使能控制

- 串行数据/串行时钟 (SDA/SCL) 器件管理接口

- 48 引脚超薄四方扁平无引线 (VQFN) (RGZ) 封装

- 工业温度范围:-40°C 至 +85°C

- 针对高速串行解串器 (SERDES) 的时钟分配

- 针对 1G/10G 以太网、1X/2X/4X/10X 光纤通道、PCI Express、串行 ATA、同步光纤网 (SONET)、通用公共无线接口 (CPRI) 和开放式基站架构联盟 (OBSAI) 等的 SERDES 基准时钟分配

- 多达 1 到 10 的时钟缓冲和扇出

All trademarks are the property of their respective owners. All trademarks are the property of their respective owners.

- Function

- Clock buffer, Clock divider

- Additive RMS jitter (Typ) (fs)

- 40

- Output frequency (Max) (MHz)

- 650

- Number of outputs

- 10

- Output supply voltage (V)

- 1.8

- Core supply voltage (V)

- 1.8

- Output skew (ps)

- 64

- Features

- I2C interface

- Operating temperature range (C)

- -40 to 85

- Rating

- Catalog

- Output type

- CML

- Input type

- LVDS

CDCL1810A的完整型号有:CDCL1810ARGZR、CDCL1810ARGZT,以下是这些产品的关键参数及官网采购报价:

CDCL1810ARGZR,工作温度:-40 to 85,封装:VQFN (RGZ)-48,包装数量MPQ:2500个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:NIPDAU,TI官网CDCL1810ARGZR的批量USD价格:5.933(1000+)

CDCL1810ARGZT,工作温度:-40 to 85,封装:VQFN (RGZ)-48,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:NIPDAU,TI官网CDCL1810ARGZT的批量USD价格:7.12(1000+)

CDCL1810A IBIS Software

PSpice for TI 可提供帮助评估模拟电路功能的设计和仿真环境。此功能齐全的设计和仿真套件使用 Cadence 的模拟分析引擎。PSpice for TI 可免费使用,包括业内超大的模型库之一,涵盖我们的模拟和电源产品系列以及精选的模拟行为模型。借助?PSpice for TI 的设计和仿真环境及其内置的模型库,您可对复杂的混合信号设计进行仿真。创建完整的终端设备设计和原型解决方案,然后再进行布局和制造,可缩短产品上市时间并降低开发成本。

在?PSpice for TI 设计和仿真工具中,您可以搜索 TI (...)

CLOCK-TREE-ARCHITECT ― 时钟树架构编程软件

时钟树架构是一款时钟树综合工具,可根据您的系统要求生成时钟树解决方案,从而帮助您简化设计流程。该工具从庞大的时钟产品数据库中提取数据,然后生成系统级多芯片时钟解决方案。