- ���쳧�̣�TI

- ��Ʒ���ʱ�Ӻͼ�ʱ

- ������Ŀ��ʱ�ӻ�����

- ����������ͨ�����롢10 ������迹 LVCMOS ������

- ������������CDCLVC1310�ļ����ĵ�����

- TI�����������ṩ���շ������ϸ������������������Ŀ��۸�

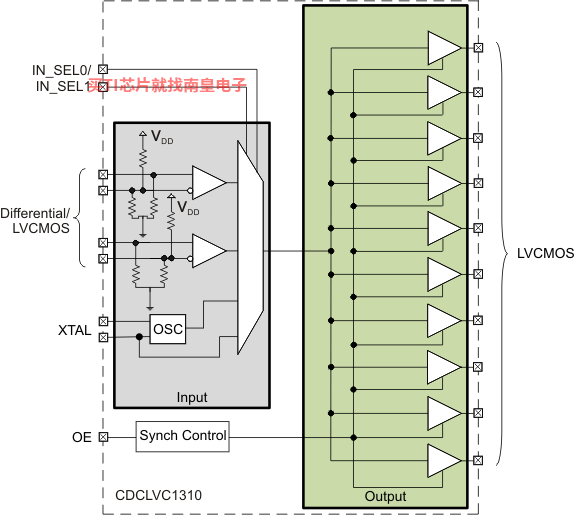

CDCLVC1310 ��һ�����;���Ͷ���������ʱ���ȳ����������˻������ɽ����� 3 �������е� 1 �����䵽 10 ���Ͷ��� LVCOMS ʱ��������� 3 ������������������в�ֻ��ߵ����źź;������롣 ��������ʺ����ڶ����ƶ�����������ʩ������ͨ�š����㡢����ҽ�Ƴ���ͱ�Яʽ���ԺͲ���Ӧ�á� ������Ϊ�Ƿ���ƽʱ���������һ��ȷ����״̬�ϡ� �ɽ��ں˵�ѹ�趨�� 2.5V �� 3.3V �ϣ�������趨�� 1.5V��1.8V��2.5V �� 3.3V �ϡ����ű�̿����ɵ����� CDCLVC1310�� ���帽�Ӷ�������Ϊ 25fsRMS������ֵ���� CDCLVC1310 ��װ��С�� 32 ���� 5mm x 5mm QFN ��װ�ڡ�

- ֧�� -169dBc/Hz ���ͱ��������ĸ����ܾ�����

- ���ӵ���λ����/��������Ϊ 25fsRMS������ֵ��

- ���� 3.3V �� 2.5V �ں˵�ѹ�� 3.3V��2.5V��1.8V �� 1.5V �����Դ�ĵ�ƽת��

- ������������������μ��;������벢��ʹ������ MUX �����ֹ�ѡ��ͨ�����ţ��� �����ʹμ������ܹ����ܵ͵�ѹ���伫����� (LVPECL)����ѹ����ź� (LVDS)������ʱ���źŵ�ƽ (HCSL)��SSTL ���ߵ�ѹ CMOS (LVCMOS) �źź;������롣

- ֧��8MHz �� 50MHz �ľ���Ƶ��

- ֧�ָߴ� 200MHz �IJ�ֺ͵�������Ƶ�ʡ�

- 10 ������ LVCMOS ����� ����������� 1.5V��1.8V��2.5V ���� 3.3V �ĵ�Դ��ѹ�¡�

- LVCOMS �������Ƶ�ʸߴ� 200MHz

- ���ƫ��Ϊ 30ps������ֵ��

- �ܴ����ӳ�Ϊ 2ns������ֵ��

- ͬ������ë������������ÿ���

- ���÷��α�ƽ������ (QFN)-32 5mm x 5mm ��װ���乤ҵ�¶ȷ�ΧΪ�C40��C �� 85��C��

- �ܹ��������� LVCOMS �źŸߴ� 50MHz �ľ�������

- ���ߺ���������ʩ

- ���������ͨ��

- ҽ�Ƴ���

- ��Яʽ���ԺͲ���

- �߶� A/V

- Function

- Single-ended

- Additive RMS jitter (Typ) (fs)

- 25

- Output frequency (Max) (MHz)

- 200

- Number of outputs

- 10

- Output supply voltage (V)

- 1.5, 1.8, 2.5, 3.3

- Core supply voltage (V)

- 2.5, 3.3

- Output skew (ps)

- 50

- Features

- 1:10 fanout, Level translation

- Operating temperature range (C)

- -40 to 85

- Rating

- Catalog

- Output type

- LVCMOS

- Input type

- HCSL, LVCMOS, LVDS, LVPECL, SSTL, XTAL

CDCLVC1310�������ͺ��У�CDCLVC1310RHBR����������Щ��Ʒ�Ĺؼ������������ɹ����ۣ�

CDCLVC1310RHBR�������¶ȣ�-40 to 85����װ��VQFN (RHB)-32����װ����MPQ��3000����MSL �ȼ�/��������ֵ�¶ȣ�Level-2-260C-1 YEAR�����ŶƲ�/������ϣ�NIPDAU��TI����CDCLVC1310RHBR������USD�۸�2.21��1000+��

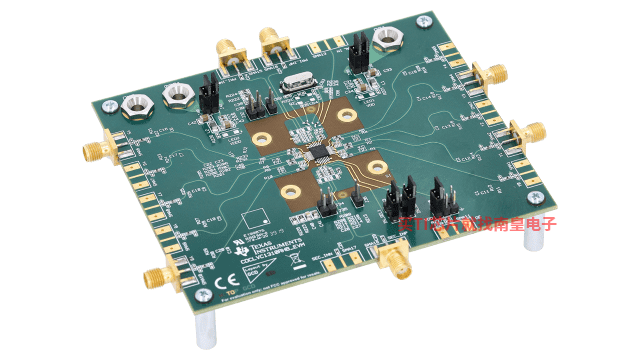

CDCLVC1310-EVM �� CDCLVC1310 ����ģ��

CDCLVC1310 ��һ��߶ȶ������ĵͶ���������ʱ���ȳ����������ɷ����� 10 ��Ͷ��� LVCMOS ʱ������� ʱ����Դ�� 3 �������е� 1 �飬�����������������֧�ֲ�ֻ��źţ����� 3 ���������Ǿ������롣

CDCLVC1310 IBIS Model

PSpice for TI ���ṩ��������ģ���·���ܵ���ƺͷ��滷�����˹�����ȫ����ƺͷ�����ʹ�� Cadence ��ģ��������档PSpice for TI �����ʹ�ã�����ҵ�ڳ����ģ�Ϳ�֮һ���������ǵ�ģ��͵�Դ��Ʒϵ���Լ���ѡ��ģ����Ϊģ�͡�����?PSpice for TI ����ƺͷ��滷���������õ�ģ�Ϳ⣬���ɶԸ��ӵĻ���ź���ƽ��з��档�����������ն��豸��ƺ�ԭ�ͽ��������Ȼ���ٽ��в��ֺ����죬�����̲�Ʒ����ʱ�䲢���Ϳ����ɱ���

��?PSpice for TI ��ƺͷ��湤���У����������� TI (...)

CLOCK-TREE-ARCHITECT �� ʱ�����ܹ��������

ʱ�����ܹ���һ��ʱ�����ۺϹ��ߣ��ɸ�������ϵͳҪ������ʱ��������������Ӷ���������������̡��ù��ߴ��Ӵ��ʱ�Ӳ�Ʒ���ݿ�����ȡ���ݣ�Ȼ������ϵͳ����оƬʱ�ӽ��������