- 制造厂商:TI

- 产品类别:时钟和计时

- 技术类目:时钟缓冲器

- 功能描述:通过超小偏斜实现时钟分配且频率高达 1100MHz 的 1:10 LVDS 时钟缓冲器

- 点击这里打开及下载CDCLVD110A的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

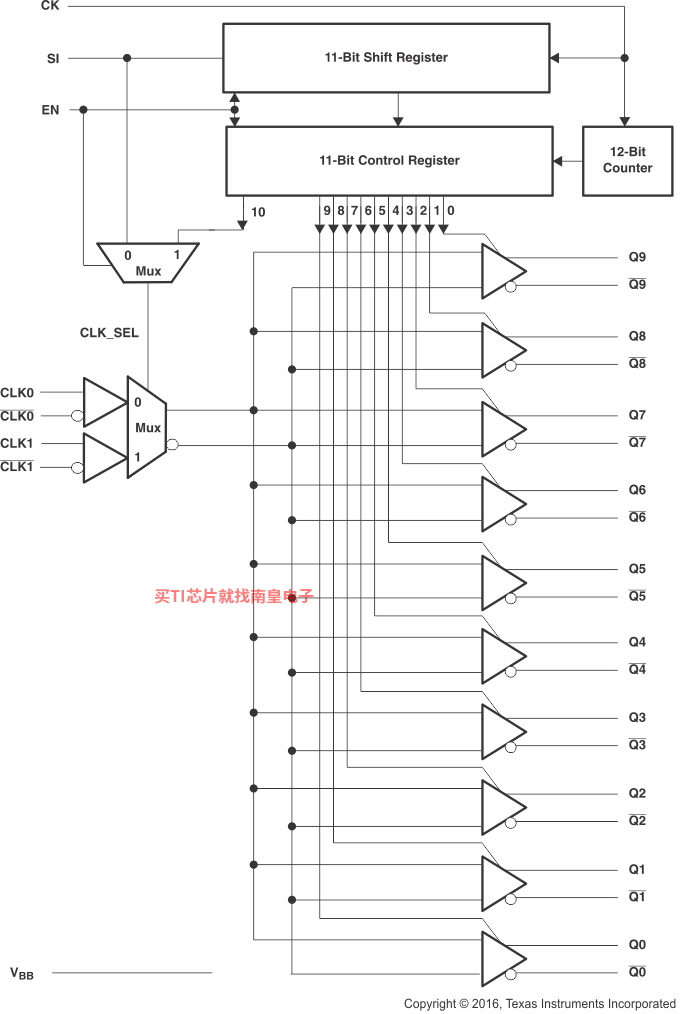

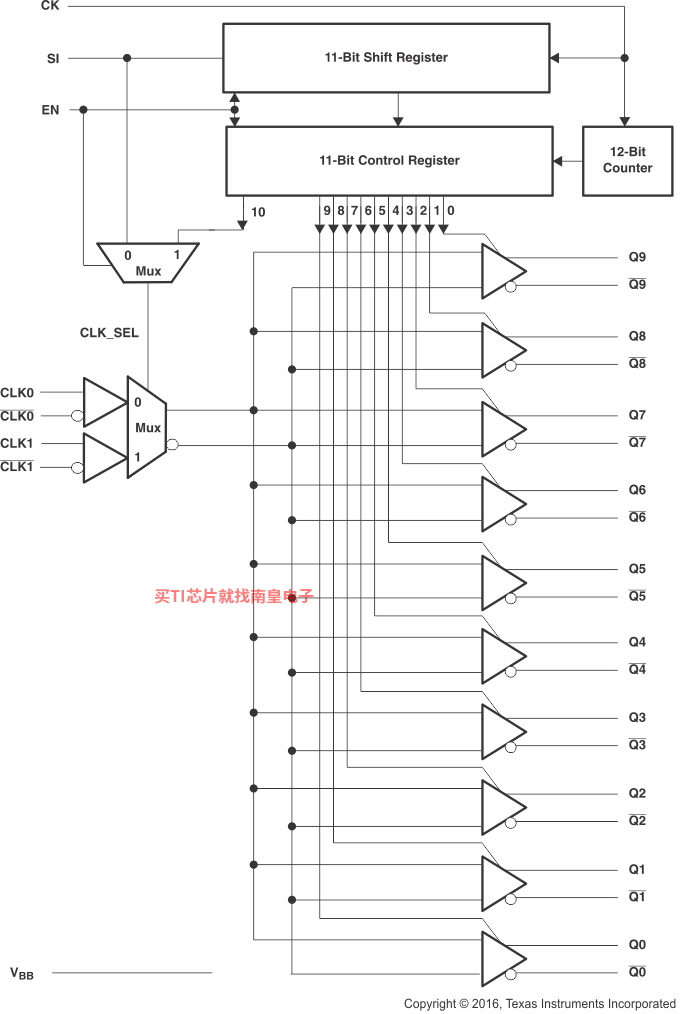

The CDCLVD110A clock driver distributes one pair of differential LVDS clock inputs (either CLK0 or CLK1) to 10 pairs of differential clock outputs (Q0 to Q9) with minimum skew for clock distribution. The CDCLVD110A is specifically designed to drive 50-Ω transmission lines.

When the control enable is high (EN = 1), the 10 differential outputs are programmable in that each output can be individually enabled or disabled

(3-stated) according to the first 10 bits loaded into the shift register. Once the shift register is loaded, the last bit selects either CLK0 or CLK1 as the clock input. However, when EN = 0, the outputs are not programmable and all outputs are enabled.

The CDCLVD110A has an improved start-up circuit that minimizes enabling time in AC- and DC-coupled systems.

The CDCLVD110A is characterized for operation from –40°C to 85°C.

- Low-Output Skew <30 ps (Typical) for Clock-Distribution Applications

- Distributes One Differential Clock Input to 10 LVDS Differential Clock Outputs

- VCC Range: 2.5 V ±5%

- Typical Signaling Rate Capability of Up to 1.1 GHz

- Configurable Register (SI/CK) Individually Enables Disables Outputs, Selectable CLK0, CLK0 or CLK1, CLK1 Inputs

- Full Rail-to-Rail Common-Mode Input Range

- Receiver Input Threshold: ±100 mV

- Available in 32-Pin LQFP and VQFN Package

- Fail-Safe I/O-Pins for VDD = 0 V (Power Down)

- Function

- Differential

- Additive RMS jitter (Typ) (fs)

- 111

- Output frequency (Max) (MHz)

- 1100

- Number of outputs

- 10

- Output supply voltage (V)

- 2.5

- Core supply voltage (V)

- 2.5

- Output skew (ps)

- 50

- Features

- 1:10 fanout, Individual output enable control

- Operating temperature range (C)

- -40 to 85

- Rating

- Catalog

- Output type

- LVDS

- Input type

- LVDS

CDCLVD110A的完整型号有:CDCLVD110ARHBR、CDCLVD110ARHBT、CDCLVD110AVF、CDCLVD110AVFR,以下是这些产品的关键参数及官网采购报价:

CDCLVD110ARHBR,工作温度:-40 to 85,封装:VQFN (RHB)-32,包装数量MPQ:3000个,MSL 等级/回流焊峰值温度:Level-2-260C-1 YEAR,引脚镀层/焊球材料:NIPDAU,TI官网CDCLVD110ARHBR的批量USD价格:5.452(1000+)

CDCLVD110ARHBT,工作温度:-40 to 85,封装:VQFN (RHB)-32,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-2-260C-1 YEAR,引脚镀层/焊球材料:NIPDAU,TI官网CDCLVD110ARHBT的批量USD价格:6.542(1000+)

CDCLVD110AVF,工作温度:-40 to 85,封装:LQFP (VF)-32,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网CDCLVD110AVF的批量USD价格:6.542(1000+)

CDCLVD110AVFR,工作温度:-40 to 85,封装:LQFP (VF)-32,包装数量MPQ:1000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网CDCLVD110AVFR的批量USD价格:5.452(1000+)

CDCLVD110A IBIS Software

PSpice for TI 可提供帮助评估模拟电路功能的设计和仿真环境。此功能齐全的设计和仿真套件使用 Cadence 的模拟分析引擎。PSpice for TI 可免费使用,包括业内超大的模型库之一,涵盖我们的模拟和电源产品系列以及精选的模拟行为模型。借助?PSpice for TI 的设计和仿真环境及其内置的模型库,您可对复杂的混合信号设计进行仿真。创建完整的终端设备设计和原型解决方案,然后再进行布局和制造,可缩短产品上市时间并降低开发成本。

在?PSpice for TI 设计和仿真工具中,您可以搜索 TI (...)

CLOCK-TREE-ARCHITECT ― 时钟树架构编程软件

时钟树架构是一款时钟树综合工具,可根据您的系统要求生成时钟树解决方案,从而帮助您简化设计流程。该工具从庞大的时钟产品数据库中提取数据,然后生成系统级多芯片时钟解决方案。