- 制造厂商:TI

- 产品类别:时钟和计时

- 技术类目:时钟缓冲器

- 功能描述:具有可选输入时钟驱动器的 1:10 高速时钟缓冲器

- 点击这里打开及下载CDCLVP111-SP的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

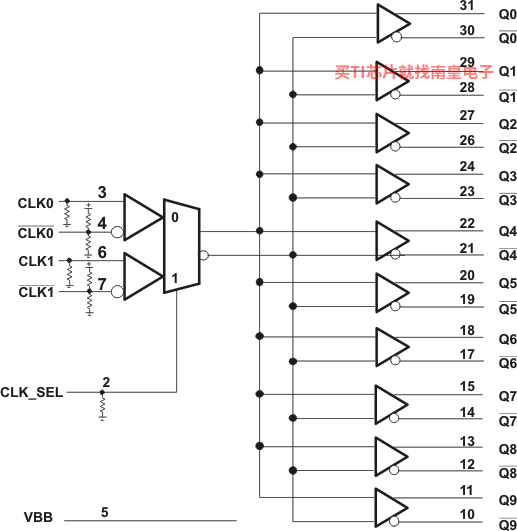

CDCLVP111-SP 时钟驱动器能够以最低时钟分配偏移将 LVPECL 输入的一对差分时钟(CLK0 和 CLK1)分配至十对差分 LVPECL 时钟(Q0 和 Q9)输出。CDCLVP111-SP 可接受两个时钟源传入一个输入多路复用器。CDCLVP111-SP 专为驱动 50Ω 传输线路而设计。当一个输出引脚不被使用时,建议将其保持在开状态以减少功耗。如果只使用差分对中的输出引脚中的一个,那么其它输出引脚必须被同样地端接至 50Ω。

如果要求单端输入运行,VBB基准电压输出被使用。在这种情况下,VBB引脚应该被连接至CLK0并由一个 10nF 电容器旁通至接地 (GND)。

如需实现高速性能,强烈建议采用差分模式。

CDCLVP111-SP 的额定工作温度范围为 -55°C 至 125°C。

- 将一个差分时钟输入对 LVPECL 分配至 10 个差分 LVPECL

- 与低压发射器耦合逻辑 (LVECL) 和 LVPECL 完全兼容

- 支持 2.375V 至 3.8V 的宽电源电压范围

- 通过 CLK_SEL 可选择时钟输入

- 低输出偏移(典型值为 15ps),适用于时钟分配 应用

- 额外抖动少于 1ps

- 传播延迟少于 355ps

- 开输入缺省状态

- 兼容低压差分信令 (LVDS)、电流模式逻辑 (CML) 和短截线串联端接逻辑 (SSTL) 输入

- 针对单端计时的 VBB 基准电压输出

- 频率范围为直流至 3.5GHz

- 支持国防、航天和医疗 应用

- 受控基线

- 同一组装和测试场所

- 同一制造场所

- 支持军用温度范围(-55°C 至 125°C) (1)

- 延长的产品生命周期

- 延长产品的变更通知周期

- 产品可追溯性

(1)提供定制温度范围。

- Function

- Differential

- Additive RMS jitter (Typ) (fs)

- 40

- Output frequency (Max) (MHz)

- 3500

- Number of outputs

- 10

- Output supply voltage (V)

- 3.3

- Core supply voltage (V)

- 3.3

- Output skew (ps)

- 50

- Features

- 1:10 fanout

- Operating temperature range (C)

- 25 to 25, -55 to 125

- Rating

- Space

- Output type

- LVPECL

- Input type

- CML, LVDS, LVPECL, SSTL

CDCLVP111-SP的完整型号有:5962-1620701VXC、CDCLVP111HFG/EM,以下是这些产品的关键参数及官网采购报价:

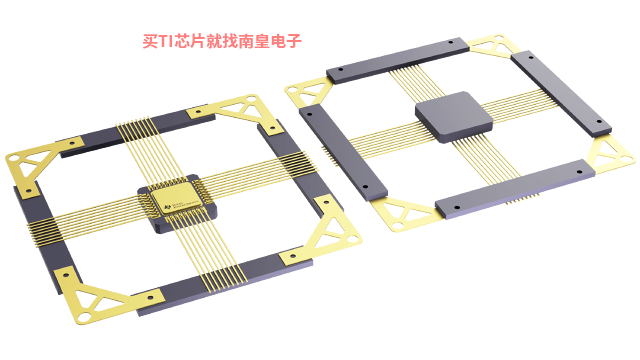

5962-1620701VXC,工作温度:-55 to 125,封装:CFP (HFG)-36,包装数量MPQ:1个,MSL 等级/回流焊峰值温度:N/A for Pkg Type,引脚镀层/焊球材料:Call TI,TI官网5962-1620701VXC的批量USD价格:2722.694(1000+)

CDCLVP111HFG/EM,工作温度:25 to 25,封装:CFP (HFG)-36,包装数量MPQ:1个,MSL 等级/回流焊峰值温度:N/A for Pkg Type,引脚镀层/焊球材料:Call TI,TI官网CDCLVP111HFG/EM的批量USD价格:1009.872(1000+)

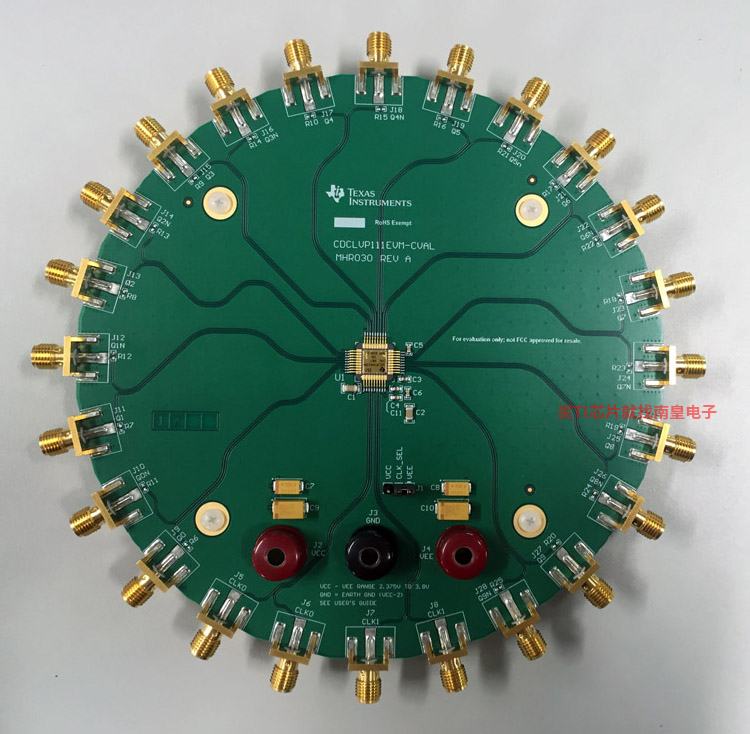

CDCLVP111EVM-CVAL — CDCLVP111-SP 1:10 LVPECL 时钟驱动器评估模块

CDCLVP111-SP EVM 利用陶瓷工程模型 (EM) 能够实现 CDCLVP111 时钟分配缓冲器的测试和验证。CDCLVP111 IBIS Model Version 2.0 (Rev. B)

PSpice for TI 可提供帮助评估模拟电路功能的设计和仿真环境。此功能齐全的设计和仿真套件使用 Cadence 的模拟分析引擎。PSpice for TI 可免费使用,包括业内超大的模型库之一,涵盖我们的模拟和电源产品系列以及精选的模拟行为模型。借助?PSpice for TI 的设计和仿真环境及其内置的模型库,您可对复杂的混合信号设计进行仿真。创建完整的终端设备设计和原型解决方案,然后再进行布局和制造,可缩短产品上市时间并降低开发成本。

在?PSpice for TI 设计和仿真工具中,您可以搜索 TI (...)

CLOCK-TREE-ARCHITECT — 时钟树架构编程软件

时钟树架构是一款时钟树综合工具,可根据您的系统要求生成时钟树解决方案,从而帮助您简化设计流程。该工具从庞大的时钟产品数据库中提取数据,然后生成系统级多芯片时钟解决方案。