- 制造厂商:TI

- 产品类别:时钟和计时

- 技术类目:时钟发生器

- 功能描述:1:2 超低抖动晶振时钟发生器

- 点击这里打开及下载CDCM61002的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

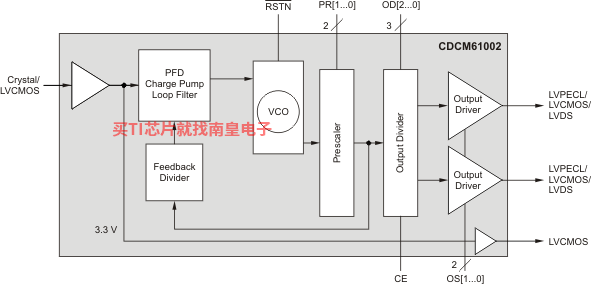

The CDCM61002 is a highly versatile, low-jitter frequency synthesizer that can generate two low-jitter clock outputs, selectable between low-voltage positive emitter coupled logic (LVPECL), low-voltage differential signaling (LVDS), or low-voltage complementary metal oxide semiconductor (LVCMOS) outputs, from a low-frequency crystal or LVCMOS input for a variety of wireline and data communication applications. The CDCM61002 features an onboard PLL that can be easily configured solely through control pins. The overall output random jitter performance is less than 1ps, RMS (from 10 kHz to 20 MHz), making this device a perfect choice for use in demanding applications such as SONET, Ethernet, Fibre Channel, and SAN. The CDCM61002 is available in a small, 32-pin, 5-mm × 5-mm QFN package.

The CDCM61002 is a high-performance, low phase noise, fully-integrated voltage-controlled oscillator (VCO) clock synthesizer with two universal output buffers that can be configured to be LVPECL, LVDS, or LVCMOS compatible. Each universal output can also be converted to two LVCMOS outputs. Additionally, an LVCMOS bypass output clock is available in an output configuration which can help with crystal loading in order to achieve an exact desired input frequency. It has one fully-integrated, low-noise, LC-based VCO that operates in the 1.75 GHz to 2.05 GHz range.

The phase-locked loop (PLL) synchronizes the VCO with respect to the input, which can either be a low-frequency crystal. The outputs share an output divider sourced from the VCO core. All device settings are managed through a control pin structure, which has two pins that control the prescaler and feedback divider, three pins that control the output divider, two pins that control the output type, and one pin that controls the output enable. Any time the PLL settings (including the input frequency, prescaler divider, or feedback divider) are altered, a reset must be issued through the Reset control pin (active low for device reset). The reset initiates a PLL recalibration process to ensure PLL lock. When the device is in reset, the outputs and dividered are turned off.

The output frequency (fOUT) is proportional to the frequency of the input clock (fIN). The feedback divider, output divider, and VCO frequency set fOUT with respect to fIN. For a configuration setting for common wireline and datacom applications, refer to. For other applications, use to calculate the exact crystal oscillator frequency required for the desired output.

The output divider can be chosen from 1, 2, 3, 4, 6, or 8 through the use of control pins. Feedback divider and prescaler divider combinations can be chosen from 25 and 3, 24 and 3, 20 and 4, or 15 and 5, respectively, also through the use of control pins. shows a high-level block diagram of the CDCM61002.

The device operates in a 3.3-V supply environment and is characterized for operation from –40°C to +85°C.

- One Crystal/LVCMOS Reference Input Including 24.8832 MHz, 25 MHz, and 26.5625 MHz

- Input Frequency Range: 21.875 MHz to 28.47 MHz

- On-Chip VCO Operates in Frequency Range of 1.75 GHz to 2.05 GHz

- 2x Output Available:

- Pin-Selectable Between LVPECL, LVDS, or 2-LVCMOS; Operates at 3.3 V

- LVCMOS Bypass Output Available

- Output Frequency Selectable by /1, /2, /3, /4, /6, /8 from a Single Output Divider

- Supports Common LVPECL/LVDS Output Frequencies:

- 62.5 MHz, 74.25 MHz, 75 MHz, 77.76 MHz, 100 MHz, 106.25 MHz, 125 MHz, 150 MHz, 155.52 MHz, 156.25 MHz, 159.375 MHz, 187.5 MHz, 200 MHz, 212.5 MHz, 250 MHz, 311.04 MHz, 312.5 MHz, 622.08 MHz, 625 MHz

- Supports Common LVCMOS Output Frequencies:

- 62.5 MHz, 74.25 MHz, 75 MHz, 77.76 MHz, 100 MHz, 106.25 MHz, 125 MHz, 150 MHz, 155.52 MHz, 156.25 MHz, 159.375 MHz, 187.5 MHz, 200 MHz, 212.5 MHz, 250 MHz

- Output Frequency Range: 43.75 MHz to 683.264 MHz

- Internal PLL Loop Bandwidth: 400 kHz

- High-Performance PLL Core:

- Phase Noise typically at –146 dBc/Hz at 5-MHz Offset for 625-MHz LVPECL Output

- Random Jitter typically at 0.509 ps, RMS (10 kHz to 20 MHz) for 625-MHz LVPECL Output

- Output Duty Cycle Corrected to 50% (± 5%)

- Low Output Skew of 20 ps on LVPECL Outputs

- Divider Programming Using Control Pins:

- Two Pins for Prescaler/Feedback Divider

- Three Pins for Output Divider

- Two Pins for Output Select

- Chip Enable Control Pin Available

- 3.3-V Core and I/O Power Supply

- Industrial Temperature Range: –40°C to +85°C

- 5-mm × 5-mm, 32-pin, QFN (RHB) Package

- ESD Protection Exceeds 2 kV (HBM)

- Function

- Clock generator

- Number of outputs

- 2

- Output frequency (Max) (MHz)

- 683.28

- Core supply voltage (V)

- 3.3

- Output supply voltage (V)

- 3.3

- Input type

- XTAL

- Output type

- LVPECL

- Operating temperature range (C)

- -40 to 85

- Features

- Pin programmable

- Rating

- Catalog

CDCM61002的完整型号有:CDCM61002RHBR、CDCM61002RHBT,以下是这些产品的关键参数及官网采购报价:

CDCM61002RHBR,工作温度:-40 to 85,封装:VQFN (RHB)-32,包装数量MPQ:3000个,MSL 等级/回流焊峰值温度:Level-2-260C-1 YEAR,引脚镀层/焊球材料:NIPDAUAG,TI官网CDCM61002RHBR的批量USD价格:2.464(1000+)

CDCM61002RHBT,工作温度:-40 to 85,封装:VQFN (RHB)-32,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-2-260C-1 YEAR,引脚镀层/焊球材料:NIPDAUAG,TI官网CDCM61002RHBT的批量USD价格:2.957(1000+)

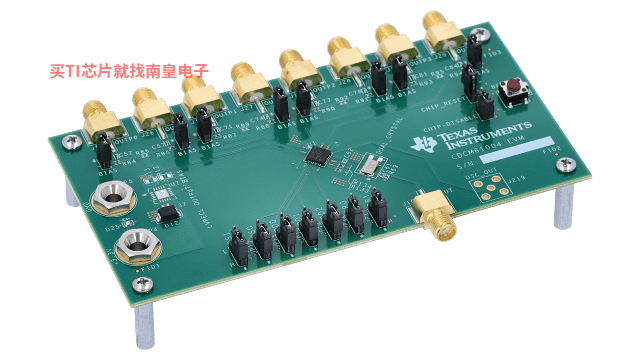

CDCM6100XEVM — CDCM61004/CDCM61002/CDCM61001 评估模块

CDCM6100xEVM is the evaluation module for CDCM61004 or CDCM61002 or CDCM61001. CDCM61004/2/1 family is a highly versatile, ultra low-jitter frequency synthesizer family that can generate four/two/one low-jitter clock output pairs, selectable among LVPECL, LVDS, or 2 LVCMOS, from a low-frequency (...)

TMDXEVM388 — DM388 DaVinci 数字媒体处理器评估模块

借助 DM38x 数字视频评估模块 (DVEVM),开发人员可立即开始评估 DM38x 数字媒体处理器,并开始构建数字视频应用,例如 IP 安全摄像头、运动摄像头、无人机、可视门铃、车用数字录像机和其他数字视频产品。此数字视频评估模块 (DVEVM) 支持开发人员编写适用于 ARM 的生产就绪型应用代码,并通过 API 访问 HDVICP 协处理器内核,适用于 DM385、DM388 和 DM389 数字媒体处理器。CDCM61002 IBIS Model (Rev. B)

PSpice for TI 可提供帮助评估模拟电路功能的设计和仿真环境。此功能齐全的设计和仿真套件使用 Cadence 的模拟分析引擎。PSpice for TI 可免费使用,包括业内超大的模型库之一,涵盖我们的模拟和电源产品系列以及精选的模拟行为模型。借助?PSpice for TI 的设计和仿真环境及其内置的模型库,您可对复杂的混合信号设计进行仿真。创建完整的终端设备设计和原型解决方案,然后再进行布局和制造,可缩短产品上市时间并降低开发成本。

在?PSpice for TI 设计和仿真工具中,您可以搜索 TI (...)