- 制造厂商:TI

- 产品类别:时钟和计时

- 技术类目:时钟抖动清除器和同步器

- 功能描述:高性能、低相位噪声、低偏移的时钟同步器(使参考时钟与 VCXO 同步)

- 点击这里打开及下载CDCM7005的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

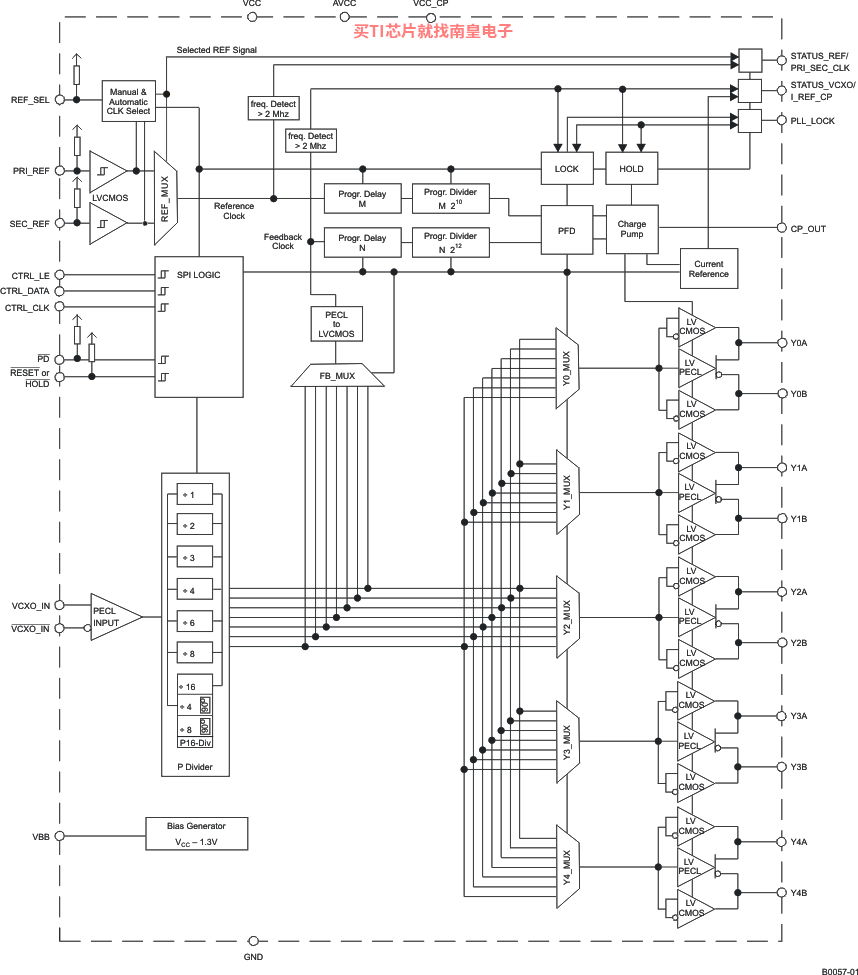

The CDCM7005 is a high-performance, low phase noise and low skew clock synchronizer that synchronizes a VCXO (voltage controlled crystal oscillator) or VCO (voltage controlled oscillator) frequency to one of the two reference clocks. The programmable pre-divider M and the feedback-dividers N and P give a high flexibility to the frequency ratio of the reference clock to VC(X)O

VC(X)O_IN clock operates up to 2.2 GHz. Through the selection of external VC(X)O and loop filter components, the PLL loop bandwidth and damping factor can be adjust to meet different system requirements.

The CDCM7005 can lock to one of two reference clock inputs (PRI_REF and SEC_REF), supports frequency hold-over mode and fast-frequency-locking for fail-safe and increased system redundancy. The outputs of the CDCM7005 are user definable and can be any combination of up to five LVPECL outputs or up to 10 LVCMOS outputs. The built in synchronization latches ensure that all outputs are synchronized for low output skew.

All device settings, like outputs signaling, divider value, and input selection are programmable by SPI (3-wire serial peripheral interface). SPI allows individually control of the device settings.

The device operates in 3.3-V environment and is characterized for operation from –40°C to 85°C.

- High Performance LVPECL and LVCMOS PLL Clock Synchronizer

- Two Reference Clock Inputs (Primary and Secondary Clock) for Redundancy Support With Manual or Automatic Selection

- Accepts LVCMOS Input Frequencies up to 200 MHz

- VCXO_IN Clock is Synchronized to One of the Two Reference Clocks

- VCXO_IN Frequencies Up to 2.2 GHz (LVPECL)

- Outputs Can Be a Combination of LVPECL and LVCMOS (Up to Five Differential LVPECL Outputs or up to 10 LVCMOS Outputs)

- Output Frequency is Selectable by ×1, /2, /3, /4, /6, /8, /16 on Each Output Individually

- Efficient Jitter Cleaning From Low PLL Loop Bandwidth

- Low Phase Noise PLL Core

- Programmable Phase Offset (PRI_REF and SEC_REF to Outputs)

- Wide Charge Pump Current Range From 200 A to 3 mA

- Dedicated Charge Pump Supply (VCC_CP) for Wide Tuning Voltage Range VCOs

- Presets Charge Pump to VCC_CP/2 for Fast Center-Frequency Setting of VC(X)O

- Analog and Digital PLL Lock Indication

- Provides VBB Bias Voltage Output for Single-Ended Input Signals (VCXO_IN)

- Frequency Hold-Over Mode Improves Fail-Safe Operation

- Power-up Control Forces LVPECL Outputs to 3-State at VCC < 1.5 V

- SPI Controllable Device Setting

- 3.3-V Power Supply

- Packaged in 64-Pin BGA (0.8 mm Pitch ZVA) or 48-Pin QFN (RGZ)

- Industrial Temperature Range 40°C to 85°C

- Function

- Single-loop PLL

- Number of outputs

- 5

- Output frequency (Min) (MHz)

- 0

- Output frequency (Max) (MHz)

- 1500

- Input type

- LVCMOS (REF_CLK), LVPECL (VCXO_CLK)

- Output type

- LVCMOS, LVPECL

- Supply voltage (Min) (V)

- 3

- Supply voltage (Max) (V)

- 3.6

- Features

- Programmable Delay

- Operating temperature range (C)

- -40 to 85

CDCM7005的完整型号有:CDCM7005RGZR、CDCM7005RGZT、CDCM7005ZVA、CDCM7005ZVAR、CDCM7005ZVAT,以下是这些产品的关键参数及官网采购报价:

CDCM7005RGZR,工作温度:-40 to 85,封装:VQFN (RGZ)-48,包装数量MPQ:2500个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:NIPDAU,TI官网CDCM7005RGZR的批量USD价格:8.778(1000+)

CDCM7005RGZT,工作温度:-40 to 85,封装:VQFN (RGZ)-48,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:NIPDAU,TI官网CDCM7005RGZT的批量USD价格:10.45(1000+)

CDCM7005ZVA,工作温度:-40 to 85,封装:BGA (ZVA)-64,包装数量MPQ:348个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:SNAGCU,TI官网CDCM7005ZVA的批量USD价格:10.45(1000+)

CDCM7005ZVAR,工作温度:-40 to 85,封装:BGA (ZVA)-64,包装数量MPQ:1000个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:SNAGCU,TI官网CDCM7005ZVAR的批量USD价格:8.778(1000+)

CDCM7005ZVAT,工作温度:-40 to 85,封装:BGA (ZVA)-64,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:SNAGCU,TI官网CDCM7005ZVAT的批量USD价格:10.45(1000+)

ADS5474EVM ADS5474 14 位 400-MSPS ADC 评估模块

ADS5474EVM 是能让设计者评估德州仪器 (TI) ADS5474 器件(14 位 400MSPS ADC)的电路板。借助提供的逻辑分析器输出板,可以使用 Agilent E5405A 或 Tektronix P6980 非接触式探针直接采集 ADC LVDS 输出。

CDC7005QFN-EVM 采用 QFN 封装的 CDC7005 评估模块

The CDC7005 is a high-performance, low phase noise and low skew clock synchronizer that synchronizes voltage controlled crystal oscillator (VCXO) frequency to an external reference clock; generates very low phase noise (jitter) clock.

The PLL loop bandwidth and damping factor can be adjusted to meet (...)

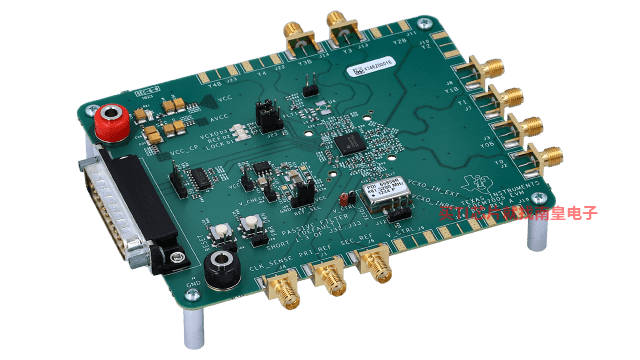

CDCM7005BGA-EVM 采用 BGA 封装的 CDCM7005 评估模块

The CDCM7005 is a high-performance, low phase noise and low skew clock synchronizer that synchronizes voltage controlled crystal oscillator (VCXO) frequency to an external reference clock; generates very low phase noise (jitter) clock.

The PLL loop bandwidth and damping factor can be adjusted to (...)

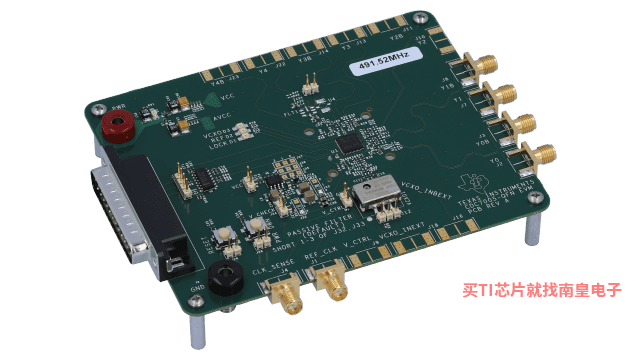

CDCM7005QFN-EVM 采用 QFN 封装的 CDCM7005 评估模块

TheCDCM7005QFN-EVM is an evaluation module designed to aid in evaluating the performance of the CDCM7005, which is a high-performance, low phase noise and low skew clock synchronizer that synchronizes voltage controlled crystal oscillator (VCXO) frequency to an external reference clock; generates (...)

DAC5688EVM DAC5688 评估模块

DAC5688EVM 是一块电路板,它允许设计人员评估具有宽带 LVDS 数据输入、集成 2x/4x/8x 内插滤波器、32 位 NCO 和内部参考电压的德州仪器 (TI) 双通道 16 位 800MSPS 数模转换器 (DAC)。EVM 提供了可在各种时钟、输入条件下测试 DAC5688 的灵活环境。

它能与 TSW3100 配合使用以执行各种测试程序。TSW3100 生成了测试模式,该模式将通过单行速度可达 250MSPS 的双路 CMOS 端口被馈送至 DAC5688。DAC5688EVM 具有可使 TSW3100 板与 DAC5688 同步的可编程时钟芯片。

CDCM7005 IBIS Model ZVA PKG With PKG Parasitics at 2GHz

PSpice for TI 可提供帮助评估模拟电路功能的设计和仿真环境。此功能齐全的设计和仿真套件使用 Cadence 的模拟分析引擎。PSpice for TI 可免费使用,包括业内超大的模型库之一,涵盖我们的模拟和电源产品系列以及精选的模拟行为模型。借助PSpice for TI 的设计和仿真环境及其内置的模型库,您可对复杂的混合信号设计进行仿真。创建完整的终端设备设计和原型解决方案,然后再进行布局和制造,可缩短产品上市时间并降低开发成本。

在PSpice for TI 设计和仿真工具中,您可以搜索 TI (...)

CDC-CDCM7005-CALC CDC7005 和 CDCM7005 PLL 环路带宽计算器

This tool helps to determine the right divider values (M, N & P) and to choose the filter type and components. This calculator will help to find out the appropriate loop bandwidth, phase margin, jitter peaking, etc. just varying the loop parameters like PFD frequency, filter components, Charge pump (...)CLOCK-TREE-ARCHITECT 时钟树架构编程软件

时钟树架构是一款时钟树综合工具,可根据您的系统要求生成时钟树解决方案,从而帮助您简化设计流程。该工具从庞大的时钟产品数据库中提取数据,然后生成系统级多芯片时钟解决方案。CDCM7005BGA EVM Gerber Files

各种应用(如激光安全扫描仪、测距仪、无人机和制导系统)中都利用了用于高精度测量距离的飞行时间 (ToF) 光学方法。该设计详述了基于高速数据转换器的解决方案的优点,包括目标识别、宽松的采样率要求和简化的信号链。该设计还解决了光学器件、驱动器和接收器前端电路、模数转换器 (ADC)、数模转换器 (DAC) 和信号处理。TIDA-00075 宽带宽和高电压任意波形发生器前端

此设计显示如何将活动接口用于 DAC5682Z 的电流接收器输出 - 这类典型应用包括任意波形发生器的前端。EVM 包括用于数模转换的 DAC5682Z、用于演示使用宽带宽运算放大器实现活动接口的 OPA695 以及用于展示具有大电压摆幅的运算放大器的 THS3091 和 THS3095。板上还包括用于生成时钟的 CDCM7005、VCXO 和基准以及用于电压调节的线性稳压器。通过 USB 接口和 GUI 软件实现与 EVM 的通信。