- ÷Τ‘λ≥ß…ΧΘΚTI

- ≤ζΤΖάύ±πΘΚΫ”ΩΎ

- ΦΦ θάύΡΩΘΚ“‘ΧΪΆχ IC - “‘ΧΪΆχ PHY

- ΙΠΡήΟη ωΘΚ≤…”Ο–Γ–Ά QFN ΖβΉΑΒΡΒΆΙΠΚΡΓΔΡΆ”Ο–Ά«ß’Ή“‘ΧΪΆχ PHY ’ΖΔΤς

- ΒψΜς’βάο¥ρΩΣΦΑœ¬‘ΊDP83867CRΒΡΦΦ θΈΡΒΒΉ Νœ

- TI¥ζάμ«ΰΒάΘ§ΧαΙ©Β±»’ΖΔΜθΓΔ―œΗώΒΡ÷ ΝΩ±ξΉΦΘ§¬ζΉψΡζΒΡΡΩ±ξΦέΗώ

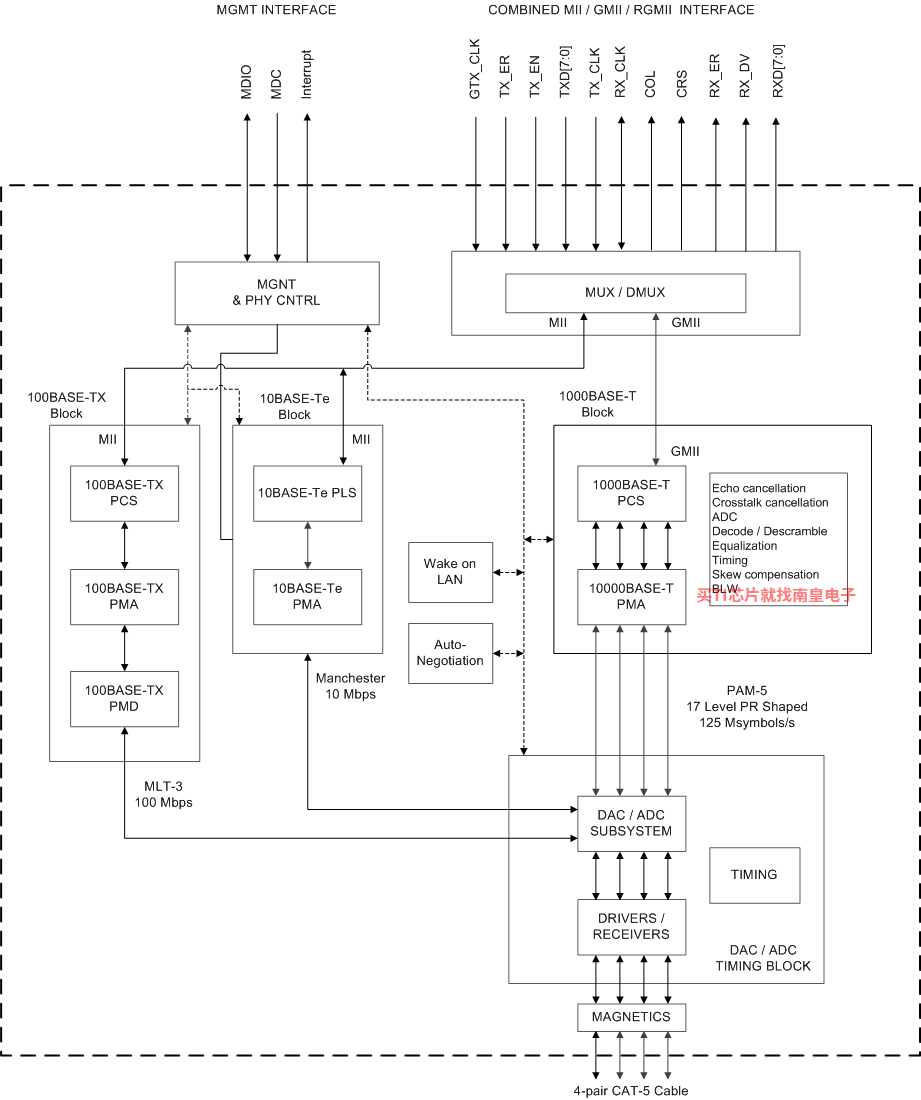

DP83867 ΤςΦΰ «“ΜΩνΈ»ΫΓΡΆ”Ο–ΆΒΆΙΠΚΡ»ΪΙΠΡήΈοάμ≤ψ ’ΖΔΤςΘ§ΥϋΦ·≥…ΝΥ PMD Ή”≤ψ“‘÷ß≥÷ 10BASE-TeΓΔ100BASE-TX ΚΆ 1000BASE-T “‘ΧΪΆχ–≠“ιΓΘDP83867 Ψ≠”≈Μ·Ω…ΧαΙ© ESD ±ΘΜΛΘ§≥§ΙΐΝΥ 8kV IEC 61000-4-2 ±ξΉΦΘ®÷±Ϋ”Ϋ”¥ΞΘ©ΓΘ

DP83867 Ω…«αΥ… Βœ÷ 10/100/1000Mbps “‘ΧΪΆχ LANΓΘΥϋΆ®ΙΐΆβ≤Ω±δ―ΙΤς÷±Ϋ”Ν§Ϋ”ΥΪΫ œΏΫι÷ ΓΘΗΟΤςΦΰΆ®Ιΐ IEEE 802.3 ±ξΉΦ MIIΓΔIEEE 802.3 GMII Μρ RGMII ÷±Ϋ””κ MAC ≤ψœύΝ§ΓΘQFP ΖβΉΑ÷ß≥÷ MII/GMII/RGMIIΘ§Εχ QFN ΖβΉΑ÷ß≥÷ RGMIIΓΘ

DP83867 ΧαΙ©ΨΪ»Ζ ±÷”Ά§≤ΫΘ§Τδ÷–Αϋά®Ά§≤Ϋ“‘ΧΪΆχ ±÷” δ≥ωΓΘΗΟΤςΦΰΨΏ”–ΒΆ―”≥ΌΘ§≤ΔΧαΙ© IEEE 1588 ÷ΓΤπ ΦΦλ≤βΓΘ

DP83867 ΫωœϊΚΡ 490mW (PAP)ΚΆ 457mW (RGZ)Θ®¬ζΙΠ¬ ‘Υ–– ±Θ©ΓΘΨ÷”ρΆχΜΫ–―Ω…”Ο”ΎΫΒΒΆœΒΆ≥ΙΠΚΡΓΘ

- ≥§ΒΆΦρΜ·ΒΡ«ß’ΉΫι÷ ΈόΙΊΫ”ΩΎ (RGMII) ―”≥ΌΘΚTX < 90nsΘ§RX < 290ns

- ΒΆΙΠΚΡΘΚ457mW ÷–ΒΡΙΠΚΡ ΐΉ÷

- ≥§≥ωΝΥ 8000V IEC 61000-4-2 Ψ≤ΒγΖ≈Βγ (ESD) ±ΘΜΛΒ»ΦΕ

- ΖϊΚœ EN55011 B άύΖχ…δ±ξΉΦ

- ‘Ύ RX/TX …œΧαΙ© 16 ÷÷Ω…±ύ≥Χ RGMII ―”≥ΌΡΘ Ϋ

- Φ·≥… MDI ΕΥΫ”ΒγΉη÷–ΒΡ MDI ΕΥΫ”ΒγΉη

- Ω…±ύ≥Χ MII/GMII/RGMII ΕΥΫ”ΉηΩΙ÷–ΒΡΩ…±ύ≥Χ MAC Ϋ”ΩΎΕΥΫ”ΉηΩΙ

- WoLΘ®Ψ÷”ρΆχΜΫ–―Θ© ΐΨίΑϋΦλ≤β

- 25MHz Μρ 125MHz Ά§≤Ϋ ±÷” δ≥ω

- ÷ß≥÷ IEEE 1588 ±Φδ¥Ν

- RJ45 ΨΒœώΡΘ Ϋ

- ”κ IEEE 802.3 10BASE-TeΓΔ100BASE-TX ΚΆ 1000BASE-T ΙφΖΕΆξ»ΪΦφ»ί

- Βγά¬’οΕœ

- ’ΉΈΜΫι÷ ΈόΙΊΫ”ΩΎ (MII)ΓΔ«ß’ΉΈΜΫι÷ ΈόΙΊΫ”ΩΎ (GMII) ΚΆ RGMII Ϋι÷ ΖΟΈ ΩΊ÷Τ (MAC) Ϋ”ΩΎ―Γœν

- Ω…≈δ÷Ο I/O Βγ―ΙΘ®3.3VΓΔ2.5VΓΔ1.8VΘ©

- ΩλΥΌΝ¥¬ΖΫ®ΝΔ/ΕœΩΣΡΘ Ϋ

- JTAG ÷ß≥÷

- Datarate (Mbps)

- 10/100/1000

- Interface type

- RGMII

- Number of ports

- Single

- Rating

- Catalog

- Features

- Cable diagnostics, IEEE 1588 SOF, JTAG1149.1

- Supply voltage (V)

- 1 and 2.5

- IO supply (Typ) (V)

- 1.8, 2.5, 3.3

- Operating temperature range (C)

- 0 to 70

- Cable length (m)

- 130

DP83867CRΒΡΆξ’ϊ–ΆΚ≈”–ΘΚDP83867CRRGZRΓΔDP83867CRRGZTΘ§“‘œ¬ «’β–©≤ζΤΖΒΡΙΊΦϋ≤Έ ΐΦΑΙΌΆχ≤…ΙΚ±®ΦέΘΚ

DP83867CRRGZRΘ§ΙΛΉςΈ¬Ε»ΘΚ0 to 70Θ§ΖβΉΑΘΚVQFN (RGZ)-48Θ§ΑϋΉΑ ΐΝΩMPQΘΚ2500ΗωΘ§MSL Β»ΦΕ/ΜΊΝςΚΗΖε÷ΒΈ¬Ε»ΘΚLevel-3-260C-168 HRΘ§“ΐΫ≈ΕΤ≤ψ/ΚΗ«ρ≤ΡΝœΘΚNIPDAUΘ§TIΙΌΆχDP83867CRRGZRΒΡ≈ζΝΩUSDΦέΗώΘΚ2.565Θ®1000+Θ©

DP83867CRRGZTΘ§ΙΛΉςΈ¬Ε»ΘΚ0 to 70Θ§ΖβΉΑΘΚVQFN (RGZ)-48Θ§ΑϋΉΑ ΐΝΩMPQΘΚ250ΗωΘ§MSL Β»ΦΕ/ΜΊΝςΚΗΖε÷ΒΈ¬Ε»ΘΚLevel-3-260C-168 HRΘ§“ΐΫ≈ΕΤ≤ψ/ΚΗ«ρ≤ΡΝœΘΚNIPDAUΘ§TIΙΌΆχDP83867CRRGZTΒΡ≈ζΝΩUSDΦέΗώΘΚ3.078Θ®1000+Θ©

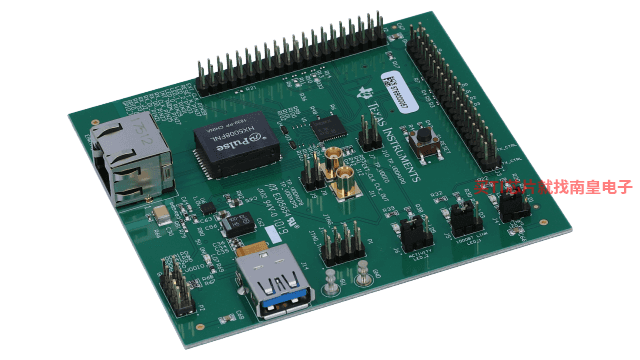

DP83867ERGZ-R-EVM ΓΣ DP83867ERGZ-R-EVM RGMII 1000M/100M/10M “‘ΧΪΆχΈοάμ≤ψΤάΙάΡΘΩι

DP83867ERGZ-R-EVM ÷ß≥÷ 1000/100/10BASE ≤Δ«“ΖϊΚœ IEEE 802.3 ±ξΉΦΓΘ¥Υ≤ΈΩΦ…ηΦΤ÷ß≥÷ RGMII MAC Ϋ”ΩΎΓΘ

DP83867 EVM Αϋά®»ΐΗωΑε‘ΊΉ¥Χ§ LEDΓΔ5V Ν§Ϋ”Τς“‘ΦΑΑε‘Ί LDOΘ§≤Δ«“Ω…Ά®Ιΐ JTAG ΖΟΈ ΓΘDP83867 EVM ΡήΙΜ¥”Αε‘Ί 25MHz ΨßΧεΧαΙ©“ΜΗω 125MHz ≤ΈΩΦ ±÷”ΓΘ¥°––ΙήάμΫ”ΩΎ MDIO/MDC ήΒΫ÷ß≥÷Θ§≤Δ«“Ω…”Ο”ΎΖΟΈ PHY ΦΡ¥φΤς“‘ Βœ÷ΗϋΕύΙΠΡήΓΘ¥ΥΤάΙάΡΘΩιΧαΙ© 4 ΦΕ¥νΫ”Θ§“ρ¥ΥΈό–η÷±Ϋ”ΖΟΈ PHY ΦΡ¥φΤς±ψΩ…Ϋχ––œΒΆ≥≈δ÷ΟΓΘΆβ≤ΩΒγ‘¥Ω…Ν§Ϋ”ΒΫΗςΗω÷ΗΕ®Βγ―ΙΙλ“‘Ϋχ––Ϋχ“Μ≤ΫœΒΆ≥ΤάΙάΓΘDP83867 EVM (...)

USB-2-MDIO ΓΣ USB ΉΣ MDIO ¥°––ΙήάμΙΛΨΏ

άϊ”Ο USB ΉΣ MDIO »μΦΰΙΛΨΏΘ§Β¬÷ί“«Τς (TI) “‘ΧΪΆχ PHY ΒΡ”ΟΜßΩ…“‘ΖΟΈ MDIO Ή¥Χ§ΚΆΩΊ÷ΤΦΡ¥φΤςΓΘUSB ΉΣ MDIO ΙΛΨΏΑϋΚ§Ν§Ϋ”÷Ν«αΝΩΦΕ GUI ΒΡ MSP430 LaunchPadΓΘ¥Υ LaunchPad Βœ÷ΝΥ“ΜΗω MDIO ΉήœΏΩΊ÷ΤΤςΘ§ΗΟΩΊ÷ΤΤςΩ…“‘≤ΌΉςΝ§Ϋ”ΒΫΉήœΏΒΡ PHY …œΒΡΦΡ¥φΤςΓΘETHERNET-SW ΓΣ “‘ΧΪΆχ PHY Linux «ΐΕ·ΤςΚΆΙΛΨΏ

Β¬÷ί“«Τς (TI) “‘ΧΪΆχΈοάμ≤ψ ’ΖΔΤς (PHY) Linux «ΐΕ·≥Χ–ρ÷ß≥÷Ά®Ιΐ¥°––ΙήάμΫ”ΩΎ (MDC/MDIO) Ϋχ––Ά®–≈Θ§“‘≈δ÷ΟΚΆΕΝ»Γ PHY ΦΡ¥φΤςΓΘ¥Υ USB-2-MDIO »μΦΰ‘ΎΒς ‘ΚΆ‘≠–Ά…ηΦΤΤΎΦδΩ… Βœ÷÷±Ϋ”ΦΡ¥φΤςΖΟΈ ΓΘ ¥ΥΙΛΨΏ÷ß≥÷Υυ”– TI “‘ΧΪΆχ PHYΓΘ

Ττ”Ο«ΐΕ·≥Χ–ρ÷ß≥÷Ι”ΟΓΑmake menuconfigΓ±Θ®“≤Ω…“‘ Ι”ΟΓΑmake xconfigΓ±ΜρΓΑmake nconfigΓ±Θ©≈δ÷ΟΡΎΚΥ

Menuconfig ΈΜ÷Ο//ΗϋΗΡ“‘œ¬ Ψάΐ÷–ΒΡΖϊΚ≈Ή÷ΕΈ“‘ΤΞ≈δ≤ΩΦΰΚ≈

ΖϊΚ≈ΘΚDP83848_PHY [=y]

άύ–ΆΘΚtristate

Χα ΨΘΚΒ¬÷ί“«Τς (TI) DP83848 PHY «ΐΕ·≥Χ–ρ

ΈΜ÷ΟΘΚ

(...)

DP83867IR IBIS Model (Rev. A)

PSpice for TI Ω…ΧαΙ©Αο÷ζΤάΙάΡΘΡβΒγ¬ΖΙΠΡήΒΡ…ηΦΤΚΆΖ¬’φΜΖΨ≥ΓΘ¥ΥΙΠΡήΤκ»ΪΒΡ…ηΦΤΚΆΖ¬’φΧΉΦΰ Ι”Ο Cadence ΒΡΡΘΡβΖ÷Έω“ΐ«φΓΘPSpice for TI Ω…ΟβΖ― Ι”ΟΘ§Αϋά®“ΒΡΎ≥§¥σΒΡΡΘ–ΆΩβ÷°“ΜΘ§Κ≠Η«Έ“Ο«ΒΡΡΘΡβΚΆΒγ‘¥≤ζΤΖœΒΝ–“‘ΦΑΨΪ―ΓΒΡΡΘΡβ––ΈΣΡΘ–ΆΓΘΫη÷ζ?PSpice for TI ΒΡ…ηΦΤΚΆΖ¬’φΜΖΨ≥ΦΑΤδΡΎ÷ΟΒΡΡΘ–ΆΩβΘ§ΡζΩ…Ε‘Η¥‘”ΒΡΜλΚœ–≈Κ≈…ηΦΤΫχ––Ζ¬’φΓΘ¥¥Ϋ®Άξ’ϊΒΡ÷’ΕΥ…η±Η…ηΦΤΚΆ‘≠–ΆΫβΨωΖΫΑΗΘ§»ΜΚσ‘ΌΫχ––≤ΦΨ÷ΚΆ÷Τ‘λΘ§Ω…ΥθΕΧ≤ζΤΖ…œ – ±Φδ≤ΔΫΒΒΆΩΣΖΔ≥…±ΨΓΘ

‘Ύ?PSpice for TI …ηΦΤΚΆΖ¬’φΙΛΨΏ÷–Θ§ΡζΩ…“‘Υ―Υς TI (...)

TINA-TI ΓΣ Μυ”Ύ SPICE ΒΡΡΘΡβΖ¬’φ≥Χ–ρ

TINA-TI ΧαΙ©ΝΥ SPICE Υυ”–ΒΡ¥ΪΆ≥÷±ΝςΓΔΥ≤Χ§ΚΆΤΒ”ρΖ÷Έω“‘ΦΑΗϋΕύΓΘTINA ΨΏ”–ΙψΖΚΒΡΚσ¥ΠάμΙΠΡήΘ§‘ –μΡζΑ¥’’œΘΆϊΒΡΖΫ Ϋ…η÷ΟΫαΙϊΒΡΗώ ΫΓΘ–ιΡβ“«Τς‘ –μΡζ―Γ‘ώ δ»κ≤®–ΈΓΔΧΫ’κΒγ¬ΖΫΎΒψΒγ―ΙΚΆ≤®–ΈΓΘTINA ΒΡ‘≠άμΆΦ≤ΕΜώΖ«≥Θ÷±Ιέ - ’φ’ΐΒΡΓΑΩλΥΌ»κΟ≈Γ±ΓΘTINA-TI Α≤ΉΑ–η“Σ¥σ‘Φ 500MBΓΘ÷±Ϋ”Α≤ΉΑΘ§»γΙϊœκ–Ε‘Ί“≤Κή»ί“ΉΓΘΈ“Ο«œύ–≈ΡζΩœΕ®ΜαΑ°≤Μ Ά ÷ΓΘ

TINA «Β¬÷ί“«Τς (TI) Ή®”–ΒΡ DesignSoft ≤ζΤΖΓΘΗΟΟβΖ―Αφ±ΨΨΏ”–Άξ’ϊΒΡΙΠΡήΘ§ΒΪ≤Μ÷ß≥÷Άξ’ϊΑφ TINA ΥυΧαΙ©ΒΡΡ≥–©ΤδΥϊΙΠΡήΓΘ

»γ–ηΜώ»ΓΩ…”Ο TINA-TI ΡΘ–ΆΒΡΆξ’ϊΝ–±μΘ§«κ≤Έ‘ΡΘΚSpiceRack - Άξ’ϊΝ–±μ

–η“Σ HSpice (...)

TIDA-050034 ΓΣ Integrated power supply reference design for NXP iMX 7D processor

TIDA-050034 is a fully functional development board combining a TI PMIC, TPS65218DO, with NXP i.MX 7Dual Application Processor.The hardware design consists of DDR3L SDRAM (2x512MB), 64MB Serial NOR Flash, 8GB eMMC 5.0 iNAND, SD Card interface v3.0, 50 pin LCD Connector for external TFT display (...)

TIDEP-01008 ΓΣ Jacinto ADAS ¥ΠάμΤς…œΒΡΕύ¥ΪΗ–ΤςΤΫΧ®≤ΈΩΦ…ηΦΤ

D3 Engineering ΒΡΗΏΦΕΦί Μ‘±Η®÷ζœΒΆ≥ (ADAS) ΒΡΕύ¥ΪΗ–ΤςΤΫΧ®≤ΈΩΦ…ηΦΤΈΣΚœΗώΒΡΩΣΖΔ»Υ‘±ΧαΙ©ΝΥ“ΜΗωΙΠΡήΤκ»ΪΒΡΤάΙάΤΫΧ®Θ§±ψ”ΎΫχ––÷ς“ΣΟφœρΤϊ≥Β––“ΒΒΡ ADAS ”Π”ΟΒΡ≤β ‘ΚΆΩΣΖΔΓΘD3 ΜΙΧαΙ©ΡΘΩιΜ·œΒΆ≥ (SOM) ΫβΨωΖΫΑΗΘ§Τδ÷–ΑϋΚ§Ω…”κ¥Υ≤ΈΩΦ…ηΦΤ≈δΚœ Ι”ΟΒΡ ADAS «Ε»κ Ϋ¥ΠάμΤςΘ®άΐ»γ TDA3xΘ©ΓΘά¥Ή‘ D3 ΒΡ DesignCore TDA3x Τϊ≥Β»κΟ≈ΧΉΦΰ

TIDA-00204 ΓΣ ΖϊΚœ EMI/EMC ±ξΉΦΒΡΙΛ“ΒΈ¬Ε»ΦΕΥΪΕΥΩΎ«ß’ΉΈΜ“‘ΧΪΆχ≤ΈΩΦ…ηΦΤ

¥Υ…ηΦΤ”Ο”ΎΕ‘ΝΫΗωΙΛ“ΒΦΕ DP83867IR «ß’ΉΈΜ“‘ΧΪΆχ PHY ΚΆ Sitara ÷ςΜζ¥ΠάμΤςΘ®Κ§Φ·≥… Ϋ“‘ΧΪΆχ MAC ΚΆΫΜΜΜΜζΘ©Ϋχ–––‘ΡήΤάΙάΓΘ¥Υ…ηΦΤ÷Φ‘Ύ¬ζΉψΙΊ”Ύ EMI ΚΆ EMC ΒΡΙΛ“Β“Σ«σΓΘ¥Υ…ηΦΤΒΡ”Π”ΟΙΧΦΰ Βœ÷ΝΥ ”Ο”Ύ PHYΓΔUDP ΚΆ TCP/IP –≠“ι’Μ“‘ΦΑ HTTP Web ΖΰΈώΤς ΨάΐΒΡ«ΐΕ·≥Χ–ρΓΘ÷ςΜζ¥ΠάμΤς≈δ÷ΟΈΣ¥”Αε‘Ί SD Ω®“ΐΒΦ‘ΛΉΑΒΡΙΧΦΰΓΘΆ®Ιΐ USB –ιΡβ COM ΕΥΩΎΩ…ΖΟΈ PHY ΦΡ¥φΤςΓΘΆ®Ιΐ JTAG Ϋ”ΩΎΩ…Ϋχ––Ή‘ΦΚΒΡΙΧΦΰΩΣΖΔΓΘ