- 制造厂商:TI

- 产品类别:接口

- 技术类目:LVDS、M-LVDS 和 PECL IC

- 功能描述:汽车类 LVDS 双路差动线路接收器

- 点击这里打开及下载DS90LV028AQ-Q1的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

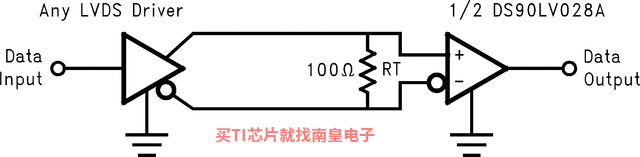

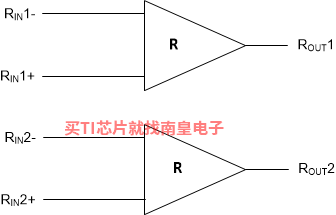

DS90LV028AQ 是一款双路 CMOS 差动线路接收器,专为 需要超低功率耗散、低噪声和高数据速率的 应用而设计。该器件旨在利用低电压差动信号 (LVDS) 技术支持超过 400Mbps (200MHz) 的数据速率。

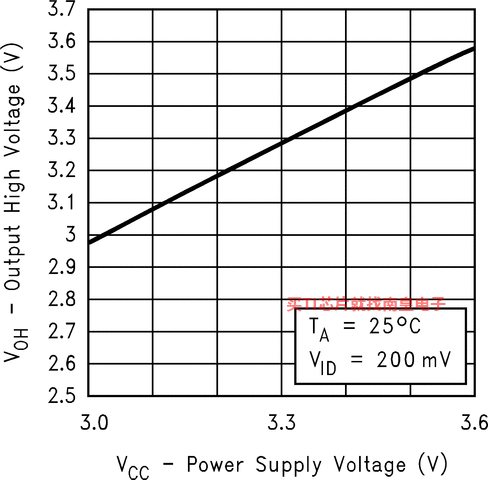

DS90LV028AQ 可接受低电压(350mV 典型值)差动输入信号,并将其转换为 3V CMOS 输出电平。DS90LV028AQ 采用了直通式设计,可简化 PCB 布局。

DS90LV028AQ 和配套的 LVDS 线路驱动器 DS90LV027AQ 可为高速点对点接口应用提供高功率 PECL/ECL 器件作为新的 替代产品。

- 符合面向汽车应用的 AECQ-100 标准

- 温度等级 1:-40°C 至 +125°C TA

- >400Mbps (200MHz) 的开关速率

- 50ps 差动偏斜(典型值)

- 0.1ns 通道到通道偏斜(典型值)

- 2.5ns 最大传播延迟

- 3.3V 电源设计

- 直通引脚

- 在断电模式下,LVDS 输入端具有高阻抗

- 低功耗设计(3.3V 静态条件下为 18mW)

- LVDS 输入可接受 LVDS/CML/LVPECL 信号

- 符合 ANSI/TIA/EIA-644 标准

- 采用 SOIC 封装

- Function

- Receiver

- Protocols

- LVDS

- Number of transmitters

- 0

- Number of receivers

- 2

- Supply voltage (V)

- 3.3

- Signaling rate (Mbps)

- 400

- Input signal

- LVDS

- Output signal

- TTL, LVTTL

- Rating

- Automotive

- Operating temperature range (C)

- -40 to 125

DS90LV028AQ-Q1的完整型号有:DS90LV028AQMA/NOPB、DS90LV028AQMAX/NOPB,以下是这些产品的关键参数及官网采购报价:

DS90LV028AQMA/NOPB,工作温度:-40 to 125,封装:SOIC (D)-8,包装数量MPQ:95个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:SN,TI官网DS90LV028AQMA/NOPB的批量USD价格:.817(1000+)

DS90LV028AQMAX/NOPB,工作温度:-40 to 125,封装:SOIC (D)-8,包装数量MPQ:2500个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:SN,TI官网DS90LV028AQMAX/NOPB的批量USD价格:.699(1000+)

DS90LV027A-28AEVM ― 双通道 LVDS 驱动器和接收器评估模块

The DS90LV027A-28A is an evaluation module designed for performance and functional evaluation of the Texas Instruments DS90LV027A LVDS dual differential driver and DS90LV028A LVDS dual differential line receiver. With this kit, users can quickly evaluate the output waveform characteristics (...)DS90LV028A IBIS Model

PSpice for TI 可提供帮助评估模拟电路功能的设计和仿真环境。此功能齐全的设计和仿真套件使用 Cadence 的模拟分析引擎。PSpice for TI 可免费使用,包括业内超大的模型库之一,涵盖我们的模拟和电源产品系列以及精选的模拟行为模型。借助?PSpice for TI 的设计和仿真环境及其内置的模型库,您可对复杂的混合信号设计进行仿真。创建完整的终端设备设计和原型解决方案,然后再进行布局和制造,可缩短产品上市时间并降低开发成本。

在?PSpice for TI 设计和仿真工具中,您可以搜索 TI (...)

TINA-TI ― 基于 SPICE 的模拟仿真程序

TINA-TI 提供了 SPICE 所有的传统直流、瞬态和频域分析以及更多。TINA 具有广泛的后处理功能,允许您按照希望的方式设置结果的格式。虚拟仪器允许您选择输入波形、探针电路节点电压和波形。TINA 的原理图捕获非常直观 - 真正的“快速入门”。TINA-TI 安装需要大约 500MB。直接安装,如果想卸载也很容易。我们相信您肯定会爱不释手。

TINA 是德州仪器 (TI) 专有的 DesignSoft 产品。该免费版本具有完整的功能,但不支持完整版 TINA 所提供的某些其他功能。

如需获取可用 TINA-TI 模型的完整列表,请参阅:SpiceRack - 完整列表

需要 HSpice (...)

TIDA-01022 ― 适用于 DSO、雷达和 5G 无线测试系统的灵活 3.2GSPS 多通道 AFE 参考设计

此高速多通道数据采集参考设计可实现最佳的系统性能。系统设计人员需要考虑关键的设计参数,如高速多通道时钟生成功能的时钟抖动和偏斜(这会影响整个系统的 SNR、SFDR、通道间偏斜和确定性延迟)。此参考设计演示了一种多通道 AFE 和时钟解决方案,采用具有 JESD204B 的高速数据转换器、高速放大器、高性能时钟和低噪声电源解决方案,可实现最佳的系统性能TIDA-010122 ― 同步多通道射频系统数据转换器 DDC 和 NCO 特性的参考设计

由于 5G 的兴起,大规模多输入多输出 (mMIMO)、相控阵雷达和通信有效载荷等应用需要进行相应的调整,由此带来了同步设计挑战,该参考设计可解决这些挑战。典型射频前端包括模拟域中的天线、低噪声放大器 (LNA)、混频器、本机振荡器 (LO),以及数字域中的模数转换器、数字控制振荡器 (NCO) 和数字下变频器 (DDC)。要实现总体系统同步,这些数字块需要与系统时钟进行同步。该参考设计使用 ADC12DJ3200 数据转换器,通过将片上 NCO 与 SYNC~ 进行同步获得确定性延迟,以此在多个接收器上实现小于 5ps 的通道间偏移,并使用无噪声孔径延迟调节(tAD (...)TIDA-010132 ― 适用于雷达和电子战应用的多通道射频收发器参考设计

该参考设计展示了一款 8 通道模拟前端 (AFE),它使用了两个 AFE7444 4 通道射频收发器和基于 LMK04828-LMX2594 的时钟子系统,该子系统可支持将设计扩展至 16 通道或更多通道。每个 AFE 通道都包含 14 位 9GSPS DAC 和 3GSPS ADC,该 ADC 可在 2.6GHz 下同步至低于 10ps 偏移并且动态范围大于 75dB。TIDA-010128 ― 适用于 12 位数字转换器的可扩展 20.8GSPS 参考设计

此参考设计介绍采用时序交错配置射频采样模数转换器 (ADC) 的 20.8GSPS 采样系统。时序交错法是一种经实践检验可提高采样率的传统方法,然而,匹配个别 ADC 失调电压、增益和采样时间不匹配是实现性能的关键。随着采样时钟频率的增加,交错复杂性也随之增加。ADC 之间的相位匹配是实现更出色的 SFDR 和 ENOB 的关键规格之一。本参考设计通过采用简化 20.8GSPS 交错实施的 19fs 精确相位控制措施,在 ADC12DJ5200RF 上应用了无噪声孔径延迟调节功能。本参考设计基于符合 12 位系统性能要求的 LMK04828 和 LMX2594,采用了板载低噪声 (...)TIDA-01028 ― 适用于高速示波器和宽带数字转换器的 12.8-GSPS 模拟前端参考设计

此参考设计提供了一个用于实现 12.8GSPS 采样率的交错射频采样模数转换器 (ADC) 的实用示例。这可通过对两个射频采样 ADC 进行时序交错来实现。交错需要在 ADC 之间进行相移,此参考设计通过 ADC12DJ3200 的无噪声孔径延迟调节(tAD 调节)功能来实现相移。此功能还可用于最大限度地减少交错 ADC 常见的失配问题:最大程度地提升 SNR、ENOB 和 SFDR 性能。此参考设计还采用了支持 JESD204B 的低相位噪声时钟树,该时钟树通过 LMX2594 宽带 PLL、LMK04828 合成器以及抖动清除器来实现。TIDA-01027 ― 可最大限度提升 12.8GSPS 数据采集系统性能的低噪声电源参考设计

此参考设计显示了适用于能超过 12.8GSPS 的极高速 DAQ 系统的高效率、低噪声 5 轨电源设计。该电源的直流/直流转换器进行了频率同步和相移,从而使输入电流纹波最小并控制频率成分。此外,它还使用高性能 HotRod封装技术将任何潜在的辐射电磁干扰 (EMI) 降到了最低。TIDA-010131 ― 适用于雷达和无线 5G 测试仪的多通道射频收发器时钟参考设计

相控阵雷达、无线通信测试仪和电子战等高速终端设备的模拟前端需要同步的多收发器信号链。每个收发器信号链都包括高速模数转换器 (ADC)、数模转换器 (DAC) 和时钟子系统。时钟子系统提供低噪声采样时钟,具备精细的延迟调节功能,可实现最低的通道间偏差和最佳的系统性能,如信噪比 (SNR)、无杂散动态范围 (SFDR)、IMD3 和有效位数 (ENOB) 等。此参考设计通过 AFE7444 EVM 展示了多通道 JESD204B 时钟生成和系统性能。通过高达 2.6GHz 射频的 6GSPS/3GSPS DAC/ADC 时钟实现的优于 10ps 的通道间偏差以及 SNR 和 SFDR (...)TIDA-01021 ― 适用于 DSO、雷达和 5G 无线测试仪的多通道 JESD204B 15GHz 时钟参考设计

High speed multi-channel applications require precise clocking solutions capable of managing channel-to-channel skew in order to achieve optimal system SNR, SFDR, and ENOB. This reference design is capable of supporting two high speed channels on separate boards by utilizing TI’s LMX2594 (...)TIDA-01024 ― 适用于雷达和 5G 无线测试仪的高通道数 JESD204B 菊链时钟参考设计

高速多通道应用需要低噪声、可扩展且可进行精确通道间偏斜调节的时钟解决方案,以实现最佳系统 SNR、SFDR 和 ENOB。此参考设计支持在菊链配置中增加 JESD204B 同步时钟。此设计可提供多通道 JESD204B 时钟,采用 TI LMK04828 时钟抖动清除器和带有集成式 VCO 的 LMX2594 宽带 PLL,能够实现低于 10ps 的时钟间偏斜。此设计经过 TI ADC12DJ3200 EVM 在 3GSPS 环境中检测,具有改善的 SNR 性能,通道间偏斜低于 (...)TIDA-01023 ― 适用于雷达和 5G 无线测试仪的高通道数 JESD204B 时钟生成参考设计

高速多通道应用需要低噪声、可扩展且可进行精确通道间偏差调节的时钟解决方案,以实现最佳系统 SNR、SFDR 和 ENOB。此参考设计使用一个主时钟器件和多个从时钟器件,支持高通道数 JESD204B 同步时钟。此设计可提供多通道 JESD204B 时钟,采用 TI LMK04828 时钟抖动清除器和带有集成式 VCO 的 LMX2594 宽带 PLL,能够实现低于 10ps 的时钟间偏差。此设计经过 TI ADC12DJ3200 EVM 在 3GSPS 环境中检测,具有改善的 SNR 性能,通道间偏差低于 (...)