- 制造厂商:TI

- 产品类别:接口

- 技术类目:其他接口

- 功能描述:3MHz 至 40MHz 直流平衡 24 位 LVDS 串行器

- 点击这里打开及下载DS99R105的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

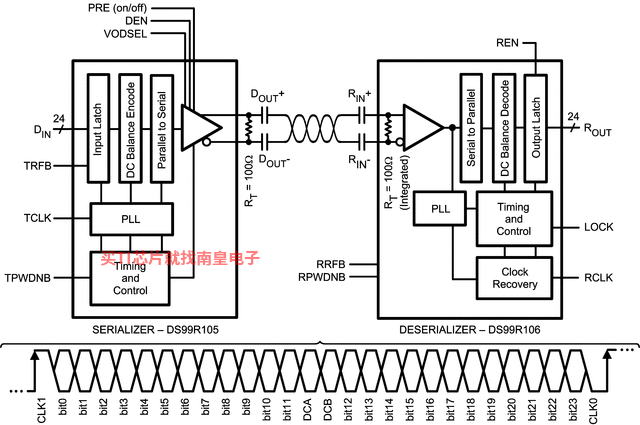

The DS99R105/DS99R106 Chipset translates a 24-bit parallel bus into a fully transparent data/control LVDS serial stream with embedded clock information. This single serial stream simplifies transferring a 24-bit bus over PCB traces and cable by eliminating the skew problems between parallel data and clock paths. It saves system cost by narrowing data paths that in turn reduce PCB layers, cable width, and connector size and pins.

The DS99R105/DS99R106 incorporates LVDS signaling on the high-speed I/O. LVDS provides a low power and low noise environment for reliably transferring data over a serial transmission path. By optimizing the serializer output edge rate for the operating frequency range EMI is further reduced.

In addition the device features pre-emphasis to boost signals over longer distances using lossy cables. Internal DC balanced encoding/decoding is used to support AC-Coupled interconnects.

- 3 MHz–40 MHz Clock Embedded and DC-Balancing 24:1 and 1:24 Data Transmissions

- Capable to Drive Shielded Twisted-Pair Cable

- User Selectable Clock Edge for Parallel Data on Both Transmitter and Receiver

- Internal DC Balancing Encode/Decode – Supports AC-Coupling Interface with no External Coding Required

- Individual Power-Down Controls for Both Transmitter and Receiver

- Embedded Clock CDR (Clock and Data Recovery) on Receiver and no External Source of Reference Clock Needed

- All Codes RDL (Random Data Lock) to Support Live-Pluggable Applications

- LOCK Output Flag to Ensure Data Integrity at Receiver Side

- Balanced TSETUP/THOLD between RCLK and RDATA on Receiver Side

- PTO (Progressive Turn-On) LVCMOS Outputs to Reduce EMI and Minimize SSO Effects

- All LVCMOS Inputs and Control Pins have Internal Pulldown

- On-Chip Filters for PLLs on Transmitter and Receiver

- Integrated 100? Input Termination on Receiver

- 4 mA Receiver Output Drive

- 48-Pin TQFP and 48-Pin WQFN Packages

- Pure CMOS .35 μm Process

- Power Supply Range 3.3V ± 10%

- Temperature Range 0°C to +70°C

- 8 kV HBM ESD Tolerance

All trademarks are the property of their respective owners.

- Operating temperature range (C)

- 0 to 70

DS99R105的完整型号有:DS99R105SQ/NOPB、DS99R105SQX/NOPB、DS99R105VS/NOPB,以下是这些产品的关键参数及官网采购报价:

DS99R105SQ/NOPB,工作温度:0 to 70,封装:WQFN (NJU)-48,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-2-260C-1 YEAR,引脚镀层/焊球材料:SN,TI官网DS99R105SQ/NOPB的批量USD价格:4.118(1000+)

DS99R105SQX/NOPB,工作温度:0 to 70,封装:WQFN (NJU)-48,包装数量MPQ:2500个,MSL 等级/回流焊峰值温度:Level-2-260C-1 YEAR,引脚镀层/焊球材料:SN,TI官网DS99R105SQX/NOPB的批量USD价格:3.432(1000+)

DS99R105VS/NOPB,工作温度:0 to 70,封装:TQFP (PFB)-48,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:SN,TI官网DS99R105VS/NOPB的批量USD价格:4.393(1000+)

PSPICE-FOR-TI — 适用于 TI 设计和模拟工具的 PSpice

PSpice for TI 可提供帮助评估模拟电路功能的设计和仿真环境。此功能齐全的设计和仿真套件使用 Cadence 的模拟分析引擎。PSpice for TI 可免费使用,包括业内超大的模型库之一,涵盖我们的模拟和电源产品系列以及精选的模拟行为模型。借助?PSpice for TI 的设计和仿真环境及其内置的模型库,您可对复杂的混合信号设计进行仿真。创建完整的终端设备设计和原型解决方案,然后再进行布局和制造,可缩短产品上市时间并降低开发成本。

在?PSpice for TI 设计和仿真工具中,您可以搜索 TI (...)

TINA-TI — 基于 SPICE 的模拟仿真程序

TINA-TI 提供了 SPICE 所有的传统直流、瞬态和频域分析以及更多。TINA 具有广泛的后处理功能,允许您按照希望的方式设置结果的格式。虚拟仪器允许您选择输入波形、探针电路节点电压和波形。TINA 的原理图捕获非常直观 - 真正的“快速入门”。TINA-TI 安装需要大约 500MB。直接安装,如果想卸载也很容易。我们相信您肯定会爱不释手。

TINA 是德州仪器 (TI) 专有的 DesignSoft 产品。该免费版本具有完整的功能,但不支持完整版 TINA 所提供的某些其他功能。

如需获取可用 TINA-TI 模型的完整列表,请参阅:SpiceRack - 完整列表

需要 HSpice (...)