- ÷Τ‘λ≥ß…ΧΘΚTI

- ≤ζΤΖάύ±πΘΚΒγ‘¥Ιήάμ

- ΦΦ θάύΡΩΘΚ÷±Νς/÷±ΝςΩΣΙΊΈ»―ΙΤς - ΫΒ―ΙΈ»―ΙΤς

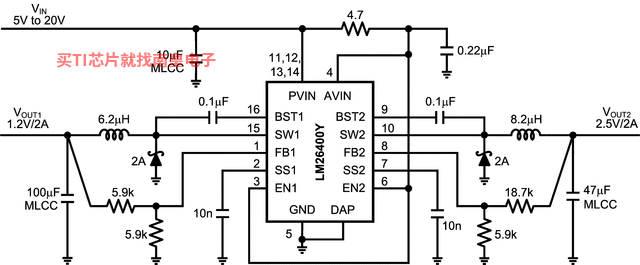

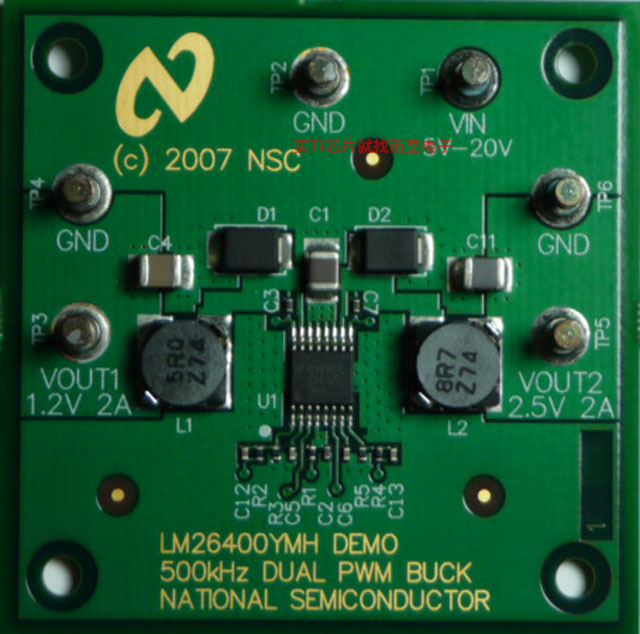

- ΙΠΡήΟη ωΘΚΥΪ¬Ζ 2AΓΔ500kHz Ωμ δ»κΖΕΈßΫΒ―ΙΈ»―ΙΤς

- ΒψΜς’βάο¥ρΩΣΦΑœ¬‘ΊLM26400YΒΡΦΦ θΈΡΒΒΉ Νœ

- TI¥ζάμ«ΰΒάΘ§ΧαΙ©Β±»’ΖΔΜθΓΔ―œΗώΒΡ÷ ΝΩ±ξΉΦΘ§¬ζΉψΡζΒΡΡΩ±ξΦέΗώ

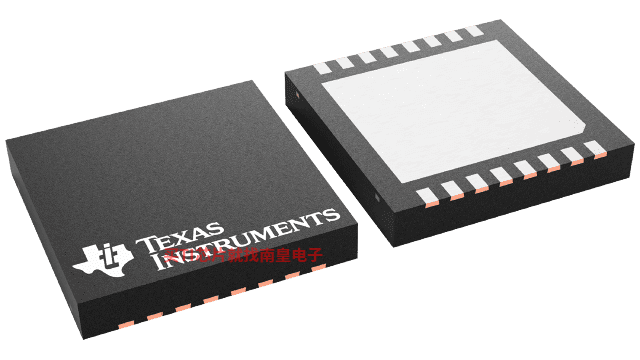

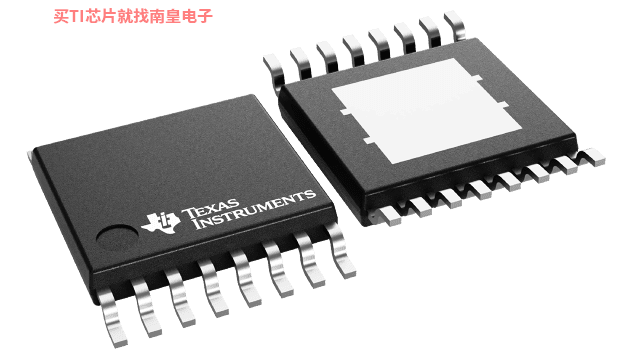

The LM26400Y device is a monolithic, two-output fixed-frequency PWM step-down DC-DC regulator, in a 16-pin WSON or thermally-enhanced HTSSOP package. With a minimum number of external components and internal loop compensation, the LM26400Y is easy to use.

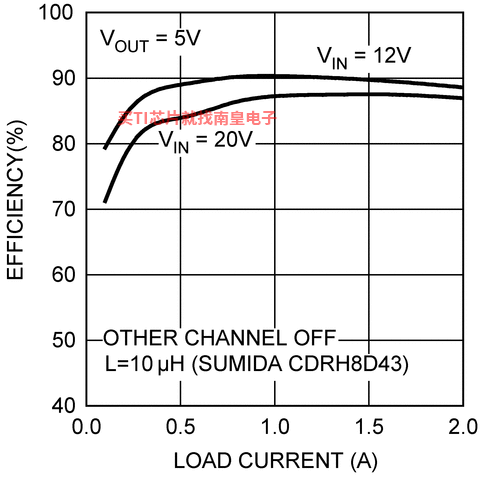

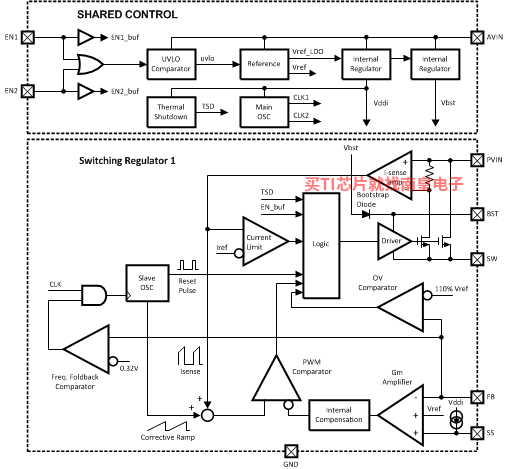

The ability to drive 2-A loads with an internal 175-mΩ NMOS switch using state-of-the-art 0.5-µm BiCMOS technology results in a high-power density design. The world class control circuitry allows for an ON-time as low as 40 ns, thus supporting high-frequency conversion over the entire input range of 3 V to 20 V and down to an output voltage of only 0.6 V. The LM26400Y utilizes peak current-mode control and internal compensation to provide high-performance regulation over a wide range of line and load conditions. Switching frequency is internally set to 500 kHz, optimal for a broad range of applications in terms of size versus thermal tradeoffs.

Given a nonsynchronous architecture, efficiencies above 90% are easy to achieve. External shutdown is included, enabling separate turnon and turnoff of the two channels. Additional features include programmable soft-start circuitry to reduce inrush current, pulse-by-pulse current limit and frequency foldback, integrated bootstrap structure, and thermal shutdown.

- Input Voltage Range of 3 V to 20 V

- Dual 2-A Output

- Output Voltage Down to 0.6 V

- Internal Compensation

- 500-kHz PWM Frequency

- Separate Enable Pins

- Separate Soft-Start Pins

- Frequency Foldback Protection

- 175-mΠΗ NMOS Switch

- Integrated Bootstrap Diodes

- Overcurrent Protection

- HTSSOP and WSON Packages

- Thermal Shutdown

- Vin (Min) (V)

- 3

- Vin (Max) (V)

- 20

- Vout (Min) (V)

- 0.6

- Vout (Max) (V)

- 16

- Iout (Max) (A)

- 2

- Iq (Typ) (uA)

- 4000

- Switching frequency (Min) (kHz)

- 500

- Switching frequency (Max) (kHz)

- 500

- Features

- Enable, Light Load Efficiency, Power Good, Pre-Bias Start-Up

- Rating

- Catalog

- Regulated outputs (#)

- 2

- Control mode

- Current Mode

- Duty cycle (Max) (%)

- 96

LM26400YΒΡΆξ’ϊ–ΆΚ≈”–ΘΚLM26400YMH/NOPBΓΔLM26400YMHX/NOPBΓΔLM26400YSD/NOPBΓΔLM26400YSDE/NOPBΘ§“‘œ¬ «’β–©≤ζΤΖΒΡΙΊΦϋ≤Έ ΐΦΑΙΌΆχ≤…ΙΚ±®ΦέΘΚ

LM26400YMH/NOPBΘ§ΙΛΉςΈ¬Ε»ΘΚ-40 to 125Θ§ΖβΉΑΘΚHTSSOP (PWP)-16Θ§ΑϋΉΑ ΐΝΩMPQΘΚ92ΗωΘ§MSL Β»ΦΕ/ΜΊΝςΚΗΖε÷ΒΈ¬Ε»ΘΚLevel-1-260C-UNLIMΘ§“ΐΫ≈ΕΤ≤ψ/ΚΗ«ρ≤ΡΝœΘΚSNΘ§TIΙΌΆχLM26400YMH/NOPBΒΡ≈ζΝΩUSDΦέΗώΘΚ2.44Θ®1000+Θ©

LM26400YMHX/NOPBΘ§ΙΛΉςΈ¬Ε»ΘΚ-40 to 125Θ§ΖβΉΑΘΚHTSSOP (PWP)-16Θ§ΑϋΉΑ ΐΝΩMPQΘΚ2500ΗωΘ§MSL Β»ΦΕ/ΜΊΝςΚΗΖε÷ΒΈ¬Ε»ΘΚLevel-1-260C-UNLIMΘ§“ΐΫ≈ΕΤ≤ψ/ΚΗ«ρ≤ΡΝœΘΚSNΘ§TIΙΌΆχLM26400YMHX/NOPBΒΡ≈ζΝΩUSDΦέΗώΘΚ2.033Θ®1000+Θ©

LM26400YSD/NOPBΘ§ΙΛΉςΈ¬Ε»ΘΚPropertyValueΘ§ΖβΉΑΘΚWSON (NHQ)-16Θ§ΑϋΉΑ ΐΝΩMPQΘΚ1000ΗωΘ§MSL Β»ΦΕ/ΜΊΝςΚΗΖε÷ΒΈ¬Ε»ΘΚLevel-1-260C-UNLIMΘ§“ΐΫ≈ΕΤ≤ψ/ΚΗ«ρ≤ΡΝœΘΚSNΘ§TIΙΌΆχLM26400YSD/NOPBΒΡ≈ζΝΩUSDΦέΗώΘΚ2.033Θ®1000+Θ©

LM26400YSDE/NOPBΘ§ΙΛΉςΈ¬Ε»ΘΚPropertyValueΘ§ΖβΉΑΘΚWSON (NHQ)-16Θ§ΑϋΉΑ ΐΝΩMPQΘΚ250ΗωΘ§MSL Β»ΦΕ/ΜΊΝςΚΗΖε÷ΒΈ¬Ε»ΘΚLevel-1-260C-UNLIMΘ§“ΐΫ≈ΕΤ≤ψ/ΚΗ«ρ≤ΡΝœΘΚSNΘ§TIΙΌΆχLM26400YSDE/NOPBΒΡ≈ζΝΩUSDΦέΗώΘΚ2.033Θ®1000+Θ©

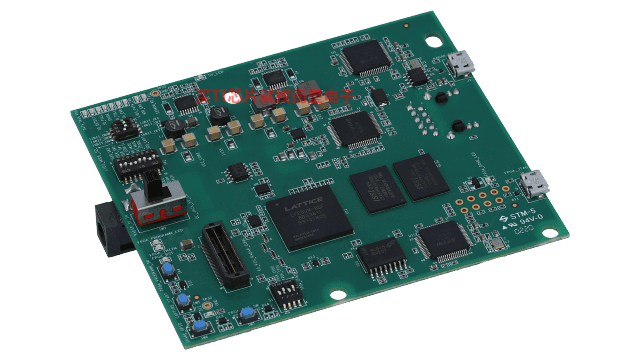

DCA1000EVM ΓΣ ”Ο”ΎάΉ¥οΗ–”Π”Π”ΟΒΡ Β ± ΐΨί≤ΕΉΫ ≈δΤςΤάΙάΡΘΩι

DCA1000 ΤάΙάΡΘΩι (EVM) ΈΣά¥Ή‘ TI AWR ΚΆ IWR άΉ¥ο¥ΪΗ–Τς EVM ΒΡΝΫΆ®ΒάΚΆΥΡΆ®ΒάΒΆ―Ι≤νΖ÷–≈Κ≈ (LVDS) ΝςΝΩΧαΙ© Β ± ΐΨί≤ΕΜώΚΆΝς Ϋ¥Ϊ δΓΘ ΐΨίΩ…“‘Ά®Ιΐ 1Gbps “‘ΧΪΆχ Β ±Νς Ϋ¥Ϊ δΒΫ‘Υ–– MMWAVE-STUDIO ΙΛΨΏΒΡ PC Μζ…œΘ§“‘Ϋχ––≤ΕΜώΓΔΩ… ”Μ·Θ§»ΜΚσΩ…“‘ΫΪΤδ¥ΪΒίΗχΥυ―ΓΒΡ”Π”ΟΫχ–– ΐΨί¥ΠάμΚΆΥψΖ®ΩΣΖΔΓΘ

LM26400YEVAL ΓΣ ΥΪ¬Ζ 2AΓΔ500kHz Ωμ δ»κΖΕΈßΫΒ―ΙΈ»―ΙΤς

The LM26400Y demonstration board was designed to provide two 2A outputs at 1.2V and 2.5V respectively. It uses the ETSSOP package option of the LM26400Y for easier probing. The design emphasizes on the compactness of the LM26400Y PCB layout and is thermally optimized. The total solution size is (...)

PSPICE-FOR-TI ΓΣ ”Ο”Ύ TI …ηΦΤΚΆΡΘΡβΙΛΨΏΒΡ PSpice

PSpice for TI Ω…ΧαΙ©Αο÷ζΤάΙάΡΘΡβΒγ¬ΖΙΠΡήΒΡ…ηΦΤΚΆΖ¬’φΜΖΨ≥ΓΘ¥ΥΙΠΡήΤκ»ΪΒΡ…ηΦΤΚΆΖ¬’φΧΉΦΰ Ι”Ο Cadence ΒΡΡΘΡβΖ÷Έω“ΐ«φΓΘPSpice for TI Ω…ΟβΖ― Ι”ΟΘ§Αϋά®“ΒΡΎ≥§¥σΒΡΡΘ–ΆΩβ÷°“ΜΘ§Κ≠Η«Έ“Ο«ΒΡΡΘΡβΚΆΒγ‘¥≤ζΤΖœΒΝ–“‘ΦΑΨΪ―ΓΒΡΡΘΡβ––ΈΣΡΘ–ΆΓΘΫη÷ζ?PSpice for TI ΒΡ…ηΦΤΚΆΖ¬’φΜΖΨ≥ΦΑΤδΡΎ÷ΟΒΡΡΘ–ΆΩβΘ§ΡζΩ…Ε‘Η¥‘”ΒΡΜλΚœ–≈Κ≈…ηΦΤΫχ––Ζ¬’φΓΘ¥¥Ϋ®Άξ’ϊΒΡ÷’ΕΥ…η±Η…ηΦΤΚΆ‘≠–ΆΫβΨωΖΫΑΗΘ§»ΜΚσ‘ΌΫχ––≤ΦΨ÷ΚΆ÷Τ‘λΘ§Ω…ΥθΕΧ≤ζΤΖ…œ – ±Φδ≤ΔΫΒΒΆΩΣΖΔ≥…±ΨΓΘ

‘Ύ?PSpice for TI …ηΦΤΚΆΖ¬’φΙΛΨΏ÷–Θ§ΡζΩ…“‘Υ―Υς TI (...)

TIDA-00431 ΓΣ ≤ΈΩΦ…ηΦΤ - ≤…”Ο 8GHz ÷±ΝςώνΚœ»Ϊ≤νΖ÷Ζ≈¥σΤςΒΡ RF ≤…―υ 4GSPS ADC

Ωμ¥χ…δΤΒ (RF) Ϋ” ’Τς”–÷ζ”ΎΦΪ¥σΧα…ΐΈόœΏΒγ…ηΦΤ÷–ΒΡΝιΜν–‘ΓΘΫœΩμΒΡΥ≤ ±¥χΩμ÷ß≥÷ΝιΜνΒςΫΎΕχΈό–ηΗΡΕ·”≤Φΰ«“ΡήΙΜ“‘ΦδΗτΫœ¥σΒΡΤΒ¬ ≤ΕΜώΕύΗωΆ®ΒάΓΘ¥Υ≤ΈΩΦ…ηΦΤΫι…ήΝΥ“ΜΗωΩμ¥χ…δΤΒΫ” ’ΤςΘ§ΗΟΫ” ’Τςάϊ”Ο 4 GSPS ΡΘ ΐΉΣΜΜΤς (ADC) ≤ΔΨΏ”–“ΜΗω 8GHz ÷±ΝςώνΚœ»Ϊ≤νΕ·Ζ≈¥σΤς«ΑΕΥΓΘΖ≈¥σΤς«ΑΕΥΧαΙ©–≈Κ≈‘ω“φ≤Δ‘ –μ≤…Φ·œ¬––ΒΫ÷±ΝςΒΡ–≈Κ≈Θ§ΕχΤΫΚβ-Ζ«ΤΫΚβ±δ―ΙΤςώνΚœ δ»κ‘ρΉω≤ΜΒΫ’β“ΜΒψΓΘ

TIDA-00826 ΓΣ 50ΠΗ 2GHz Ψ≤®Τς«ΑΕΥ≤ΈΩΦ…ηΦΤ

¥Υ≤ΈΩΦ…ηΦΤ « 50ΠΗ δ»κ Ψ≤®Τς”Π”ΟΒΡΡΘΡβ«ΑΕΥΒΡ“Μ≤ΩΖ÷ΓΘœΒΆ≥…ηΦΤ»Υ‘±Ω…«αΥ… Ι”Ο¥ΥΤάΙάΤΫΧ®ά¥¥ΠάμΤΒ”ρΚΆ ±”ρ”Π”Ο÷–ΒΡ÷±ΝςΒΫ 2GHz ΒΡ δ»κ–≈Κ≈ΓΘTIDA-00432 ΓΣ ΫΪ Xilinx ΤΫΧ®”Π”Ο”ΎœύΈΜ’σΝ–άΉ¥οœΒΆ≥“‘ Βœ÷ JESD204B «ß’Ή¥Έ≤…―υ ADC ΒΡΆ§≤Ϋ

¥ΥœΒΆ≥ΦΕ…ηΦΤ’Ι ΨΝΥ»γΚΈ Ι”Ο Xilinx VC707 ΤΫΧ®“ΜΤπΆ§≤ΫΝΫΗω ADC12J4000 ΤάΙάΡΘΩι (EVM)ΓΘ¥Υ…ηΦΤΈΡΒΒΫι…ήΝΥ±Ί“ΣΒΡ”≤Φΰ–όΗΡΚΆΤςΦΰ≈δ÷ΟΘ§Αϋά® ±÷”ΖΫΑΗΓΘ¥Υ…ηΦΤœ‘ ΨΝΥΟΩΗω EVM ΒΡ Ψάΐ≈δ÷ΟΈΡΦΰΓΘ¥Υ…ηΦΤΫι…ήΝΥ FPGA ΙΧΦΰΘ§≤Δœ‘ ΨœύΙΊΒΡ Xilinx IP Ωι≈δ÷Ο≤Έ ΐΓΘ¥ΥΆβΜΙœ‘ Ψ≤ΔΖ÷ΈωΝΥ‘Ύ ΒΦ ”≤Φΰ…œ≤…Φ·ΒΡ ΐΨίΘ§≤β ‘ΫαΙϊœ‘ Ψ≥ω 50ps ΡΎΒΡΆ§≤ΫΘ§Έ¥ Ι”ΟΧΊ–‘Μ·Βγά¬Θ§“≤Έ¥–ΘΉΦ¥Ϊ≤Ξ―”≥ΌΓΘ