- 制造厂商:TI

- 产品类别:时钟和计时

- 技术类目:时钟缓冲器

- 功能描述:低偏移、1 至 5、差动至 3.3V LVPECL 扇出缓冲器

- 点击这里打开及下载LMK00725的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

LMK00725 是一款低偏移、高性能时钟扇出缓冲器,此缓冲器能够从可接受差分或单端输入的两个输入中的一个分发多达 5 个 3.3V LVPECL 输出。 时钟使能输入在内部同步,以便在时钟使能引脚被置为有效或置为无效时消除输出上的欠幅脉冲或毛刺脉冲。 低附加抖动和相位噪底,以及可靠输出和部件间偏移特性使得 LMK00725 成为对高性能和可重复性有严格要求的应用的理想选择。

- 5 个 3.3V 差分 LVPECL 输出

- 附加抖动:312.5MHz 时为 43fs RMS(典型值)

- 噪声基底(≥ 1MHz 偏移):312.5MHz 时为 -158dBc/Hz(典型值)

- 输出频率:650MHz(最大值)

- 输出偏移:35ps(最大值)

- 部件间偏移:100ps(最大值)

- 传播延迟:0.37ns(最大值)

- 两个差分输入对(可由引脚选择)

- CLKx,nCLK 输入对接受 LVPECL,低压差分信号 (LVDS),主机时钟信号电平 (HCSL),短截线串联端接逻辑 (SSTL),低压高速收发器逻辑 (LVHSTL) 或单端信号

- 同步时钟启用

- 电源:3.3V ± 5%

- 封装:20 引线薄型小尺寸封装 (TSSOP)

- 工业温度范围:-40oC 至 85oC

- 与 ICS85304-01 引脚兼容,具有更低附加抖动和更宽温度范围

- 无线和有线基础设施

- 网络和数据通信

- 服务器和计算

- 医疗成像

- 便携式测试和测量

- 高端 A/V

- Function

- Differential, Fanout

- Additive RMS jitter (Typ) (fs)

- 43

- Output frequency (Max) (MHz)

- 650

- Number of outputs

- 5

- Output supply voltage (V)

- 3.3

- Core supply voltage (V)

- 3.3

- Output skew (ps)

- 35

- Features

- Pin control

- Operating temperature range (C)

- -40 to 85

- Rating

- Catalog

- Output type

- LVPECL

- Input type

- HCSL, LVCMOS, LVDS, LVPECL, LVTTL, SSTL

LMK00725的完整型号有:LMK00725PW、LMK00725PWR,以下是这些产品的关键参数及官网采购报价:

LMK00725PW,工作温度:-40 to 85,封装:TSSOP (PW)-20,包装数量MPQ:73个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:SN,TI官网LMK00725PW的批量USD价格:3.881(1000+)

LMK00725PWR,工作温度:-40 to 85,封装:TSSOP (PW)-20,包装数量MPQ:2500个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:SN,TI官网LMK00725PWR的批量USD价格:3.234(1000+)

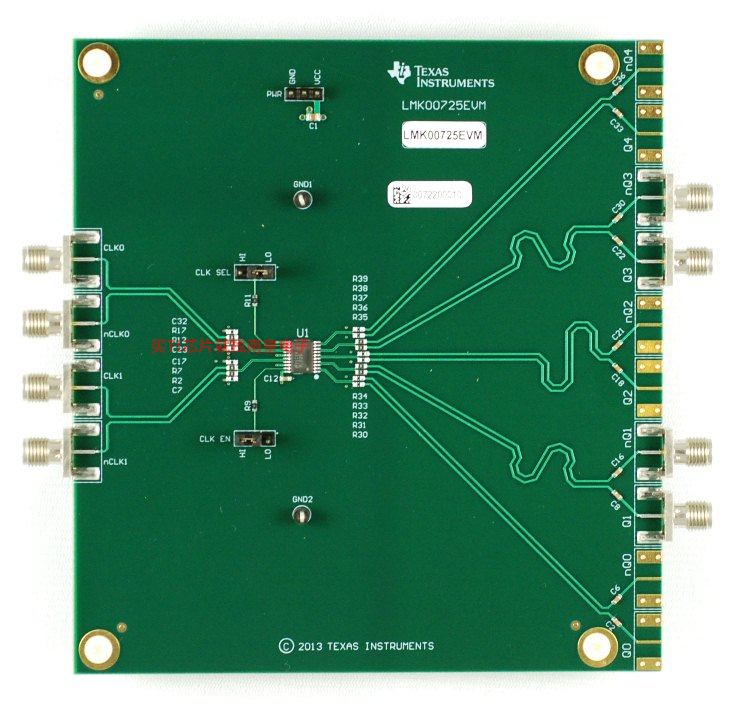

LMK00725EVM ― LMK00725 评估模块

LMK00725 是一款低偏差、高性能时钟扇出缓冲器,可提供最多五个 3.3V LVPECL 输出。时钟来自可接受差动或单端输入信号的两个可选输入之中的一个。

此评估模块 (EVM) 旨在演示 LMK00725 器件的功能和电气性能。为获得出色性能,此评估板配备了 50 欧姆的 SMA 连接器和 50 欧姆的布线阻抗。

LMK00725 IBIS Model

PSpice for TI 可提供帮助评估模拟电路功能的设计和仿真环境。此功能齐全的设计和仿真套件使用 Cadence 的模拟分析引擎。PSpice for TI 可免费使用,包括业内超大的模型库之一,涵盖我们的模拟和电源产品系列以及精选的模拟行为模型。借助?PSpice for TI 的设计和仿真环境及其内置的模型库,您可对复杂的混合信号设计进行仿真。创建完整的终端设备设计和原型解决方案,然后再进行布局和制造,可缩短产品上市时间并降低开发成本。

在?PSpice for TI 设计和仿真工具中,您可以搜索 TI (...)

CLOCK-TREE-ARCHITECT ― 时钟树架构编程软件

时钟树架构是一款时钟树综合工具,可根据您的系统要求生成时钟树解决方案,从而帮助您简化设计流程。该工具从庞大的时钟产品数据库中提取数据,然后生成系统级多芯片时钟解决方案。