- 制造厂商:TI

- 产品类别:时钟和计时

- 技术类目:时钟抖动清除器和同步器

- 功能描述:具有集成式 1840 至 1970MHz VCO0 且符合 JESD204B 标准的超低噪声时钟抖动消除器

- 点击这里打开及下载LMK04826的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

The LMK0482x family is the industry’s highest performance clock conditioner with JEDEC JESD204B support.

The 14 clock outputs from PLL2 can be configured to drive seven JESD204B converters or other logic devices, using device and SYSREF clocks. SYSREF can be provided using both DC and AC coupling. Not limited to JESD204B applications, each of the 14 outputs can be individually configured as high-performance outputs for traditional clocking systems.

The high performance, combined with features such as the ability to trade off between power or performance, dual VCOs, dynamic digital delay, holdover, and glitchless analog delay, make the LMK0482x family ideal for providing flexible high-performance clocking trees.

- JEDEC JESD204B Support

- Ultra-Low RMS Jitter

- 88 fs RMS Jitter (12 kHz to 20 MHz)

- 91 fs RMS Jitter (100 Hz to 20 MHz)

- –162.5 dBc/Hz Noise Floor at 245.76 MHz

- Up to 14 Differential Device Clocks from PLL2

- Up to 7 SYSREF Clocks

- Maximum Clock Output Frequency 3.1 GHz

- LVPECL, LVDS, HSDS, LCPECL Programmable Outputs from PLL2

- Up to 1 Buffered VCXO/Crystal Output from PLL1

- LVPECL, LVDS, 2xLVCMOS Programmable

- Dual Loop PLLatinum? PLL Architecture

- PLL1

- Up to 3 Redundant Input Clocks

- Automatic and Manual Switch-Over Modes

- Hitless Switching and LOS

- Integrated Low-Noise Crystal Oscillator Circuit

- Holdover Mode When Input Clocks are Lost

- Up to 3 Redundant Input Clocks

- PLL2

- Normalized [1 Hz] PLL Noise Floor of –227 dBc/Hz

- Phase Detector Rate up to 155 MHz

- OSCin Frequency-Doubler

- Two Integrated Low-Noise VCOs

- 50% Duty Cycle Output Divides, 1 to 32 (even and odd)

- Precision Digital Delay, Dynamically Adjustable

- 25-ps Step Analog Delay

- Multi-Mode: Dual PLL, Single PLL, and Clock Distribution

- Industrial Temperature Range: –40 to 85°C

- Supports 105°C PCB Temperature (Measured at Thermal Pad)

- 3.15-V to 3.45-V Operation

- Package: 64-Pin QFN (9.0 mm × 9.0 mm × 0.8 mm)

- Function

- Dual-loop PLL

- Number of outputs

- 15

- RMS jitter (fs)

- 88

- Output frequency (Min) (MHz)

- 0.225

- Output frequency (Max) (MHz)

- 2505

- Input type

- LVCMOS, LVDS, LVPECL

- Output type

- LVCMOS, LVDS, LVPECL

- Supply voltage (Min) (V)

- 3.15

- Supply voltage (Max) (V)

- 3.45

- Features

- JESD204B

- Operating temperature range (C)

- -40 to 85

LMK04826的完整型号有:LMK04826BISQ/NOPB、LMK04826BISQE/NOPB、LMK04826BISQX/NOPB,以下是这些产品的关键参数及官网采购报价:

LMK04826BISQ/NOPB,工作温度:-40 to 85,封装:WQFN (NKD)-64,包装数量MPQ:1000个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:SN,TI官网LMK04826BISQ/NOPB的批量USD价格:11.827(1000+)

LMK04826BISQE/NOPB,工作温度:-40 to 85,封装:WQFN (NKD)-64,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:SN,TI官网LMK04826BISQE/NOPB的批量USD价格:11.827(1000+)

LMK04826BISQX/NOPB,工作温度:-40 to 85,封装:WQFN (NKD)-64,包装数量MPQ:2000个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:SN,TI官网LMK04826BISQX/NOPB的批量USD价格:9.856(1000+)

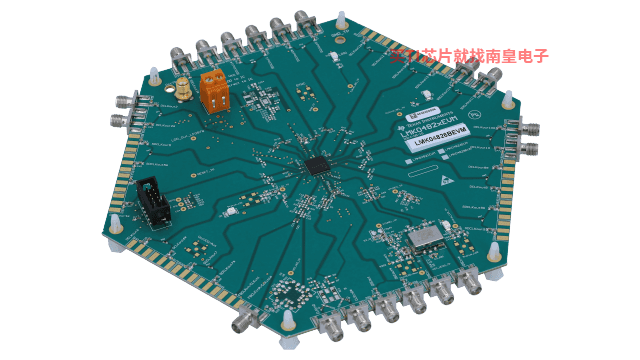

LMK04826BEVM — LMK04826BEVM 评估模块

LMK04826BEVM 和 LMK04828BEVM 支持 LMK04820 系列产品,该系列产品是支持 JEDEC JESD204B 且在业内具备超高性能的时钟调节器。双环路 PLLatinum™ 架构使用低噪声 VCXO 模块实现低于 100fs 的抖动(12kHz 至 20MHz)。双环架构由两个高性能锁相环 (PLL)、一个低噪声晶体振荡器电路以及一个高性能压控振荡器 (VCO) 构成。

第一个 PLL (PLL1) 具有低噪声抖动消除器功能,第二个 PLL (PLL2) 则执行时钟和 SYSREF 生成。PLL1 可配置为与外部 VCXO (...)

CLOCKDESIGNTOOL — 时钟设计工具 - 环路滤波器和器件配置 + 仿真

The Clock Design Tool software helps with part selection, loop filter design and simulation of timing device solutions. When you enter desired output frequencies and a reference frequency (optional), the tool provides TI devices to meet the specified requirements, divider values and a recommended (...)TICSPRO-SW — 德州仪器 (TI) 时钟和合成器 (TICS) 专业软件

德州仪器 (TI) 时钟和合成器 (TICS) 专业软件用于对具有以下前缀的产品编号的评估模块 (EVM) 进行编程:CDC、LMK 和 LMX。这些产品包括锁相环和电压控制振荡器 (PLL+VCO)、合成器和时钟器件。CODELOADER — CodeLoader 器件寄存器编程

The CodeLoader 4 software is used to program the LMX PLLs and LMK timing devices through either the USB or line print terminal (LPT) port of a computer. This software also provides information on how to program the device by showing the bits that are actually sent.Which software do I use?

Product

(...)

LMK04826 IBIS Model (Rev. C)

PSpice for TI 可提供帮助评估模拟电路功能的设计和仿真环境。此功能齐全的设计和仿真套件使用 Cadence 的模拟分析引擎。PSpice for TI 可免费使用,包括业内超大的模型库之一,涵盖我们的模拟和电源产品系列以及精选的模拟行为模型。借助?PSpice for TI 的设计和仿真环境及其内置的模型库,您可对复杂的混合信号设计进行仿真。创建完整的终端设备设计和原型解决方案,然后再进行布局和制造,可缩短产品上市时间并降低开发成本。

在?PSpice for TI 设计和仿真工具中,您可以搜索 TI (...)

CLOCK-TREE-ARCHITECT — 时钟树架构编程软件

时钟树架构是一款时钟树综合工具,可根据您的系统要求生成时钟树解决方案,从而帮助您简化设计流程。该工具从庞大的时钟产品数据库中提取数据,然后生成系统级多芯片时钟解决方案。