- 制造厂商:TI

- 产品类别:时钟和计时

- 技术类目:时钟缓冲器

- 功能描述:双组 8 通道输出 1.8V、2.5V 和 3.3V LVDS 缓冲器

- 点击这里打开及下载LMK1D2108的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

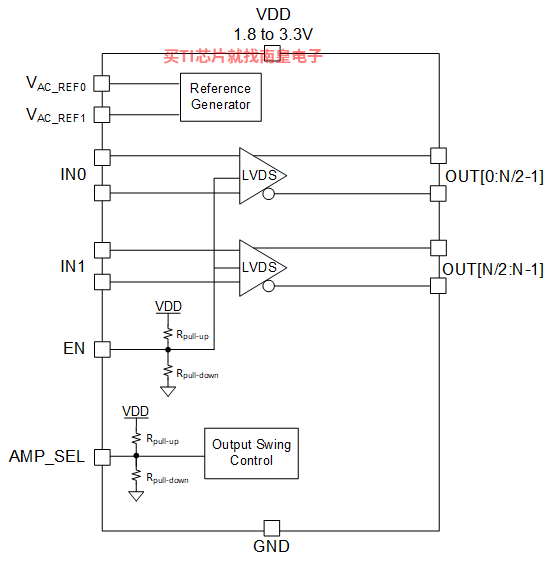

LMK1D210x 时钟缓冲器将两个时钟输入(IN0 和 IN1)分配给 LMK1D2108 中的共 16 对差分 LVDS 时钟输出(OUT0 至 OUT15),以及 LMK1D2106 中的共 12 对时钟输出(OUT0 至 OUT11),通过超小延迟实现时钟分配。每个缓冲器块由一个输入和最多 6 个 (LMK1D2106) 或 8 个 (LMK1D2108) LVDS 输出组成。输入可以为 LVDS、LVPECL、HCSL、CML 或 LVCMOS。

LMK1D210x 专为驱动 50Ω 传输线路而设计。在单端模式下驱动输入时,对未使用的负输入引脚施加适当的偏置电压(请参阅Figure 8-6)。

使用控制引脚 (EN) 可以启用或禁用输出组。如果该引脚保持开路,将启用两个组输出。如果控制引脚切换至逻辑“0”,则两个组输出均被禁用(静态逻辑“0”)。如果控制引脚切换至逻辑“1”,则一个组的输出被禁用,而另一个组的输出被启用。该器件还支持失效防护功能。该器件还整合了输入迟滞,可防止在没有输入信号的情况下输出随机振荡。

该器件可在 1.8V、2.5V 或 3.3V 电源环境下工作,额定温度范围是 –40°C 至 105°C(环境温度)。

- 高性能 LVDS 时钟缓冲器系列:高达 2GHz

- 双路 1:6 差分缓冲器

- 双路 1:8 差分缓冲器

- 电源电压:1.71V 至 3.465V

- 低附加抖动:156.25MHz 下小于 12kHz 至 20MHz 范围内的 60fs RMS 最大值

- 超低相位本底噪声:-164dBc/Hz(典型值)

- 超低传播延迟:< 575ps(最大值)

- 输出延迟:20ps(最大值)

- 高摆幅 LVDS(升压模式):500mV VOD(典型值,AMP_SEL 设置为 1 时)

- 使用 EN 引脚启用/禁用组

- 失效防护输入操作

- 通用输入接受 LVDS、LVPECL、LVCMOS、HCSL 和 CML 信号电平

- LVDS 基准电压 (VAC_REF) 适用于容性耦合输入

- 工业温度范围:–40°C 至 105°C

- 采用封装

-

LMK1D2106:6mm × 6mm 40 引脚 VQFN (RHA)

-

LMK1D2108:7mm × 7mm 48 引脚 VQFN (RGZ)

-

- Function

- Clock buffer, Differential

- Additive RMS jitter (Typ) (fs)

- 45

- Output frequency (Max) (MHz)

- 2000

- Number of outputs

- 16

- Output supply voltage (V)

- 1.8, 2.5, 3.3

- Core supply voltage (V)

- 1.8, 2.5, 3.3

- Output skew (ps)

- 20

- Features

- Dual 1:8 fanout, Universal inputs, Output enable control

- Operating temperature range (C)

- -40 to 105

- Rating

- Catalog

- Output type

- LVDS

- Input type

- HCSL, LP-HCSL, LVCMOS, LVDS, LVPECL

LMK1D2108的完整型号有:LMK1D2108RGZR、LMK1D2108RGZT,以下是这些产品的关键参数及官网采购报价:

LMK1D2108RGZR,工作温度:-40 to 105,封装:VQFN (RGZ)-48,包装数量MPQ:2500个,MSL 等级/回流焊峰值温度:Level-2-260C-1 YEAR,引脚镀层/焊球材料:NIPDAU,TI官网LMK1D2108RGZR的批量USD价格:7.384(1000+)

LMK1D2108RGZT,工作温度:-40 to 105,封装:VQFN (RGZ)-48,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-2-260C-1 YEAR,引脚镀层/焊球材料:NIPDAU,TI官网LMK1D2108RGZT的批量USD价格:8.861(1000+)

LMK1D1216EVM — LMK1D1216 low jitter 2:16 LVDS fan-out buffer evaluation module

LMK1D1216 is a high-performance, low additive jitter LVDS clock buffer with two differential inputs and 16 LVDS outputs. This evaluation module (EVM) is designed to demonstrate the electrical performance of the LMK1D1216. However, this EVM can also be used to evaluate other 48 pin devices in the (...)LMK1DX IBIS Model (Rev. A)

PSpice for TI 可提供帮助评估模拟电路功能的设计和仿真环境。此功能齐全的设计和仿真套件使用 Cadence 的模拟分析引擎。PSpice for TI 可免费使用,包括业内超大的模型库之一,涵盖我们的模拟和电源产品系列以及精选的模拟行为模型。借助?PSpice for TI 的设计和仿真环境及其内置的模型库,您可对复杂的混合信号设计进行仿真。创建完整的终端设备设计和原型解决方案,然后再进行布局和制造,可缩短产品上市时间并降低开发成本。

在?PSpice for TI 设计和仿真工具中,您可以搜索 TI (...)