- 制造厂商:TI

- 产品类别:接口

- 技术类目:LVDS、M-LVDS 和 PECL IC

- 功能描述:2Gbps LVDS、LVPECL 和 CML 转 LVPECL 中继器/转换器

- 点击这里打开及下载SN65LVDS101的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

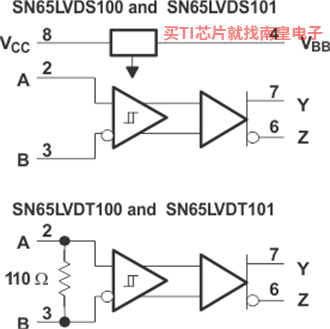

The SN65LVDS100, SN65LVDT100, SN65LVDS101, and SN65LVDT101 are high-speed differential receivers and drivers connected as repeaters. The receiver accepts low-voltage differential signaling (LVDS), positive-emitter-coupled logic (PECL), or current-mode logic (CML) input signals at rates up to 2 Gbps and repeats it as either an LVDS or PECL output signal. The signal path through the device is differential for low radiated emissions and minimal added jitter.

The outputs of the SN65LVDS100 and SN65LVDT100 are LVDS levels as defined by TIA/EIA-644-A. The outputs of the SN65LVDS101 and SN65LVDT101 are compatible with 3.3-V PECL levels. Both drive differential transmission lines with nominally 100-Ω characteristic impedance.

The SN65LVDT100 and SN65LVDT101 include a 110-Ω differential line termination resistor for less board space, fewer components, and the shortest stub length possible. They do not include the VBB voltage reference found in the SN65LVDS100 and SN65LVDS101. VBB provides a voltage reference of typically 1.35 V below VCC for use in receiving single-ended input signals and is particularly useful with single-ended 3.3-V PECL inputs. When VBB is not used, it should be unconnected or open.

All devices are characterized for operation from –40°C to 85°C.

- Designed for Signaling Rates ≥ 2 Gbps

- Total Jitter < 65 ps

- Low-Power Alternative for the MC100EP16

- Low 100-ps (Maximum) Part-to-Part Skew

- 25 mV of Receiver Input Threshold Hysteresis Over 0-V to 4-V Input Voltage Range

- Inputs Electrically Compatible With LVPECL, CML, and LVDS Signal Levels

- 3.3-V Supply Operation

- LVDT Integrates 110-Ω Terminating Resistor

- Offered in SOIC and MSOP

- Function

- Repeater, Translator

- Protocols

- LVDS, LVPECL, CML

- Number of transmitters

- 1

- Number of receivers

- 1

- Supply voltage (V)

- 3.3

- Signaling rate (Mbps)

- 2000

- Input signal

- CML, LVDS, LVPECL

- Output signal

- LVPECL

- Rating

- Catalog

- Operating temperature range (C)

- -40 to 85

SN65LVDS101的完整型号有:SN65LVDS101D、SN65LVDS101DGK、SN65LVDS101DGKR、SN65LVDS101DR,以下是这些产品的关键参数及官网采购报价:

SN65LVDS101D,工作温度:-40 to 85,封装:SOIC (D)-8,包装数量MPQ:75个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN65LVDS101D的批量USD价格:2.341(1000+)

SN65LVDS101DGK,工作温度:-40 to 85,封装:VSSOP (DGK)-8,包装数量MPQ:80个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN65LVDS101DGK的批量USD价格:2.341(1000+)

SN65LVDS101DGKR,工作温度:-40 to 85,封装:VSSOP (DGK)-8,包装数量MPQ:2500个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN65LVDS101DGKR的批量USD价格:2.006(1000+)

SN65LVDS101DR,工作温度:-40 to 85,封装:SOIC (D)-8,包装数量MPQ:2500个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN65LVDS101DR的批量USD价格:2.006(1000+)

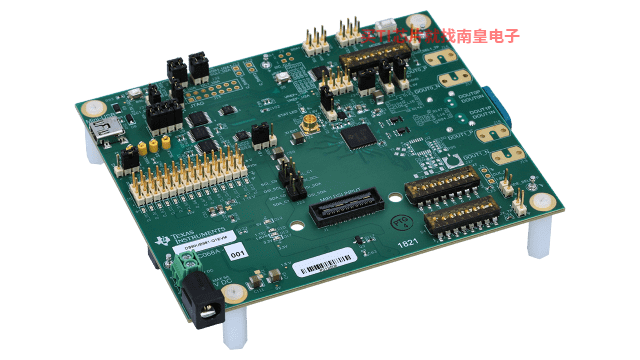

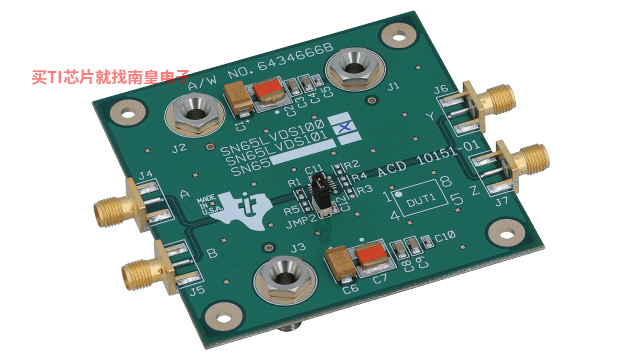

SN65CML100EVM SN65CML100 评估模块]]

The EVM allows evaluation of operation of theSN65LVDS100/101 or SN65CML100 high-speed differential translators/repeaters. Differential input signals (LVDS, LVPECL, CML, etc.) can be applied and the device output can beobserved across on board terminations, or via direct connection to 50-ohm (...)

SN65LVDS101EVM SN65LVDS101 评估模块

The EVM allows evaluation of operation of the SN65LVDS100/101 or SN65CML100 high-speed differential translators/repeaters. Differential input signals (LVDS, LVPECL, CML, etc.) can be applied and the device output can be observed across on board terminations, or via direct connection to (...)

SN65LVDS101 IBIS Model (Rev. A)

PSpice for TI 可提供帮助评估模拟电路功能的设计和仿真环境。此功能齐全的设计和仿真套件使用 Cadence 的模拟分析引擎。PSpice for TI 可免费使用,包括业内超大的模型库之一,涵盖我们的模拟和电源产品系列以及精选的模拟行为模型。借助PSpice for TI 的设计和仿真环境及其内置的模型库,您可对复杂的混合信号设计进行仿真。创建完整的终端设备设计和原型解决方案,然后再进行布局和制造,可缩短产品上市时间并降低开发成本。

在PSpice for TI 设计和仿真工具中,您可以搜索 TI (...)

TINA-TI 基于 SPICE 的模拟仿真程序

TINA-TI 提供了 SPICE 所有的传统直流、瞬态和频域分析以及更多。TINA 具有广泛的后处理功能,允许您按照希望的方式设置结果的格式。虚拟仪器允许您选择输入波形、探针电路节点电压和波形。TINA 的原理图捕获非常直观 - 真正的“快速入门”。TINA-TI 安装需要大约 500MB。直接安装,如果想卸载也很容易。我们相信您肯定会爱不释手。

TINA 是德州仪器 (TI) 专有的 DesignSoft 产品。该免费版本具有完整的功能,但不支持完整版 TINA 所提供的某些其他功能。

如需获取可用 TINA-TI 模型的完整列表,请参阅:SpiceRack - 完整列表

需要 HSpice (...)

TIDA-01378 适用于上行 DOCSIS 3.1 应用的宽带接收器参考设计

此参考设计包括用于宽带接收器应用的模拟前端 (AFE) 信号链,其中使用 LMH2832 数字控制可变增益放大器 (DVGA) 和 ADS54J40 模数转换器 (ADC)。此设计主要针对适用于电缆调制解调器终端系统 (CMTS) 的上游 DOCSIS 3.1 接收器应用,并支持高达 196 MHz 的上游信号带宽。该电路满足了 DOCSIS 3.1 标准的滤波和模拟信号处理要求,使得系统设计人员更容易将设计立即整合在上游信号路径的 CMTS 侧。