- 制造厂商:TI

- 产品类别:逻辑和电压转换

- 技术类目:触发器、锁存器和寄存器 - D 型锁存器

- 功能描述:具有三态输出的八路 D 类透明读回锁存器

- 点击这里打开及下载SN74ALS667的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

These 8-bit D-type transparent latches are designed specifically for storing the contents of the input data bus, plus reading back the stored data onto the input data bus. In addition, they provide a 3-state buffer-type output and are easily utilized in bus-structured applications.

While the latch enable (LE) is high, the Q outputs of the SN74ALS666 follow the data (D) inputs. The Q\ outputs of the SN74ALS667 provide the inverse of the data applied to its D inputs. The Q or Q\ output of both devices is in the high-impedance state if either output-enable (OE1\ or OE2\) input is at a high logic level.

Read back is provided through the read-back control (OERB\) input. When OERB\ is taken low, the data present at the output of the data latches passes back onto the input data bus. When OERB\ is taken high, the output of the data latches is isolated from the D inputs. OERB\ does not affect the internal operation of the latches; however, caution should be exercised to avoid a bus conflict.

The SN74ALS666 and SN74ALS667 are characterized for operation from 0°C to 70°C.

- 3-State I/O-Type Read-Back Inputs

- Bus-Structured Pinout

- Choice of True or Inverting Logic

- SN74ALS666...True Outputs

- SN74ALS667...Inverted Outputs

- Preset and Clear Inputs

- Package Options Include Plastic Small-Outline (DW) Packages and Standard Plastic (NT) 300-mil DIPs

- Number of channels (#)

- 8

- Technology Family

- ALS

- Supply voltage (Min) (V)

- 4.5

- Supply voltage (Max) (V)

- 5.5

- Input type

- Bipolar

- Output type

- 3-State

- Clock Frequency (Max) (MHz)

- 75

- IOL (Max) (mA)

- 24

- IOH (Max) (mA)

- -2.6

- ICC (Max) (uA)

- 79000

- Features

- High speed (tpd 10-50ns), Inverting output, Flow-through pinout

SN74ALS667的完整型号有:SN74ALS667DW,以下是这些产品的关键参数及官网采购报价:

SN74ALS667DW,工作温度:0 to 70,封装:SOIC (DW)-24,包装数量MPQ:25个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN74ALS667DW的批量USD价格:15.708(1000+)

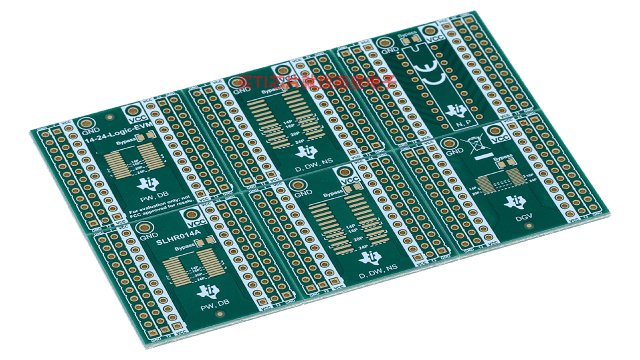

14-24-LOGIC-EVM ― 支持 14 到 24 引脚 PW、DB、D、DW、NS、DYY 和 DGV 封装的通用逻辑 EVM

该 EVM 设计用于支持采用 14 至 24 引脚 D、DW、DB、NS、PW、DYY 或 DGV 封装的任何逻辑器件。