- 制造厂商:TI

- 产品类别:逻辑和电压转换

- 技术类目:缓冲器、驱动器和收发器 - 同相缓冲器和驱动器

- 功能描述:具有施密特触发输入的 6 通道、0.8V 至 2.7V 高速缓冲器

- 点击这里打开及下载SN74AUC17的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

This hex Schmitt-trigger buffer is operational at 0.8-V to 2.7-V VCC, but is designed specifically for 1.65-V to 1.95-V VCC operation.

The SN74AUC17 contains six independent buffers and performs the Boolean function Y = A. The device functions as six independent buffers, but because of Schmitt action, it may have different input threshold levels for positive-going (VT+) and negative-going (VT-) signals.

This device is fully specified for partial-power-down applications using Ioff. The Ioff circuitry disables the outputs, preventing damaging current backflow through the device when it is powered down.

- Optimized for 1.8-V Operation and Is 3.6-V I/O Tolerant to Support Mixed-Mode Signal Operation

- Ioff Supports Partial-Power-Down Mode Operation

- Sub-1-V Operable

- Max tpd of 1.8 ns at 1.8 V

- Low Power Consumption, 10-μA Max ICC

- ±8-mA Output Drive at 1.8 V

- Latch-Up Performance Exceeds 100 mA Per JESD 78, Class II

- ESD Protection Exceeds JESD 22

- 2000-V Human-Body Model (A114-A)

- 200-V Machine Model (A115-A)

- 1000-V Charged-Device Model (C101)

- Technology Family

- AUC

- Supply voltage (Min) (V)

- 0.8

- Supply voltage (Max) (V)

- 2.7

- Number of channels (#)

- 6

- IOL (Max) (mA)

- 9

- ICC (Max) (uA)

- 10

- IOH (Max) (mA)

- -9

- Input type

- Schmitt-Trigger

- Output type

- Push-Pull

- Features

- Balanced outputs, Ultra high speed (tpd <5ns), Partial power down (Ioff), Over-voltage tolerant inputs

- Rating

- Catalog

SN74AUC17的完整型号有:SN74AUC17RGYR,以下是这些产品的关键参数及官网采购报价:

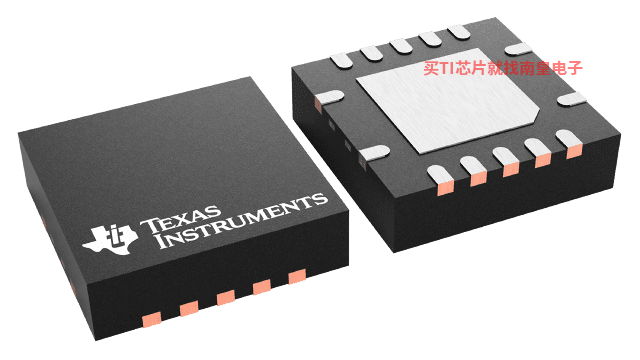

SN74AUC17RGYR,工作温度:-40 to 85,封装:VQFN (RGY)-14,包装数量MPQ:3000个,MSL 等级/回流焊峰值温度:Level-2-260C-1 YEAR,引脚镀层/焊球材料:NIPDAU,TI官网SN74AUC17RGYR的批量USD价格:.239(1000+)

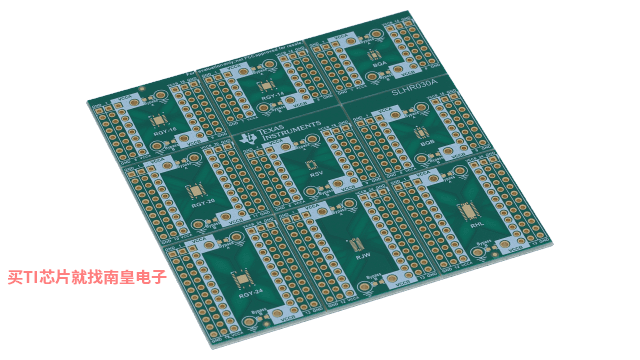

14-24-NL-LOGIC-EVM ― Generic 14 through 24 pin non-leaded package evaluation module

Flexible EVM designed to support any logic or translation device that has a BQA, BQB, RGY (14-24 pin), RSV, RJW, or RHL package.SN74AUC17 IBIS Model

该电路实现了用于处理输入信号(高达 ±12V)的高性能数据采集 (DAQ) 解决方案,该信号叠加在相对于系统主电源接地电位的较大共模偏移(经测试高达 155 Vp-p,从直流到约 15 kHz)上。通过生成隔离式电源来实现共模抑制,从而允许模拟信号链随着输入共模信号浮动。模拟信号链包含具有集成模拟前端 (AFE) 的高性能 16 位 1 MSPS SAR ADC,该 AFE 可提供高输入阻抗和 ±12V 宽输入电压范围。相关应用领域包括 :具有逐通道隔离的 PLC 模拟输入模块、汽车电池组监控、交流电机驱动器中的电源监控和热电偶测量。PMP10580 ― 针对 Terasic DE0-Nano (Cyclone IV) 的电源解决方案 - 参考设计

PMP10580 参考设计提供为 Altera 的 Cyclone IV FPGA 供电时所需的所有电源轨。DE0-Nano 由 Terasic 开发,该板可通过 Terasic 的网站购买。