- ���쳧�̣�TI

- ��Ʒ������͵�ѹת��

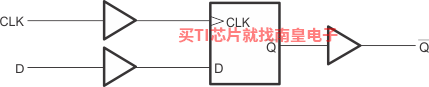

- ������Ŀ�����������������ͼĴ��� - D �ʹ�����

- �������������ĵ�·�����ش���ʽ D �ʹ�����

- ������������SN74AUP1G80�ļ����ĵ�����

- TI�����������ṩ���շ������ϸ������������������Ŀ��۸�

The AUP family is TI’s premier solution to the industry’s low-power needs in battery-powered portable applications. This family assures a low static- and dynamic-power consumption across the entire VCC range of 0.8 V to 3.6 V, resulting in increased battery life (see AUP – The Lowest-Power Family). This product also maintains excellent signal integrity (see Excellent Signal Integrity).

This is a single positive-edge-triggered D-type flip-flop. When data at the data (D) input meets the setup time requirement, the data is transferred to the Q output on the positive-going edge of the clock pulse. Clock triggering occurs at a voltage level and is not directly related to the rise time of the clock pulse. Following the hold-time interval, data at the D input can be changed without affecting the levels at the outputs.

NanoStar™ package technology is a major breakthrough in IC packaging concepts, using the die as the package.

This device is fully specified for partial-power-down applications using Ioff. The Ioff circuitry disables the outputs when the device is powered down. This inhibits current backflow into the device which prevents damage to the device.

- Latch-Up Performance Exceeds 100 mA Per JESD78, ClassII

- ESD Performance Tested Per JESD 22

- 2000-V Human-Body Model (A114-B, Class II)

- 1000-V Charged-Device Model (C101)

- Available in the Texas Instruments NanoStar? Package

- Low Static-Power Consumption (ICC = 0.9 ��A Maximum)

- Low Dynamic-Power Consumption (Cpd = 4.3 pF Typical at 3.3 V)

- Low Input Capacitance (Ci = 1.5 pF Typical)

- Low Noise �C Overshoot and Undershoot <10% of VCC

- Ioff Supports Partial-Power-Down Mode Operation

- Schmitt-Trigger Action Allows Slow Input Transition and Better Switching Noise Immunity at the Input (Vhys = 250 mV Typical at 3.3 V)

- Wide Operating VCC Range of 0.8 V to 3.6 V

- Optimized for 3.3-V Operation

- 3.6-V I/O Tolerant to Support Mixed-Mode Signal Operation

- tpd = 4.4 ns Maximum at 3.3 V

- Suitable for Point-to-Point Applications

- Number of channels (#)

- 1

- Technology Family

- AUP

- Supply voltage (Min) (V)

- 0.8

- Supply voltage (Max) (V)

- 3.6

- Input type

- Standard CMOS

- Output type

- Push-Pull

- Clock Frequency (Max) (MHz)

- 260

- IOL (Max) (mA)

- 4

- IOH (Max) (mA)

- -4

- ICC (Max) (uA)

- 0.9

- Features

- Balanced outputs, Very high speed (tpd 5-10ns), Over-voltage tolerant inputs, Partial power down (Ioff)

SN74AUP1G80�������ͺ��У�SN74AUP1G80DBVR��SN74AUP1G80DBVT��SN74AUP1G80DCKR��SN74AUP1G80DCKT��SN74AUP1G80DPWR��SN74AUP1G80DRYR��SN74AUP1G80DSFR��SN74AUP1G80YFPR��SN74AUP1G80YZPR����������Щ��Ʒ�Ĺؼ������������ɹ����ۣ�

SN74AUP1G80DBVR�������¶ȣ�-40 to 85����װ��SOT-23 (DBV)-5����װ����MPQ��3000����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�NIPDAU��TI����SN74AUP1G80DBVR������USD�۸�0.106��1000+��

SN74AUP1G80DBVT�������¶ȣ�-40 to 85����װ��SOT-23 (DBV)-5����װ����MPQ��250����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�NIPDAU��TI����SN74AUP1G80DBVT������USD�۸�0.306��1000+��

SN74AUP1G80DCKR�������¶ȣ�-40 to 85����װ��SC70 (DCK)-5����װ����MPQ��3000����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�NIPDAU��TI����SN74AUP1G80DCKR������USD�۸�0.066��1000+��

SN74AUP1G80DCKT�������¶ȣ�-40 to 85����װ��SC70 (DCK)-5����װ����MPQ��250����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�NIPDAU��TI����SN74AUP1G80DCKT������USD�۸�0.306��1000+��

SN74AUP1G80DPWR�������¶ȣ�-40 to 85����װ��X2SON (DPW)-5����װ����MPQ��3000����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�NIPDAU��TI����SN74AUP1G80DPWR������USD�۸�0.117��1000+��

SN74AUP1G80DRYR�������¶ȣ�-40 to 85����װ��SON (DRY)-6����װ����MPQ��5000����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�NIPDAUAG��TI����SN74AUP1G80DRYR������USD�۸�0.117��1000+��

SN74AUP1G80DSFR�������¶ȣ�-40 to 85����װ��SON (DSF)-6����װ����MPQ��5000����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�NIPDAU��TI����SN74AUP1G80DSFR������USD�۸�0.127��1000+��

SN74AUP1G80YFPR�������¶ȣ�PropertyValue����װ��DSBGA (YFP)-6����װ����MPQ��3000����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�SNAGCU��TI����SN74AUP1G80YFPR������USD�۸�0.166��1000+��

SN74AUP1G80YZPR�������¶ȣ�-40 to 85����װ��DSBGA (YZP)-5����װ����MPQ��3000����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�SNAGCU��TI����SN74AUP1G80YZPR������USD�۸�0.176��1000+��

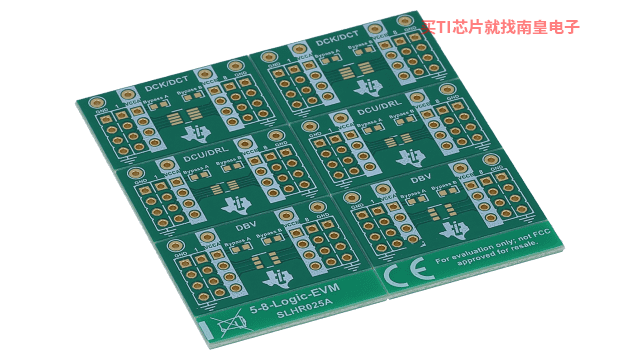

5-8-LOGIC-EVM �� ֧�� 5 �� 8 ���� DCK��DCT��DCU��DRL �� DBV ��װ��ͨ���� EVM

���� EVM �������֧�־��� 5 �� 8 �������Ҳ��� DCK��DCT��DCU��DRL �� DBV ��װ���κ�������SN74AUP1G80 IBIS Model (Rev. B)

TIDA-01054 �ο���Ʋ��� LM53635 ��ѹת�������ɰ������� EMI �Ը��� 16 λ�����ݲɼ� (DAQ) ϵͳ�����ܽ���Ӱ�졣�����ý�ѹת�����������Ա���Խ���Դ������������ڿ����ź�·����λ�ã��������������Ҫ�� EMI ����������ͬʱ���Խ�ʡ����ռ䡣�����ʹ�� 20 λ 1MSPS SAR ADC ֧�� 100.13dB ��ϵͳ SNR ���ܣ������ƥ��ʹ���ⲿ��Դʱ�� 100.14dB SNR ���ܡ�TIDA-01055 �� ���ڸ����� DAQ ϵͳ�� ADC ��ѹ���������Ż��ο����

�����ڸ����� DAQ ϵͳ�� TIDA-01055 �ο�����Ż��� ADC ��������������� SNR ���ܲ������ģ�ʹ�� TI OPA837 ��������Ŵ����������������ڸ��ϻ��������ã��봫ͳ����Ŵ�����ȣ������Ľ����� 22%�����м��ɻ������ĵ�ѹ��Դͨ��ȱ���ڸ�ͨ����ϵͳ��ʵ������������������ǿ�ȡ��òο�����ܹ�������� ADC ��ʵ�� 15.77 λ��ϵͳ ENOB��ʹ�� 18 λ 2MSPS SAR ADC����TIDA-01057 �� ������������ 20 λ ADC ���źŶ�̬��Χ��ʵ������ 10Vpp �������IJο����

This reference design is designed for high performance data acquisition(DAQ) systems to improve the dynamic range of 20 bit differential input ADCs. Many DAQ systems require the measurement capability at a wide FSR (Full Scale Range) in order to obtain sufficient signal dynamic range. Many earlier (...)TIDA-01056 �� ����������ȵؼ�С EMI ��ͬʱ�Ż�����Ч�ʵ� 20 λ 1MSPS DAQ �ο����

�������ڸ��������ݲɼ� (DAQ) ϵͳ�IJο�����Ż��˹��ʼ����Խ����IJ����̶ȵؼ�С������ѹ���� EMI Ӱ�죨ͨ��ʹ�� LMS3635-Q1 ��ѹת���������� LM53635 ��ѹת������ȣ��òο���ƿ������Ḻ�ص����½�Ч����� 7.2%���Ӷ�ʵ�� 125.25dB �� SFDR��99dB �� SNR �� 16.1 �� ENOB��TIDA-01051 �� �Ż� FPGA �����ʺ��Զ������豸�����������IJο����

TIDA-01051 �ο����������ʾ����ͨ�������ݲɼ� (DAQ) ϵͳ���������Զ������豸 (ATE) �е�ϵͳ�������Ż���ͨ���ܶȡ����ɡ����ġ�ʱ�ӷ�����ź������ܡ����ô��������� TI DS90C383B�������ͬ������ ADC ����뼸�� LVDS �߽�ϣ��������������� FPGA ���봦����������������ˣ����� FPGA �ɴ����� DAQ ͨ������������ӣ����ҵ�·�岼�ߵĸ�����Ҳ��͡�TIDA-01050 �� ������ 18 λ SAR ����ת������ģ��ǰ���Ż��� DAQ ϵͳ�ο����

TIDA-01050 �ο������Ϊ�˸���ͨ�����Զ������豸��صļ��ɡ����ġ����ܺ�ʱ�����⡣������������κ� ATE ϵͳ������������������Ҫ��������ͨ����ϵͳ��TIDA-01052 �� ʹ�ø���Դ����Ľ��������� THD �� ADC �������ο����

TIDA-01052 �ο����ּ��ͻ����ģ��ǰ���������Ŵ�����ʹ�ø���ѹ������ǽӵ����µ�ϵͳ�����������˸���������ģ��ǰ���йأ��������ר������Զ������豸��