- ���쳧�̣�TI

- ��Ʒ������͵�ѹת��

- ������Ŀ������ - ��������

- �������������Ŀ����ö����

- ������������SN74AUP1G97�ļ����ĵ�����

- TI�����������ṩ���շ������ϸ������������������Ŀ��۸�

The AUP family is TI’s premier solution to the industry’s low-power needs in battery-powered portable applications. This family ensures a very low static- and dynamic-power consumption across the entire VCC range of 0.8 V to 3.6 V, resulting in increased battery life (see Figure 1). This product also maintains excellent signal integrity (see the very low undershoot and overshoot characteristics shown in Figure 2).

The SN74AUP1G97 features configurable multiple functions. The output state is determined by eight patterns of 3-bit input. The user can choose the logic functions MUX, AND, OR, NAND, NOR, inverter, and noninverter. All inputs can be connected to VCC or GND.

The device functions as an independent gate with Schmitt-trigger inputs, which allows for slow input transition and better switching-noise immunity at the input.

NanoStar™ package technology is a major breakthrough in IC packaging concepts, using the die as the package.

This device is fully specified for partial-power-down applications using Ioff. The Ioff circuitry disables the outputs, preventing damaging current backflow through the device when it is powered down.

- Available in the Texas Instruments NanoStar? Package

- Low Static-Power Consumption (ICC = 0.9 ��A Max)

- Low Dynamic-Power Consumption (Cpd = 4.8 pF Typ at 3.3 V)

- Low Input Capacitance (CI = 1.5 pF Typ)

- Low Noise �C Overshoot and Undershoot <10% of VCC

- Ioff Supports Partial-Power-Down Mode Operation

- Includes Schmitt-Trigger Inputs

- Wide Operating VCC Range of 0.8 V to 3.6 V

- Optimized for 3.3-V Operation

- 3.6-V I/O Tolerant to Support Mixed-Mode Signal Operation

- tpd = 5.6 ns Max at 3.3 V

- Suitable for Point-to-Point Applications

- Latch-Up Performance Exceeds 100 mA Per JESD 78, Class II

- ESD Performance Tested Per JESD 22

- 2000-V Human-Body Model (A114-B, Class II)

- 1000-V Charged-Device Model (C101)

NanoStar is a trademark of Texas Instruments

- Technology Family

- AUP

- Supply voltage (Min) (V)

- 0.8

- Supply voltage (Max) (V)

- 3.6

- Number of channels (#)

- 1

- Inputs per channel

- 1

- IOL (Max) (mA)

- 4

- IOH (Max) (mA)

- -4

- Input type

- Schmitt-Trigger

- Output type

- Push-Pull

- Features

- Partial power down (Ioff), Over-voltage tolerant inputs, Very high speed (tpd 5-10ns)

- Data rate (Max) (Mbps)

- 100

- Rating

- Catalog

- Operating temperature range (C)

- -40 to 85

SN74AUP1G97�������ͺ��У�SN74AUP1G97DBVR��SN74AUP1G97DBVT��SN74AUP1G97DCKR��SN74AUP1G97DCKT��SN74AUP1G97DRLR��SN74AUP1G97DRYR��SN74AUP1G97DSFR��SN74AUP1G97YFPR��SN74AUP1G97YZPR����������Щ��Ʒ�Ĺؼ������������ɹ����ۣ�

SN74AUP1G97DBVR�������¶ȣ�-40 to 85����װ��SOT-23 (DBV)-6����װ����MPQ��3000����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�SN��TI����SN74AUP1G97DBVR������USD�۸�.106��1000+��

SN74AUP1G97DBVT�������¶ȣ�-40 to 85����װ��SOT-23 (DBV)-6����װ����MPQ��250����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�NIPDAU��TI����SN74AUP1G97DBVT������USD�۸�.306��1000+��

SN74AUP1G97DCKR�������¶ȣ�-40 to 85����װ��SC70 (DCK)-6����װ����MPQ��3000����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�NIPDAU��TI����SN74AUP1G97DCKR������USD�۸�.089��1000+��

SN74AUP1G97DCKT�������¶ȣ�-40 to 85����װ��SC70 (DCK)-6����װ����MPQ��250����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�NIPDAU��TI����SN74AUP1G97DCKT������USD�۸�.306��1000+��

SN74AUP1G97DRLR�������¶ȣ�-40 to 85����װ��SOT-5X3 (DRL)-6����װ����MPQ��4000����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�NIPDAUAG��TI����SN74AUP1G97DRLR������USD�۸�.131��1000+��

SN74AUP1G97DRYR�������¶ȣ�-40 to 85����װ��SON (DRY)-6����װ����MPQ��5000����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�NIPDAU��TI����SN74AUP1G97DRYR������USD�۸�.117��1000+��

SN74AUP1G97DSFR�������¶ȣ�-40 to 85����װ��SON (DSF)-6����װ����MPQ��5000����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�NIPDAUAG��TI����SN74AUP1G97DSFR������USD�۸�.127��1000+��

SN74AUP1G97YFPR�������¶ȣ�PropertyValue����װ��DSBGA (YFP)-6����װ����MPQ��3000����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�SNAGCU��TI����SN74AUP1G97YFPR������USD�۸�.166��1000+��

SN74AUP1G97YZPR�������¶ȣ�-40 to 85����װ��DSBGA (YZP)-6����װ����MPQ��3000����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�SNAGCU��TI����SN74AUP1G97YZPR������USD�۸�.17��1000+��

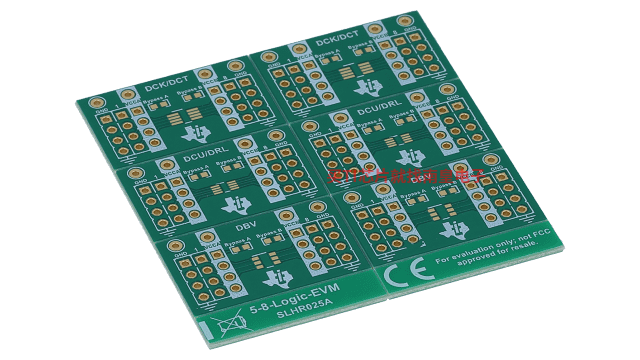

5-8-LOGIC-EVM �� ֧�� 5 �� 8 ���� DCK��DCT��DCU��DRL �� DBV ��װ��ͨ���� EVM

���� EVM �������֧�־��� 5 �� 8 �������Ҳ��� DCK��DCT��DCU��DRL �� DBV ��װ���κ�������