- 制造厂商:TI

- 产品类别:逻辑和电压转换

- 技术类目:触发器、锁存器和寄存器 - 计数器

- 功能描述:同步 4 位二进制计数器

- 点击这里打开及下载SN74F161A的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

This synchronous, presettable, 4-bit binary counter has internal carry look-ahead circuitry for use in high-speed counting designs. Synchronous operation is provided by having all flip-flops clocked simultaneously so that the outputs change coincident with each other when so instructed by the count-enable (ENP, ENT) inputs and internal gating. This mode of operation eliminates the output counting spikes that are normally associated with asynchronous (ripple-clock) counters. However, counting spikes can occur on the ripple-carry (RCO) output. A buffered clock (CLK) input triggers the four flip-flops on the rising (positive-going) edge of CLK.

This counter is fully programmable. That is, it can be preset to any number between 0 and 15. Because presetting is synchronous, a low logic level at the load (LOAD\) input disables the counter and causes the outputs to agree with the setup data after the next clock pulse, regardless of the levels of ENP and ENT.

The clear function is asynchronous, and a low logic level at the clear (CLR\) input sets all four of the flip-flop outputs to low, regardless of the levels of CLK, LOAD\, ENP, and ENT.

The carry look-ahead circuitry provides for cascading counters for n-bit synchronous applications, without additional gating. This function is implemented by the ENP and ENT inputs and an RCO output. Both ENP and ENT must be high to count, and ENT is fed forward to enable RCO. RCO, thus enabled, produces a high-logic-level pulse while the count is 15 (HHHH). The high-logic-level overflow ripple-carry pulse can be used to enable successive cascaded stages. Transitions at ENP or ENT are allowed, regardless of the level of CLK.

The SN74F161A features a fully independent clock circuit. Changes at ENP, ENT, or LOAD\ that modify the operating mode have no effect on the contents of the counter until clocking occurs. The function of the counter (whether enabled, disabled, loading, or counting) is dictated solely by the conditions meeting the setup and hold times.

- Internal Look-Ahead Circuitry for Fast Counting

- Carry Output for N-Bit Cascading

- Fully Synchronous Operation for Counting

- Function

- Counter

- Bits (#)

- 4

- Technology Family

- F

- Supply voltage (Min) (V)

- 4.5

- Supply voltage (Max) (V)

- 5.5

- Input type

- Bipolar

- Output type

- Push-Pull

- Features

- Very high speed (tpd 5-10ns)

SN74F161A的完整型号有:SN74F161AD、SN74F161ADR、SN74F161AN、SN74F161ANSR,以下是这些产品的关键参数及官网采购报价:

SN74F161AD,工作温度:0 to 70,封装:SOIC (D)-16,包装数量MPQ:40个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN74F161AD的批量USD价格:.379(1000+)

SN74F161ADR,工作温度:0 to 70,封装:SOIC (D)-16,包装数量MPQ:2500个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN74F161ADR的批量USD价格:.179(1000+)

SN74F161AN,工作温度:0 to 70,封装:PDIP (N)-16,包装数量MPQ:25个,MSL 等级/回流焊峰值温度:N/A for Pkg Type,引脚镀层/焊球材料:NIPDAU,TI官网SN74F161AN的批量USD价格:.206(1000+)

SN74F161ANSR,工作温度:0 to 70,封装:SO (NS)-16,包装数量MPQ:2000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN74F161ANSR的批量USD价格:.197(1000+)

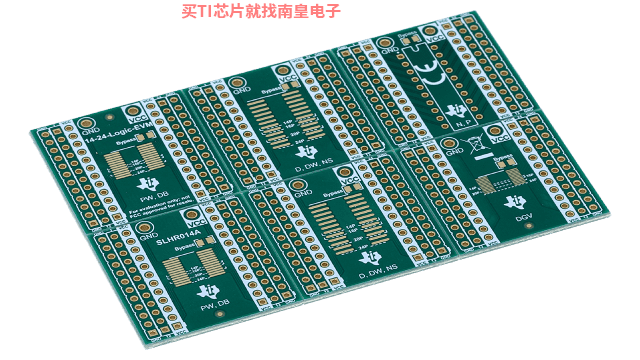

14-24-LOGIC-EVM ― 支持 14 到 24 引脚 PW、DB、D、DW、NS、DYY 和 DGV 封装的通用逻辑 EVM

该 EVM 设计用于支持采用 14 至 24 引脚 D、DW、DB、NS、PW、DYY 或 DGV 封装的任何逻辑器件。