- 制造厂商:TI

- 产品类别:逻辑和电压转换

- 技术类目:触发器、锁存器和寄存器 - 移位寄存器

- 功能描述:汽车类 8 位串行输入/并行输出移位寄存器

- 点击这里打开及下载SN74HCS596-Q1的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

The SN74HCS596-Q1 device contains an 8-bit, serial-in, parallel-out shift register that feeds an 8-bit D-type storage register. All inputs include Schmitt-triggers, eliminating any erroneous data outputs due to slow-edged or noisy input signals. The storage register has parallel open-drain outputs. Separate clocks are provided for both the shift and storage register. The shift register has a direct overriding clear (SRCLR) input, serial (SER) input, and a serial output (QH’) for cascading. When the output-enable (OE) input is high, the outputs are in a high-impedance state. Internal register data is not impacted by the operation of the OE input.

- AEC-Q100 Qualified for automotive applications:

- Device temperature grade 1: –40°C to +125°C, TA

- Device HBM ESD Classification Level 2

- Device CDM ESD Classifcation Level C6

- Wide operating voltage range: 2 V to 6 V

- Schmitt-trigger inputs allow for slow or noisy input signals

- Low power consumption

- Typical ICC of 100 nA

- Typical input leakage current of ±100 nA

- ±7.8-mA output drive at 6 V

- Configuration

- Serial-in, Parallel-out

- Bits (#)

- 8

- Technology Family

- HCS

- Supply voltage (Min) (V)

- 2

- Supply voltage (Max) (V)

- 6

- Input type

- Schmitt-Trigger

- Output type

- Open-Drain

- Clock Frequency (MHz)

- 75

- IOL (Max) (mA)

- 7.8

- IOH (Max) (mA)

- -7.8

- ICC (Max) (uA)

- 2

- Features

- Balanced outputs, High speed (tpd 10-50ns), Positive input clamp diode, Output register

SN74HCS596-Q1的完整型号有:SN74HCS596QDRQ1、SN74HCS596QPWRQ1,以下是这些产品的关键参数及官网采购报价:

SN74HCS596QDRQ1,工作温度:-40 to 125,封装:SOIC (D)-16,包装数量MPQ:2500个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN74HCS596QDRQ1的批量USD价格:.189(1000+)

SN74HCS596QPWRQ1,工作温度:-40 to 125,封装:TSSOP (PW)-16,包装数量MPQ:2000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN74HCS596QPWRQ1的批量USD价格:.189(1000+)

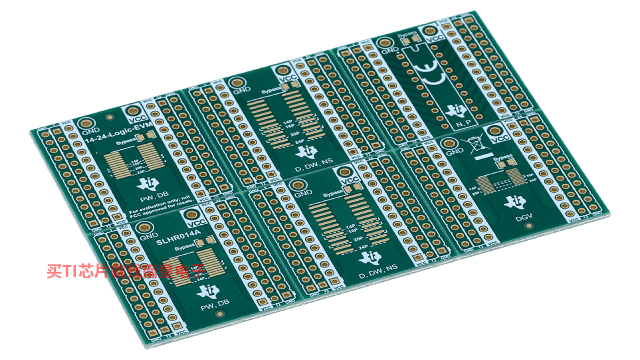

14-24-LOGIC-EVM — 支持 14 到 24 引脚 PW、DB、D、DW、NS、DYY 和 DGV 封装的通用逻辑 EVM

该 EVM 设计用于支持采用 14 至 24 引脚 D、DW、DB、NS、PW、DYY 或 DGV 封装的任何逻辑器件。