- 制造厂商:TI

- 产品类别:逻辑和电压转换

- 技术类目:缓冲器、驱动器和收发器 - 同相缓冲器和驱动器

- 功能描述:具有三态输出的 4 通道、4.75V 至 5.25V 双极缓冲器

- 点击这里打开及下载SN74LS125A的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

These bus buffers feature three-state outputs that, when enabled, have the low impedance characteristics of a TTL output with additional drive capability at high logic levels to permit driving heavily loaded bus lines without external pullup resistors. When disabled, both output transistors are turned off, presenting a high-impedance state to the bus so the output will act neither as a significant load nor as a driver. The ’125 and ’LS125A devices’ outputs are disabled when G\ is high. The ’126 and ’LS126A devices’ outputs are disabled when G is low.

- Quad Bus Buffers

- 3-State Outputs

- Separate Control for Each Channel

The SN54125, SN54126, SN74125, SN74126, and SN54LS126A are obsolete and are no longer supplied.

- Technology Family

- LS

- Supply voltage (Min) (V)

- 4.75

- Supply voltage (Max) (V)

- 5.25

- Number of channels (#)

- 4

- IOL (Max) (mA)

- 24

- ICC (Max) (uA)

- 22000

- IOH (Max) (mA)

- -2.6

- Input type

- Bipolar

- Output type

- 3-State

- Features

- High speed (tpd 10-50ns), Input clamp diode

- Rating

- Catalog

SN74LS125A的完整型号有:SN74LS125AD、SN74LS125ADBR、SN74LS125ADR、SN74LS125AN、SN74LS125ANSR,以下是这些产品的关键参数及官网采购报价:

SN74LS125AD,工作温度:0 to 70,封装:SOIC (D)-14,包装数量MPQ:50个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN74LS125AD的批量USD价格:.268(1000+)

SN74LS125ADBR,工作温度:0 to 70,封装:SSOP (DB)-14,包装数量MPQ:2000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN74LS125ADBR的批量USD价格:.312(1000+)

SN74LS125ADR,工作温度:0 to 70,封装:SOIC (D)-14,包装数量MPQ:2500个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN74LS125ADR的批量USD价格:.223(1000+)

SN74LS125AN,工作温度:0 to 70,封装:PDIP (N)-14,包装数量MPQ:25个,MSL 等级/回流焊峰值温度:N/A for Pkg Type,引脚镀层/焊球材料:NIPDAU,TI官网SN74LS125AN的批量USD价格:.256(1000+)

SN74LS125ANSR,工作温度:0 to 70,封装:SO (NS)-14,包装数量MPQ:2000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN74LS125ANSR的批量USD价格:.245(1000+)

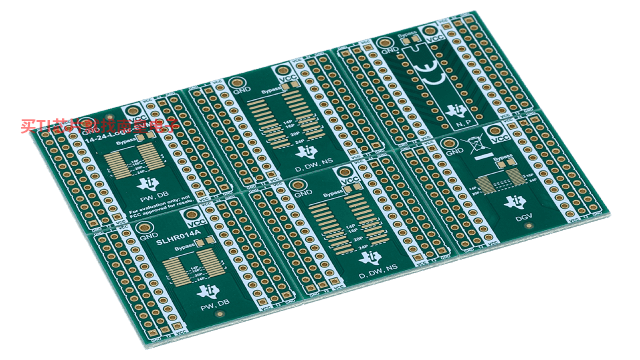

14-24-LOGIC-EVM ― 支持 14 到 24 引脚 PW、DB、D、DW、NS、DYY 和 DGV 封装的通用逻辑 EVM

该 EVM 设计用于支持采用 14 至 24 引脚 D、DW、DB、NS、PW、DYY 或 DGV 封装的任何逻辑器件。