- 制造厂商:TI

- 产品类别:逻辑和电压转换

- 技术类目:缓冲器、驱动器和收发器 - 同相缓冲器和驱动器

- 功能描述:具有三态输出的 8 通道、2V 至 5.5V 缓冲器

- 点击这里打开及下载SN74LV244A的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

The SN74LV244A octal buffers and line drivers are designed for 2-V to 5.5-V VCC operation.

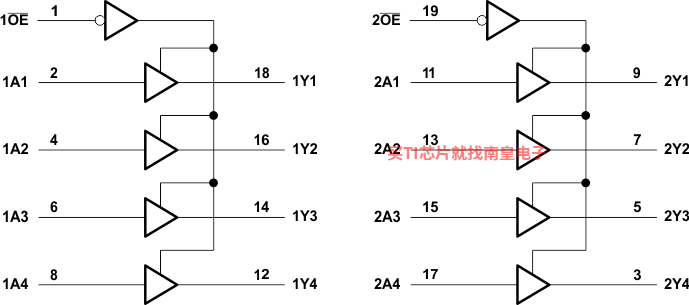

The SN74LV244A devices are designed specifically to improve both performance and density of the 3-state memory address drivers, clock drivers, and bus-oriented receivers and transmitters. These devices are organized as two 4-bit line drivers with separate output-enable (OE) inputs.

- 2-V to 5.5-V VCC Operation

- Max tpd of 6.5 ns at 5 V

- Typical VOLP (Output Ground Bounce) <0.8 V at VCC = 3.3 V, TA = 25°C

- Typical VOHV (Output VOH Undershoot) >2.3 V at VCC = 3.3 V, TA = 25°C

- Support Mixed-Mode Voltage Operation on All Ports

- Ioff Supports Partial-Power-Down Mode Operation

- Latch-Up Performance Exceeds 250-mA Per JESD 17

- ESD Protection Exceeds JESD 22

- 2000-V Human-Body Model (A114-A)

- 200-V Machine Model (A115-A)

- 1000-V Charged-Device Model (C101)

- Technology Family

- LV-A

- Supply voltage (Min) (V)

- 2

- Supply voltage (Max) (V)

- 5.5

- Number of channels (#)

- 8

- IOL (Max) (mA)

- 16

- ICC (Max) (uA)

- 20

- IOH (Max) (mA)

- -16

- Input type

- Standard CMOS

- Output type

- 3-State

- Features

- Balanced outputs, Very high speed (tpd 5-10ns), Partial power down (Ioff), Over-voltage tolerant inputs

- Rating

- Catalog

SN74LV244A的完整型号有:SN74LV244ADBR、SN74LV244ADGVR、SN74LV244ADW、SN74LV244ADWR、SN74LV244ANSR、SN74LV244APW、SN74LV244APWR、SN74LV244APWRG3、SN74LV244APWRG4、SN74LV244APWT、SN74LV244ARGYR,以下是这些产品的关键参数及官网采购报价:

SN74LV244ADBR,工作温度:-40 to 125,封装:SSOP (DB)-20,包装数量MPQ:2000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN74LV244ADBR的批量USD价格:.202(1000+)

SN74LV244ADGVR,工作温度:-40 to 125,封装:TVSOP (DGV)-20,包装数量MPQ:2000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN74LV244ADGVR的批量USD价格:.184(1000+)

SN74LV244ADW,工作温度:-40 to 125,封装:SOIC (DW)-20,包装数量MPQ:25个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN74LV244ADW的批量USD价格:.384(1000+)

SN74LV244ADWR,工作温度:-40 to 125,封装:SOIC (DW)-20,包装数量MPQ:2000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN74LV244ADWR的批量USD价格:.202(1000+)

SN74LV244ANSR,工作温度:-40 to 125,封装:SO (NS)-20,包装数量MPQ:2000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN74LV244ANSR的批量USD价格:.202(1000+)

SN74LV244APW,工作温度:-40 to 125,封装:TSSOP (PW)-20,包装数量MPQ:70个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN74LV244APW的批量USD价格:.384(1000+)

SN74LV244APWR,工作温度:-40 to 125,封装:TSSOP (PW)-20,包装数量MPQ:2000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:SN,TI官网SN74LV244APWR的批量USD价格:.184(1000+)

SN74LV244APWRG3,工作温度:-40 to 125,封装:TSSOP (PW)-20,包装数量MPQ:2000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:SN,TI官网SN74LV244APWRG3的批量USD价格:.212(1000+)

SN74LV244APWRG4,工作温度:-40 to 125,封装:TSSOP (PW)-20,包装数量MPQ:2000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN74LV244APWRG4的批量USD价格:.212(1000+)

SN74LV244APWT,工作温度:-40 to 125,封装:TSSOP (PW)-20,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN74LV244APWT的批量USD价格:.384(1000+)

SN74LV244ARGYR,工作温度:-40 to 125,封装:VQFN (RGY)-20,包装数量MPQ:3000个,MSL 等级/回流焊峰值温度:Level-2-260C-1 YEAR,引脚镀层/焊球材料:NIPDAU,TI官网SN74LV244ARGYR的批量USD价格:.193(1000+)

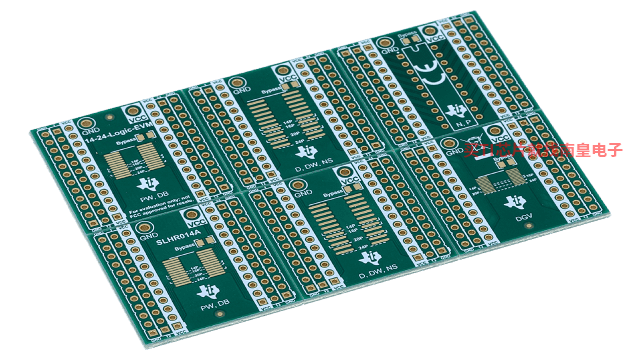

14-24-LOGIC-EVM ― 支持 14 到 24 引脚 PW、DB、D、DW、NS、DYY 和 DGV 封装的通用逻辑 EVM

该 EVM 设计用于支持采用 14 至 24 引脚 D、DW、DB、NS、PW、DYY 或 DGV 封装的任何逻辑器件。

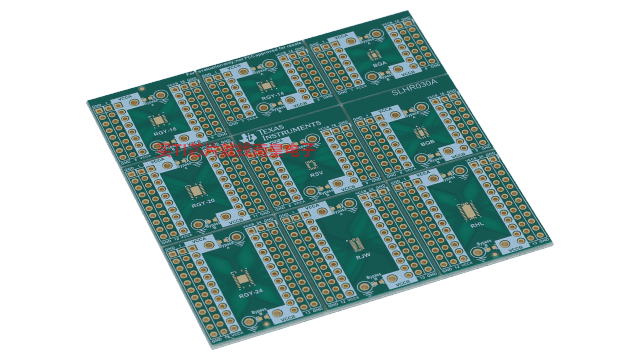

14-24-NL-LOGIC-EVM ― Generic 14 through 24 pin non-leaded package evaluation module

Flexible EVM designed to support any logic or translation device that has a BQA, BQB, RGY (14-24 pin), RSV, RJW, or RHL package.SN74LV244A IBIS Model (Rev. A)

BiSS C 主协议在工业通信子系统上的实施 (PRU-ICSS)。该设计提供可编程实时单元 (PRU) 的完整文档和源代码。TIDEP0035 ― 具有集成 HIPERFACE DSL 主接口的 ARM MPU 参考设计

该参考设计在工业通信子系统 (PRU-ICSS) 上实现了 HIPERFACE DSL 主协议。利用两线制接口,可以将位置反馈线集成到电机电缆中。该参考设计包含 AM437x PRU-ICSS 固件和 TIDA-00177 收发器参考设计。TIDEP0050 ― EnDat 2.2 系统参考设计

此参考设计基于 HEIDENHAIN EnDat 2.2 标准针对位置或旋转编码器实现了 EnDat 2.2 主协议栈和硬件接口。此设计由 EnDat 2.2 主协议栈、使用 RS-485 收发器的半双工通信,以及在 Sitara AM437x 工业开发工具包上实现的线路终端组成。此设计经过充分测试,符合 HEIDENHAIN EnDat 2.2 标准。除了 EnDat 位置反馈之外,AM437x IDK 还能够支持工业通信和电机驱动,如 AM437x 单芯片电机控制设计指南中所述。TIDEP0054 ― 适用于变电站自动化的并行冗余协议 (PRP) 以太网参考设计

此参考设计为智能电网输电和配电网络中的变电站自动化设备提供高可靠性、低延迟网络通信。它支持 IEC 62439 标准中使用 PRU-ICSS 的并行冗余协议 (PRP) 规范。此参考设计是 FPGA 方法的较低成本替代方法,可提供在无需额外组件的情况下添加 IEC 61850 支持等功能的灵活性和性能。