- 制造厂商:TI

- 产品类别:逻辑和电压转换

- 技术类目:逻辑门 - 与非门

- 功能描述:具有施密特触发输入的 2 通道、2 输入、1.65V 至 5.5V 与非门

- 点击这里打开及下载SN74LVC2G132的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

This dual 2-input NAND gate with Schmitt-trigger inputs is designed for 1.65-V to 5.5-V VCC operation.

The SN74LVC2G132 contains two inverters and performs the Boolean function Y = A ⋅ B or Y = A + B in positive logic. The device functions as two independent inverters, but because of Schmitt action, it has different input threshold levels for positive-going (VT+) and negative-going (VT-) signals.

NanoFree™ package technology is a major breakthrough in IC packaging concepts, using the die as the package.

This device can be triggered from the slowest of input ramps and still give clean jitter-free output signals.

This device is fully specified for partial-power-down applications using Ioff. The Ioff circuitry disables the outputs, preventing damaging current backflow through the device when it is powered down.

- Available in Texas Instruments NanoFree Package

- Supports 5-V VCC Operation

- Inputs Accept Voltages to 5.5 V

- Max tpd of 5.3 ns at 3.3 V

- Low Power Consumption, 10-μA Max ICC

- ±24-mA Output Drive at 3.3 V

- Typical VOLP (Output Ground Bounce) <0.8 V at VCC = 3.3 V, TA = 25°C

- Typical VOHV (Output VOH Undershoot) >2 V at VCC = 3.3 V, TA = 25°C

- Ioff Supports Live Insertion, Partial Power Down Mode, and Back Drive Protection

- Support Translation Down (5V to 3.3V and 3.3V to 1.8V)

- Latch-Up Performance Exceeds 100 mA Per JESD 78, Class II

- ESD Protection Exceeds JESD 22

- 2000-V Human-Body Model (A114-A)

- 200-V Machine Model (A115-A)

- 1000-V Charged-Device Model (C101)

- Technology Family

- LVC

- Supply voltage (Min) (V)

- 1.65

- Supply voltage (Max) (V)

- 5.5

- Number of channels (#)

- 2

- Inputs per channel

- 2

- IOL (Max) (mA)

- 32

- IOH (Max) (mA)

- -32

- Input type

- Schmitt-Trigger

- Output type

- Push-Pull

- Features

- Partial power down (Ioff), Over-voltage tolerant inputs, Ultra high speed (tpd <5ns)

- Data rate (Max) (Mbps)

- 100

- Rating

- Catalog

SN74LVC2G132的完整型号有:74LVC2G132DCURG4、74LVC2G132DCUTG4、SN74LVC2G132DCTR、SN74LVC2G132DCUR、SN74LVC2G132DCUT、SN74LVC2G132YZPR,以下是这些产品的关键参数及官网采购报价:

74LVC2G132DCURG4,工作温度:-40 to 125,封装:VSSOP (DCU)-8,包装数量MPQ:3000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网74LVC2G132DCURG4的批量USD价格:.205(1000+)

74LVC2G132DCUTG4,工作温度:PropertyValue,封装:VSSOP (DCU)-8,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网74LVC2G132DCUTG4的批量USD价格:.405(1000+)

SN74LVC2G132DCTR,工作温度:-40 to 125,封装:SM8 (DCT)-8,包装数量MPQ:3000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN74LVC2G132DCTR的批量USD价格:.172(1000+)

SN74LVC2G132DCUR,工作温度:-40 to 125,封装:VSSOP (DCU)-8,包装数量MPQ:3000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN74LVC2G132DCUR的批量USD价格:.126(1000+)

SN74LVC2G132DCUT,工作温度:-40 to 125,封装:VSSOP (DCU)-8,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:NIPDAU,TI官网SN74LVC2G132DCUT的批量USD价格:.378(1000+)

SN74LVC2G132YZPR,工作温度:-40 to 85,封装:DSBGA (YZP)-8,包装数量MPQ:3000个,MSL 等级/回流焊峰值温度:Level-1-260C-UNLIM,引脚镀层/焊球材料:SNAGCU,TI官网SN74LVC2G132YZPR的批量USD价格:.238(1000+)

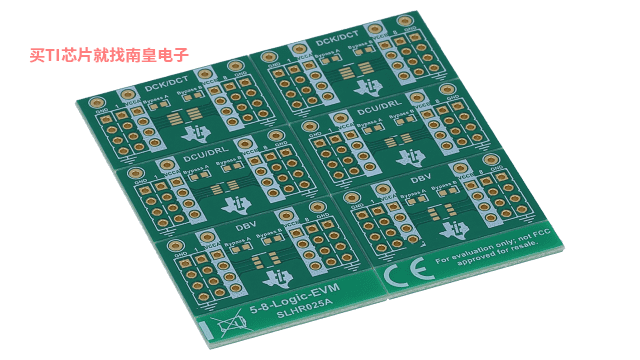

5-8-LOGIC-EVM ― 支持 5 至 8 引脚 DCK、DCT、DCU、DRL 和 DBV 封装的通用逻辑 EVM

灵活的 EVM 设计用于支持具有 5 至 8 引脚数且采用 DCK、DCT、DCU、DRL 或 DBV 封装的任何器件。SN74LVC2G132 IBIS Model (Rev. A)

CAN 和 CANopen 是传统现场总线协议,适用于工厂自动化中的许多应用。只要高电压有可能损坏终端设备,就需要隔离器件。此隔离式 CAN 灵活数据 (FD) 速率中继器参考设计在两个 CAN 总线段之间增加了电气隔离。总线段任一侧的 CAN 帧都被中继到另一侧。该设计中的 CAN 收发器和仲裁逻辑支持高达 2Mbps 的 CAN FD 速度。本参考设计由 6V 至 36V 的宽电压电源供电。TIDA-010049 ― 适用于 IEC 61508 (SIL-2) 且经 TUV 评估的数字输入参考设计

该 8 通道、组隔离式、数字输入模块参考设计聚焦于需要工业功能安全的应用。该设计实现了诊断功能,以帮助检测永久和瞬态随机硬件故障。该输入模块的概念已经过 TUEV SUED (TÜV SÜD) 的评估,可帮助设计人员满足 IEC61508-2:2010 (SIL2) 和 EN13849-1:2015 (Cat2 PLd) 系统合规性要求。此外,该设计还具有 0 硬件容错 (HFT) 能力(1oo1D 架构),并且具有设计用于符合 IEC61131-2(1 类)建议的数字输入。TIDEP0076 ― 基于 AM572x 处理器并采用 DLP 结构光的 3D 机器视觉参考设计

TIDEP0076 3D 机器视觉设计介绍了基于结构光原理的嵌入式 3D 扫描仪。将数码相机与 Sitara™ AM57xx 处理器片上系统 (SoC) 搭配使用,采集来自基于 DLP4500 的投影仪的反射光图形。可在 AM57xx 处理器 SoC 内执行已采集图形的后续处理,并计算物体的 3D 点云及其 3D 可视化。此设计提供了一款嵌入式解决方案,在基于主机 PC 的实施中具有功率、简洁性、成本和尺寸方面的优势。TIDEP0046 ― 关于 AM57x 使用 OpenCL 实现 DSP 加速的蒙特卡罗模拟参考设计

TI 基于 ARM Cortex-A15 的高性能 AM57x 处理器还集成了 C66x DSP。这些 DSP 旨在处理工业、汽车和金融应用中通常需要的高信号和数据处理任务。AM57x OpenCL 实施方案便于用户利用 DSP 加速来执行高度计算任务,同时使用标准编程模型和语言,从而无需深度了解 DSP 架构。TIDEP0046 TI 参考设计举例说明了如何使用 DSP 加速来利用标准 C/C++ 代码生成极长的普通随机数序列。TIDEP0047 ― 采用 TI AM57x 处理器时的电源和散热设计注意事项参考设计

这是一个基于 AM57x 处理器和配套的 TPS659037 电源管理集成电路 (PMIC) 的参考设计。此设计特别强调了使用 AM57x 和 TPS659037 设计的系统的重要电源和热设计注意事项和技术。它包括有关电源管理设计、配电网络 (PDN) 设计注意事项、热设计注意事项、估计功耗和功耗摘要的参考资料和文档。