- жЦдьГЇЩЬЃКTI

- ВњЦЗРрБ№ЃКТпМКЭЕчбЙзЊЛЛ

- ММЪѕРрФПЃКЛКГхЦїЁЂЧ§ЖЏЦїКЭЪеЗЂЦї - ЗДЯђЛКГхЦїКЭЧ§ЖЏЦї

- ЙІФмУшЪіЃКОпгазмЯпБЃГжЁЂTTL МцШнаЭ CMOS ЪфШыКЭШ§ЬЌЪфГіЕФ 8 ЭЈЕРЁЂ2.7V жС 3.6V ЗДЯрЦї

- ЕуЛїетРяДђПЊМАЯТдиSN74LVTH240ЕФММЪѕЮФЕЕзЪСЯ

- TIДњРэЧўЕРЃЌЬсЙЉЕБШеЗЂЛѕЁЂбЯИёЕФжЪСПБъзМЃЌТњзуФњЕФФПБъМлИё

These octal buffers and line drivers are designed specifically for low-voltage (3.3-V) VCC operation, but with the capability to provide a TTL interface to a 5-V system environment.

These devices are organized as two 4-bit buffer/line drivers with separate output-enable (OE)\ inputs. When OE\ is low, the devices pass data from the A inputs to the Y outputs. When OE\ is high, the outputs are in the high-impedance state.

To ensure the high-impedance state during power up or power down, OE\ should be tied to VCC through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

Active bus-hold circuitry holds unused or undriven inputs at a valid logic state. Use of pullup or pulldown resistors with the bus-hold circuitry is not recommended.

These devices are fully specified for hot-insertion applications using Ioff and power-up 3-state. The Ioff circuitry disables the outputs, preventing damaging current backflow through the devices when they are powered down. The power-up 3-state circuitry places the outputs in the high-impedance state during power up and power down, which prevents driver conflict.

- Support Mixed-Mode Signal Operation (5-V Input and Output Voltages With 3.3-V VCC)

- Support Unregulated Battery Operation Down to 2.7 V

- Typical VOLP (Output Ground Bounce) <0.8 V at VCC = 3.3 V, TA = 25ЁуC

- Ioff and Power-Up 3-State Support Hot Insertion

- Bus Hold on Data Inputs Eliminates the Need for External Pullup/Pulldown Resistors

- Latch-Up Performance Exceeds 500 mA Per JESD 17

- ESD Protection Exceeds JESD 22

- 2000-V Human-Body Model (A114-A)

- 200-V Machine Model (A115-A)

- Technology Family

- LVT

- Supply voltage (Min) (V)

- 2.7

- Supply voltage (Max) (V)

- 3.6

- Number of channels (#)

- 8

- IOL (Max) (mA)

- 64

- IOH (Max) (mA)

- -32

- ICC (Max) (uA)

- 5000

- Input type

- TTL-Compatible CMOS

- Output type

- 3-State

- Features

- Ultra high speed (tpd <5ns), Partial power down (Ioff), Over-voltage tolerant inputs, Power up 3-state, Bus-hold

- Rating

- Catalog

SN74LVTH240ЕФЭъећаЭКХгаЃКSN74LVTH240DBRЁЂSN74LVTH240DWЁЂSN74LVTH240DWRЁЂSN74LVTH240NSRЁЂSN74LVTH240PWЁЂSN74LVTH240PWRЃЌвдЯТЪЧетаЉВњЦЗЕФЙиМќВЮЪ§МАЙйЭјВЩЙКБЈМлЃК

SN74LVTH240DBRЃЌЙЄзїЮТЖШЃК-40 to 85ЃЌЗтзАЃКSSOP (DB)-20ЃЌАќзАЪ§СПMPQЃК2000ИіЃЌMSL ЕШМЖ/ЛиСїКИЗхжЕЮТЖШЃКLevel-1-260C-UNLIMЃЌв§НХЖЦВу/КИЧђВФСЯЃКNIPDAUЃЌTIЙйЭјSN74LVTH240DBRЕФХњСПUSDМлИёЃК.331ЃЈ1000+ЃЉ

SN74LVTH240DWЃЌЙЄзїЮТЖШЃК-40 to 85ЃЌЗтзАЃКSOIC (DW)-20ЃЌАќзАЪ§СПMPQЃК25ИіЃЌMSL ЕШМЖ/ЛиСїКИЗхжЕЮТЖШЃКLevel-1-260C-UNLIMЃЌв§НХЖЦВу/КИЧђВФСЯЃКNIPDAUЃЌTIЙйЭјSN74LVTH240DWЕФХњСПUSDМлИёЃК.361ЃЈ1000+ЃЉ

SN74LVTH240DWRЃЌЙЄзїЮТЖШЃК-40 to 85ЃЌЗтзАЃКSOIC (DW)-20ЃЌАќзАЪ§СПMPQЃК2000ИіЃЌMSL ЕШМЖ/ЛиСїКИЗхжЕЮТЖШЃКLevel-1-260C-UNLIMЃЌв§НХЖЦВу/КИЧђВФСЯЃКNIPDAUЃЌTIЙйЭјSN74LVTH240DWRЕФХњСПUSDМлИёЃК.301ЃЈ1000+ЃЉ

SN74LVTH240NSRЃЌЙЄзїЮТЖШЃК-40 to 85ЃЌЗтзАЃКSO (NS)-20ЃЌАќзАЪ§СПMPQЃК2000ИіЃЌMSL ЕШМЖ/ЛиСїКИЗхжЕЮТЖШЃКLevel-1-260C-UNLIMЃЌв§НХЖЦВу/КИЧђВФСЯЃКNIPDAUЃЌTIЙйЭјSN74LVTH240NSRЕФХњСПUSDМлИёЃК.331ЃЈ1000+ЃЉ

SN74LVTH240PWЃЌЙЄзїЮТЖШЃК-40 to 85ЃЌЗтзАЃКTSSOP (PW)-20ЃЌАќзАЪ§СПMPQЃК70ИіЃЌMSL ЕШМЖ/ЛиСїКИЗхжЕЮТЖШЃКLevel-1-260C-UNLIMЃЌв§НХЖЦВу/КИЧђВФСЯЃКNIPDAUЃЌTIЙйЭјSN74LVTH240PWЕФХњСПUSDМлИёЃК.361ЃЈ1000+ЃЉ

SN74LVTH240PWRЃЌЙЄзїЮТЖШЃК-40 to 85ЃЌЗтзАЃКTSSOP (PW)-20ЃЌАќзАЪ§СПMPQЃК2000ИіЃЌMSL ЕШМЖ/ЛиСїКИЗхжЕЮТЖШЃКLevel-1-260C-UNLIMЃЌв§НХЖЦВу/КИЧђВФСЯЃКNIPDAUЃЌTIЙйЭјSN74LVTH240PWRЕФХњСПUSDМлИёЃК.301ЃЈ1000+ЃЉ

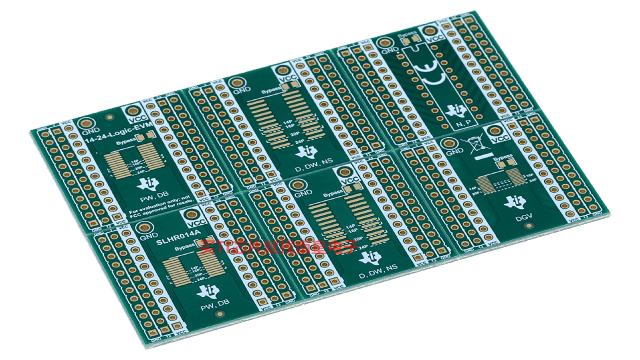

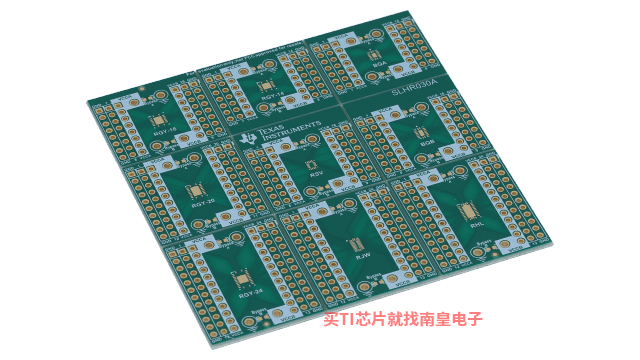

14-24-LOGIC-EVM ЁЊ жЇГж 14 ЕН 24 в§НХ PWЁЂDBЁЂDЁЂDWЁЂNSЁЂDYY КЭ DGV ЗтзАЕФЭЈгУТпМ EVM

ИУ EVM ЩшМЦгУгкжЇГжВЩгУ 14 жС 24 в§НХ DЁЂDWЁЂDBЁЂNSЁЂPWЁЂDYY Лђ DGV ЗтзАЕФШЮКЮТпМЦїМўЁЃ

14-24-NL-LOGIC-EVM ЁЊ Generic 14 through 24 pin non-leaded package evaluation module

Flexible EVM designed to support any logic or translation device that has a BQA, BQB, RGY (14-24 pin), RSV, RJW, or RHL package.