- ÷Τ‘λ≥ß…ΧΘΚTI

- ≤ζΤΖάύ±πΘΚΫ”ΩΎ

- ΦΦ θάύΡΩΘΚΤδΥϊΫ”ΩΎ

- ΙΠΡήΟη ωΘΚFlatLink Ϋ” ’Τς

- ΒψΜς’βάο¥ρΩΣΦΑœ¬‘ΊSN75LVDS82ΒΡΦΦ θΈΡΒΒΉ Νœ

- TI¥ζάμ«ΰΒάΘ§ΧαΙ©Β±»’ΖΔΜθΓΔ―œΗώΒΡ÷ ΝΩ±ξΉΦΘ§¬ζΉψΡζΒΡΡΩ±ξΦέΗώ

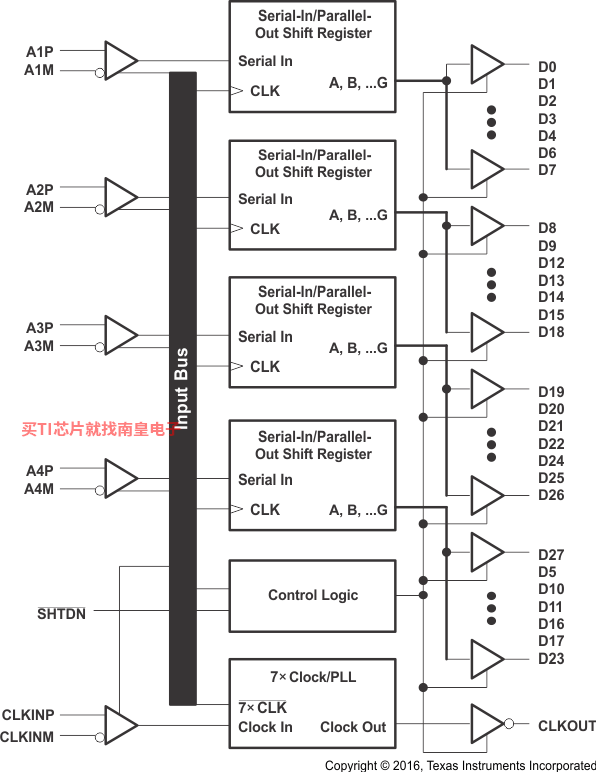

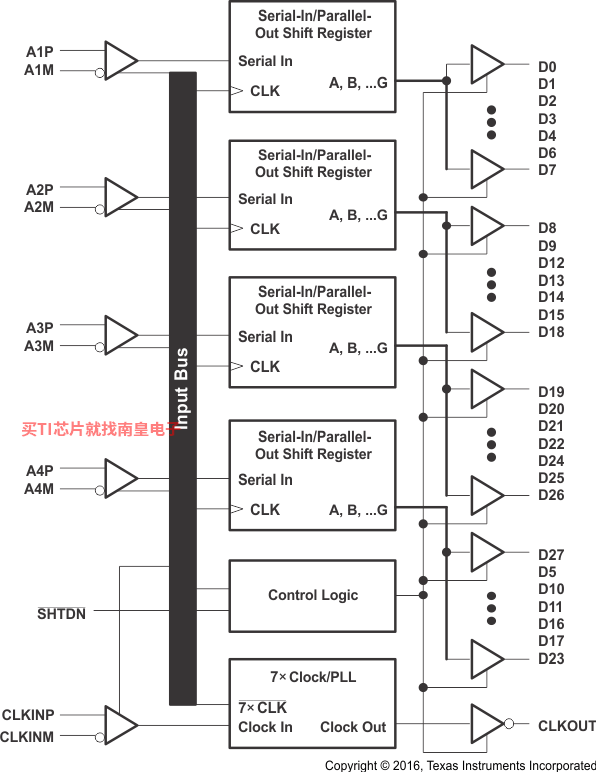

The SN75LVDS82 FlatLink™ receiver contains four serial-in, 7-bit parallel-out shift registers, a 7× clock synthesizer, and five low-voltage differential signaling (LVDS) line receivers in a single integrated circuit.

These functions allow receipt of synchronous data from a compatible transmitter, such as the SN75LVDS83B, over five balanced-pair conductors, and expansion to 28 bits of single-ended low-voltage TTL (LVTTL) synchronous data at a lower transfer rate. The SN75LVDS82 can also be used with the SN75LVDS84 for 21-bit transfers.

When receiving, the high-speed LVDS data is received and loaded into registers at the rate of seven times (7×) the LVDS input clock (CLKIN). The data is then unloaded to a 28-bit-wide LVTTL parallel bus at the CLKIN rate. A phase-locked loop (PLL) clock synthesizer circuit generates a 7× clock for internal clocking and an output clock for the expanded data. The SN75LVDS82 presents valid data on the falling edge of the output clock (CLKOUT).

The SN75LVDS82 requires only five line-termination resistors for the differential inputs and little or no control. The data bus appears the same at the input to the transmitter and output of the receiver with the data transmission transparent to the user.

The only possible user intervention is the use of the shutdown/clear (SHTDN) active-low input to inhibit the clock and shut off the LVDS receivers for lower power consumption. A low-level on SHTDN clears all internal registers to a low level and places the TTL outputs in a high-impedance state.

The SN75LVDS82 is characterized for operation over ambient air temperatures of 0°C to 70°C.

- 4:28 Data Channel Expansion at up to 1904 MbpsThroughput

- Suited for SVGA, XGA, or SXGA Display Data Transmission From Controller to Display With Very Low EMI

- Four Data Channels and Clock Low-Voltage Differential Channels In and 28 Data and Clock Low-Voltage TTL Channels Out

- Operates From a Single 3.3-V Supply With 250 mW (Typical)

- 5-V Tolerant SHTDN Input

- Falling Clock-Edge-Triggered Outputs

- Packaged in Thin Shrink Small-Outline Package (TSSOP) With 20-Mil Terminal Pitch

- Consumes Less Than 1 mW When Disabled

- Pixel Clock Frequency Range of 31 MHz to 68 MHz

- No External Components Required for PLL

- Inputs Meet or Exceed the Requirements of ANSI EIA/TIA-644 Standard

- Operating temperature range (C)

- 0 to 70

SN75LVDS82ΒΡΆξ’ϊ–ΆΚ≈”–ΘΚSN75LVDS82DGGΓΔSN75LVDS82DGGRΘ§“‘œ¬ «’β–©≤ζΤΖΒΡΙΊΦϋ≤Έ ΐΦΑΙΌΆχ≤…ΙΚ±®ΦέΘΚ

SN75LVDS82DGGΘ§ΙΛΉςΈ¬Ε»ΘΚ0 to 70Θ§ΖβΉΑΘΚTSSOP (DGG)-56Θ§ΑϋΉΑ ΐΝΩMPQΘΚ35ΗωΘ§MSL Β»ΦΕ/ΜΊΝςΚΗΖε÷ΒΈ¬Ε»ΘΚLevel-2-260C-1 YEARΘ§“ΐΫ≈ΕΤ≤ψ/ΚΗ«ρ≤ΡΝœΘΚNIPDAUΘ§TIΙΌΆχSN75LVDS82DGGΒΡ≈ζΝΩUSDΦέΗώΘΚ2.5Θ®1000+Θ©

SN75LVDS82DGGRΘ§ΙΛΉςΈ¬Ε»ΘΚ0 to 70Θ§ΖβΉΑΘΚTSSOP (DGG)-56Θ§ΑϋΉΑ ΐΝΩMPQΘΚ2000ΗωΘ§MSL Β»ΦΕ/ΜΊΝςΚΗΖε÷ΒΈ¬Ε»ΘΚLevel-2-260C-1 YEARΘ§“ΐΫ≈ΕΤ≤ψ/ΚΗ«ρ≤ΡΝœΘΚNIPDAUΘ§TIΙΌΆχSN75LVDS82DGGRΒΡ≈ζΝΩUSDΦέΗώΘΚ2.1Θ®1000+Θ©

SN75LVDS82 IBIS Model

PSpice for TI Ω…ΧαΙ©Αο÷ζΤάΙάΡΘΡβΒγ¬ΖΙΠΡήΒΡ…ηΦΤΚΆΖ¬’φΜΖΨ≥ΓΘ¥ΥΙΠΡήΤκ»ΪΒΡ…ηΦΤΚΆΖ¬’φΧΉΦΰ Ι”Ο Cadence ΒΡΡΘΡβΖ÷Έω“ΐ«φΓΘPSpice for TI Ω…ΟβΖ― Ι”ΟΘ§Αϋά®“ΒΡΎ≥§¥σΒΡΡΘ–ΆΩβ÷°“ΜΘ§Κ≠Η«Έ“Ο«ΒΡΡΘΡβΚΆΒγ‘¥≤ζΤΖœΒΝ–“‘ΦΑΨΪ―ΓΒΡΡΘΡβ––ΈΣΡΘ–ΆΓΘΫη÷ζ?PSpice for TI ΒΡ…ηΦΤΚΆΖ¬’φΜΖΨ≥ΦΑΤδΡΎ÷ΟΒΡΡΘ–ΆΩβΘ§ΡζΩ…Ε‘Η¥‘”ΒΡΜλΚœ–≈Κ≈…ηΦΤΫχ––Ζ¬’φΓΘ¥¥Ϋ®Άξ’ϊΒΡ÷’ΕΥ…η±Η…ηΦΤΚΆ‘≠–ΆΫβΨωΖΫΑΗΘ§»ΜΚσ‘ΌΫχ––≤ΦΨ÷ΚΆ÷Τ‘λΘ§Ω…ΥθΕΧ≤ζΤΖ…œ – ±Φδ≤ΔΫΒΒΆΩΣΖΔ≥…±ΨΓΘ

‘Ύ?PSpice for TI …ηΦΤΚΆΖ¬’φΙΛΨΏ÷–Θ§ΡζΩ…“‘Υ―Υς TI (...)

TINA-TI ΓΣ Μυ”Ύ SPICE ΒΡΡΘΡβΖ¬’φ≥Χ–ρ

TINA-TI ΧαΙ©ΝΥ SPICE Υυ”–ΒΡ¥ΪΆ≥÷±ΝςΓΔΥ≤Χ§ΚΆΤΒ”ρΖ÷Έω“‘ΦΑΗϋΕύΓΘTINA ΨΏ”–ΙψΖΚΒΡΚσ¥ΠάμΙΠΡήΘ§‘ –μΡζΑ¥’’œΘΆϊΒΡΖΫ Ϋ…η÷ΟΫαΙϊΒΡΗώ ΫΓΘ–ιΡβ“«Τς‘ –μΡζ―Γ‘ώ δ»κ≤®–ΈΓΔΧΫ’κΒγ¬ΖΫΎΒψΒγ―ΙΚΆ≤®–ΈΓΘTINA ΒΡ‘≠άμΆΦ≤ΕΜώΖ«≥Θ÷±Ιέ - ’φ’ΐΒΡΓΑΩλΥΌ»κΟ≈Γ±ΓΘTINA-TI Α≤ΉΑ–η“Σ¥σ‘Φ 500MBΓΘ÷±Ϋ”Α≤ΉΑΘ§»γΙϊœκ–Ε‘Ί“≤Κή»ί“ΉΓΘΈ“Ο«œύ–≈ΡζΩœΕ®ΜαΑ°≤Μ Ά ÷ΓΘ

TINA «Β¬÷ί“«Τς (TI) Ή®”–ΒΡ DesignSoft ≤ζΤΖΓΘΗΟΟβΖ―Αφ±ΨΨΏ”–Άξ’ϊΒΡΙΠΡήΘ§ΒΪ≤Μ÷ß≥÷Άξ’ϊΑφ TINA ΥυΧαΙ©ΒΡΡ≥–©ΤδΥϊΙΠΡήΓΘ

»γ–ηΜώ»ΓΩ…”Ο TINA-TI ΡΘ–ΆΒΡΆξ’ϊΝ–±μΘ§«κ≤Έ‘ΡΘΚSpiceRack - Άξ’ϊΝ–±μ

–η“Σ HSpice (...)