摘要

南皇电子专注于整合中国优质电子TI代理商国内领先的现货资源,提供合理的行业价格、战略备货、快速交付控制TI芯片供应商,轻松满足您的需求TI芯片采购需求.(http://www.litesemi.com/)

在C6000 DSP的TI中文官网优化是开发过程中必不可少的环节,可分为系统、算法、代码和内存优化。通常,开发者熟悉自己的代码,会从前三个方面进行修改,以提高整体性能,但对于内存,特别是缓存(Cache)由于它涉及芯片本身的架构,Cache的维护由DSP考虑到这些实际问题,从TI7.0系列编译器开始支持缓存优化工具的使用(Cache Layout Tools)对C通过这一系列工具,可以轻松优化6000代码。L1P Cache本文详细介绍了该工具的使用方法。

1.引言

目前,使用TI DSP越来越多的用户,在C6000系列DSP中,包含了C64x, C64x , C66x等。在C6000 DSP在开发过程中,为了充分利用DSP计算资源需要优化用户程序,可分为系统、算法、代码和内存优化。通常,开发者熟悉自己的系统和代码,可以更方便地从前三个方面进行修改,以提高整体性能,但对于内存,特别是缓存(Cache)由于它涉及芯片本身的架构,Cache的维护由DSP考虑到这些实际问题,从TI 的7.0 一系列编译器开始支持缓存优化工具的使用(Cache Layout Tools)对C通过这一系列工具,可以轻松优化6000代码。L1P Cache本文详细介绍了该工具的使用方法。

2.C6000 DSP内核缓存机制

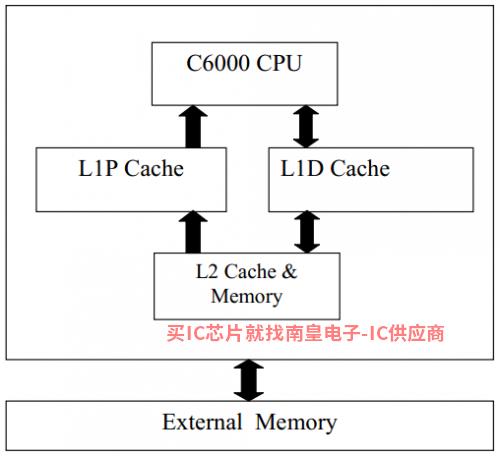

C如下图所示。

Figure 1.C6000存储器结构

存储器分为三级:一级L包括数据存储器(L1D)和代码存储器(L1P);二是代码和数据共用存储器(L2以及MSMC SRAM);第三级是外部存储器,主要是DDR存储器。L1P、L1D和L2的Cache相应的功能L1P 控制器、L1D控制器和L完成控制器。

在C6000 DSP我们通常把它放在中间L1P全部配置成Cache,当CPU发出出取指命令开始L1P如果在里面搜索L1P找不到,到下一级Cache或者Memory在里面搜索,找到需要的地址,读入L1P里,CPU从中读取执行。

因为L1P Cache大小有限(本文为32KB例如,用户内存空间一般大于32KB,所有地址都必须通过映射来实现L1P缓存;在C6000 DSP中,L1P Cache使用地址直接映射,所有DSP 核可访问地址正确L1P Cache大小(32K)取模可获得该地址L1P Cache的偏移值。

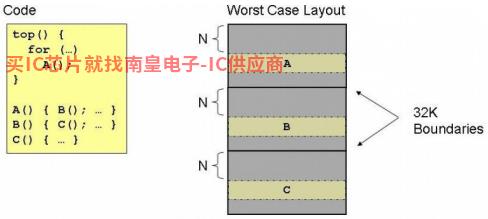

如果用户代码在内存中的不合理,可能会出现L1P Cache重复的内容替换,下图中的例子是极端情况。

Figure 2. 函数布局不正确

TOP函数中FOR反复调用循环A 函数,而A,B,C三个函数分布在内存地址和32上KB因此,边界的偏移地址是一样的,A,B,C将对应L1P里同一个CACHE位置如下

执行A时,CPUA函数需要调入Cache偏移值N的位置;

A调用B,此时转入B到Cache偏移值N 覆盖A代码的位置;

B调用C,此时转入C到Cache偏移值N 覆盖B代码的位置;

C返回,下一个循环转移到A到CacheC代码中覆盖。

DSP核对L1P,L2,DDR访问速度差异很大,对L1P访问通常是1 个时钟周期内完成,而L平均需要3-5个周期,DDR访问需要更多的时间,所以我们应该尽量避免上述重复Cache在尽可能减少函数的情况下Cache中的置换。

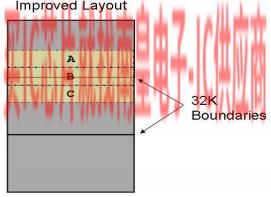

如何解决这个问题?最好的解决办法是A,B,C连续排放在内存中,以便对Cache操作次数最小化,可有效提高执行效率,如下图所示,只要A,B,C总尺寸不超过32KB,它们在Cache偏移值是连续的,即使总和大于32KB,只有超过32个被替换了K的部分。

Figure 3. 正确排列函数

3.内存优化工具

从以上机制可以看出,对L1P Cache优化主要通过分析函数调用关系及其内存分布。人工分析代码调用关系和地址布局需要很多时间,因为用户代码越来越复杂。因此,从7.0系列编译工具开始,TI提供一套内存优化工具(Cache Layout Tools)帮助用户轻松快捷地解决这个问题。

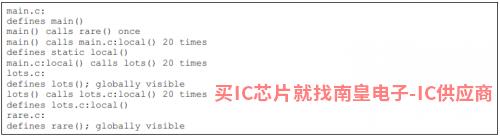

该工具的原理是在用户编译程序时打开生成分析信息选项,编译器将自动向用户程序添加分析记录代码,然后用户在TI DSP simulator或者DSP可执行文件在芯片上运行,内置的分析代码会自动记录用户的函数调用关系和调用次数。操作案例越多,记录的信息越详细,优化效果越好。

在获得函数运行信息后,可以使用编译工具进行分析,生成函数排列顺序,最后输入编译器重新编译原始代码,生成的可执行文件优化了内存排列,具体操作可参考以下实例。

4.实例教程

该实例主要由三个C文件组成,

实例中使用DSP计数器TSCL来统计cycle数,子函数sub目录下。

使用实例的步骤如下,

1.编译代码

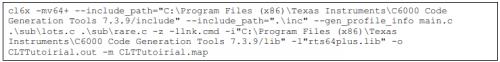

使用TI编译器编译这个例子是为了生成它profile编译时需要增加的信息--gen_profile_info选项。如果使用命令返还的形式,命令在下行运行Compile.bat文件,cl6x具体参数可参考spru186和spru一般可以在编译器的安装目录下找到两个文档,如C:\Program Files(x86)\Texas Instruments\C6000 Code Generation Tools 7.3.9\doc。

同时在目录下生成OBJ和ASM文件,这和我们的实验关系不大,不用注意。out文件是可执行的文件,需要在芯片中下载一段时间,map帮助我们定位文件profile存储信息的内存地址。

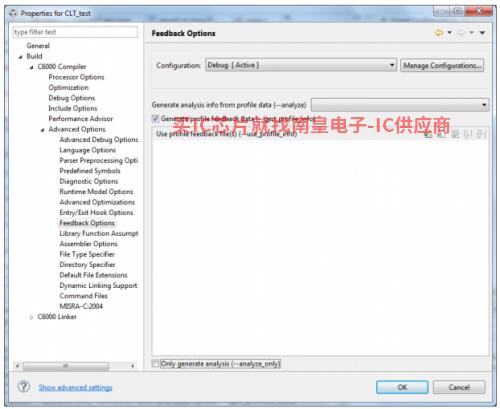

若用户使用CCS需要编译工具Build指定属性Feedback携带分析代码的可执行文件可以正常编译。

Figure 4. CCS初步编译的选项

- 电源管理IC - 稳压器 - 线性

- 电源管理IC - 稳压器 - DC DC 开关稳压器

- 逻辑 - 触发器

- 评估板 - DC-DC 与 AC-DC(离线)SMPS

- 线性器件 - 放大器 - 仪器、运算放大器、缓冲放大器

- 直流转换器

- 嵌入式 - 微控制器

- 电源管理IC - 稳压器 - DC DC 开关式控制器

- 电源管理IC - 电压基准

- 评估板 - DC-DC 与 AC-DC(离线)SMPS

- 线性 - 放大器 - 音频

- 逻辑 - 触发器