- 制造厂商:TI

- 产品类别:微控制器 (MCU) 和处理器

- 技术类目:处理器 - 数字信号处理器 (DSP)

- 功能描述:C67x 浮点 DSP- 高达 300MHz、McBSP、16 位 EMIFA

- 点击这里打开及下载TMS320C6713B的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

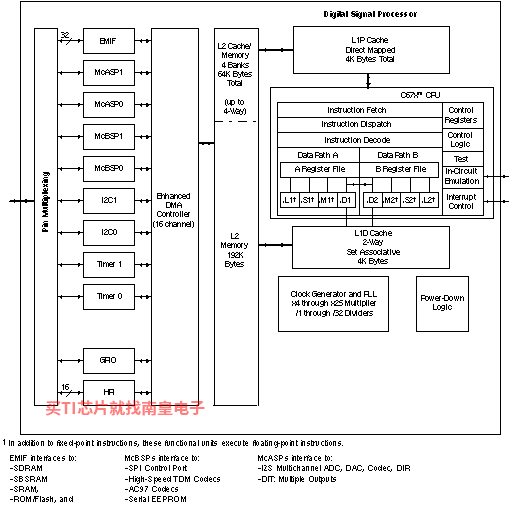

The TMS320C67x™ DSPs (including the TMS320C6713B device ) compose the floating-point DSP generation in the TMS320C6000™ DSP platform. The C6713B device is based on the high-performance, advanced very-long-instruction-word (VLIW) architecture developed by Texas Instruments (TI), making this DSP an excellent choice for multichannel and multifunction applications.

) compose the floating-point DSP generation in the TMS320C6000™ DSP platform. The C6713B device is based on the high-performance, advanced very-long-instruction-word (VLIW) architecture developed by Texas Instruments (TI), making this DSP an excellent choice for multichannel and multifunction applications.

Operating at 225 MHz, the C6713B delivers up to 1350 million floating-point operations per second (MFLOPS), 1800 million instructions per second (MIPS), and with dual fixed-/floating-point multipliers up to 450 million multiply-accumulate operations per second (MMACS).

Operating at 300 MHz, the C6713B delivers up to 1800 million floating-point operations per second (MFLOPS), 2400 million instructions per second (MIPS), and with dual fixed-/floating-point multipliers up to 600 million multiply-accumulate operations per second (MMACS).

The C6713B uses a two-level cache-based architecture and has a powerful and diverse set of peripherals. The Level 1 program cache (L1P) is a 4K-byte direct-mapped cache and the Level 1 data cache (L1D) is a 4K-byte 2-way set-associative cache. The Level 2 memory/cache (L2) consists of a 256K-byte memory space that is shared between program and data space. 64K bytes of the 256K bytes in L2 memory can be configured as mapped memory, cache, or combinations of the two. The remaining 192K bytes in L2 serves as mapped SRAM.

The C6713B has a rich peripheral set that includes two Multichannel Audio Serial Ports (McASPs), two Multichannel Buffered Serial Ports (McBSPs), two Inter-Integrated Circuit (I2C) buses, one dedicated General-Purpose Input/Output (GPIO) module, two general-purpose timers, a host-port interface (HPI), and a glueless external memory interface (EMIF) capable of interfacing to SDRAM, SBSRAM, and asynchronous peripherals.

The two McASP interface modules each support one transmit and one receive clock zone. Each of the McASP has eight serial data pins which can be individually allocated to any of the two zones. The serial port supports time-division multiplexing on each pin from 2 to 32 time slots. The C6713B has sufficient bandwidth to support all 16 serial data pins transmitting a 192 kHz stereo signal. Serial data in each zone may be transmitted and received on multiple serial data pins simultaneously and formatted in a multitude of variations on the Philips Inter-IC Sound (I2S) format.

In addition, the McASP transmitter may be programmed to output multiple S/PDIF, IEC60958, AES-3, CP-430 encoded data channels simultaneously, with a single RAM containing the full implementation of user data and channel status fields.

The McASP also provides extensive error-checking and recovery features, such as the bad clock detection circuit for each high-frequency master clock which verifies that the master clock is within a programmed frequency range.

The two I2C ports on the TMS320C6713B allow the DSP to easily control peripheral devices and communicate with a host processor. In addition, the standard multichannel buffered serial port (McBSP) may be used to communicate with serial peripheral interface (SPI) mode peripheral devices.

The TMS320C6713B device has two bootmodes: from the HPI or from external asynchronous ROM. For more detailed information, see the bootmode section of this data sheet.

The TMS320C67x DSP generation is supported by the TI eXpressDSP™ set of industry benchmark development tools, including a highly optimizing C/C++ Compiler, the Code Composer Studio™ Integrated Development Environment (IDE), JTAG-based emulation and real-time debugging, and the DSP/BIOS™ kernel.

- Highest-Performance Floating-Point Digital Signal Processor (DSP): TMS320C6713B

- Eight 32-Bit Instructions/Cycle

- 32/64-Bit Data Word

- 300-, 225-, 200-MHz (GDP and ZDP), and 225-, 200-, 167-MHz (PYP) Clock Rates

- 3.3-, 4.4-, 5-, 6-Instruction Cycle Times

- 2400/1800, 1800/1350, 1600/1200, and 1336/1000 MIPS/MFLOPS

- Rich Peripheral Set, Optimized for Audio

- Highly Optimized C/C++ Compiler

- Extended Temperature Devices Available

- Advanced Very Long Instruction Word (VLIW) TMS320C67x? DSP Core

- Eight Independent Functional Units:

- 2 ALUs (Fixed-Point)

- 4 ALUs (Floating-/Fixed-Point)

- 2 Multipliers (Floating-/Fixed-Point)

- Load-Store Architecture With 32 32-Bit General-Purpose Registers

- Instruction Packing Reduces Code Size

- All Instructions Conditional

- Eight Independent Functional Units:

- Instruction Set Features

- Native Instructions for IEEE 754

- Single- and Double-Precision

- Byte-Addressable (8-, 16-, 32-Bit Data)

- 8-Bit Overflow Protection

- Saturation; Bit-Field Extract, Set, Clear; Bit-Counting; Normalization

- Native Instructions for IEEE 754

- L1/L2 Memory Architecture

- 4K-Byte L1P Program Cache (Direct-Mapped)

- 4K-Byte L1D Data Cache (2-Way)

- 256K-Byte L2 Memory Total: 64K-Byte L2 Unified Cache/Mapped RAM, and 192K-Byte Additional L2 Mapped RAM

- Device Configuration

- Boot Mode: HPI, 8-, 16-, 32-Bit ROM Boot

- Endianness: Little Endian, Big Endian

- 32-Bit External Memory Interface (EMIF)

- Glueless Interface to SRAM, EPROM, Flash, SBSRAM, and SDRAM

- 512M-Byte Total Addressable External Memory Space

- Enhanced Direct-Memory-Access (EDMA) Controller (16 Independent Channels)

- 16-Bit Host-Port Interface (HPI)

- Two McASPs

- Two Independent Clock Zones Each (1 TX and 1 RX)

- Eight Serial Data Pins Per Port: Individually Assignable to any of the Clock Zones

- Each Clock Zone Includes:

- Programmable Clock Generator

- Programmable Frame Sync Generator

- TDM Streams From 2-32 Time Slots

- Support for Slot Size:

- 8, 12, 16, 20, 24, 28, 32 Bits

- Data Formatter for Bit Manipulation

- Wide Variety of I2S and Similar Bit Stream Formats

- Integrated Digital Audio Interface Transmitter (DIT) Supports:

- S/PDIF, IEC60958-1, AES-3, CP-430 Formats

- Up to 16 transmit pins

- Enhanced Channel Status/User Data

- Extensive Error Checking and Recovery

- Two Inter-Integrated Circuit Bus (I2C Bus?) Multi-Master and Slave Interfaces

- Two Multichannel Buffered Serial Ports:

- Serial-Peripheral-Interface (SPI)

- High-Speed TDM Interface

- AC97 Interface

- Two 32-Bit General-Purpose Timers

- Dedicated GPIO Module With 16 pins (External Interrupt Capable)

- Flexible Phase-Locked-Loop (PLL) Based Clock Generator Module

- IEEE-1149.1 (JTAG) Boundary-Scan-Compatible

- 208-Pin PowerPAD? PQFP (PYP)

- 272-BGA Packages (GDP and ZDP)

- 0.13-μm/6-Level Copper Metal Process

- CMOS Technology

- 3.3-V I/Os, 1.2-V Internal (GDP/ZDP/ PYP)

- 3.3-V I/Os, 1.4-V Internal (GDP/ZDP) [300 MHz]

TMS320C67x and PowerPAD are trademarks of Texas Instruments. I2C Bus is a trademark of Philips Electronics N.V. Corporation All trademarks are the property of their respective owners. IEEE Standard 1149.1-1990 Standard-Test-Access Port and Boundary Scan Architecture. These values are compatible with existing 1.26-V designs. TMS320C6000, eXpressDSP, Code Composer Studio, and DSP/BIOS are trademarks of Texas Instruments. Throughout the remainder of this document, TMS320C6713B shall be referred to as C6713B or 13B.

- DSP

- 1 C67x

- DSP MHz (Max)

- 167, 200, 200, 225, 300

- CPU

- 32-/64-bit

- Operating system

- DSP/BIOS

- Rating

- Catalog

- Operating temperature range (C)

- -40 to 105, 0 to 90

TMS320C6713B的完整型号有:TMS320C6713BGDP225、TMS320C6713BGDP300、TMS320C6713BPYP200、TMS320C6713BZDP225、TMS320C6713BZDP300、TMS32C6713BGDPA200、TMS32C6713BPYPA167、TMS32C6713BPYPA200、TMS32C6713BZDPA200,以下是这些产品的关键参数及官网采购报价:

TMS320C6713BGDP225,工作温度:0 to 90,封装:BGA (GDP)-272,包装数量MPQ:40个,MSL 等级/回流焊峰值温度:Level-3-220C-168 HR,引脚镀层/焊球材料:SNPB,TI官网TMS320C6713BGDP225的批量USD价格:22.141(1000+)

TMS320C6713BGDP300,工作温度:0 to 90,封装:BGA (GDP)-272,包装数量MPQ:40个,MSL 等级/回流焊峰值温度:Level-3-220C-168 HR,引脚镀层/焊球材料:SNPB,TI官网TMS320C6713BGDP300的批量USD价格:29.327(1000+)

TMS320C6713BPYP200,工作温度:0 to 90,封装: (PYP)-208,包装数量MPQ:36个,MSL 等级/回流焊峰值温度:Level-4-260C-72 HR,引脚镀层/焊球材料:NIPDAU,TI官网TMS320C6713BPYP200的批量USD价格:16.897(1000+)

TMS320C6713BZDP225,工作温度:0 to 90,封装:BGA (ZDP)-272,包装数量MPQ:40个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:SNAGCU,TI官网TMS320C6713BZDP225的批量USD价格:22.141(1000+)

TMS320C6713BZDP300,工作温度:0 to 90,封装:BGA (ZDP)-272,包装数量MPQ:40个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:SNAGCU,TI官网TMS320C6713BZDP300的批量USD价格:29.327(1000+)

TMS32C6713BGDPA200,工作温度:-40 to 105,封装:BGA (GDP)-272,包装数量MPQ:40个,MSL 等级/回流焊峰值温度:Level-3-220C-168 HR,引脚镀层/焊球材料:SNPB,TI官网TMS32C6713BGDPA200的批量USD价格:22.53(1000+)

TMS32C6713BPYPA167,工作温度:-40 to 105,封装: (PYP)-208,包装数量MPQ:36个,MSL 等级/回流焊峰值温度:Level-4-260C-72 HR,引脚镀层/焊球材料:NIPDAU,TI官网TMS32C6713BPYPA167的批量USD价格:20.976(1000+)

TMS32C6713BPYPA200,工作温度:-40 to 105,封装: (PYP)-208,包装数量MPQ:36个,MSL 等级/回流焊峰值温度:Level-4-260C-72 HR,引脚镀层/焊球材料:NIPDAU,TI官网TMS32C6713BPYPA200的批量USD价格:20.005(1000+)

TMS32C6713BZDPA200,工作温度:-40 to 105,封装:BGA (ZDP)-272,包装数量MPQ:40个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:SNAGCU,TI官网TMS32C6713BZDPA200的批量USD价格:22.53(1000+)

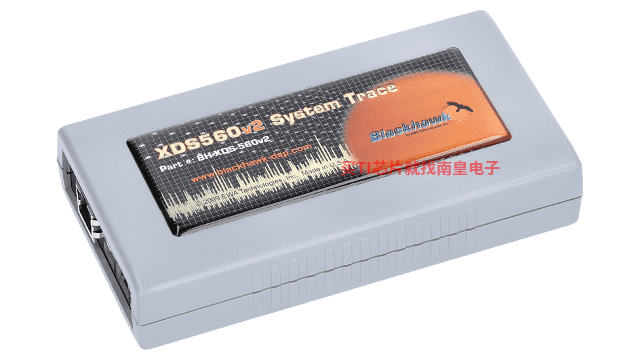

TMDSEMU560V2STM-U ― Blackhawk XDS560v2 系统跟踪 USB 仿真器

XDS560v2 System Trace 是 XDS560v2 系列高性能 TI 处理器调试探针(仿真器)的第一种型号。XDS560v2 是 XDS 系列调试探针中性能最高的一款,同时支持传统 JTAG 标准 (IEEE1149.1) 和 cJTAG (IEEE1149.7)。

XDS560v2 System Trace 在其巨大的外部存储器缓冲区中加入了系统引脚跟踪。这种外部存储器缓冲区适用于指定的 TI 器件,通过捕获相关器件级信息,获得准确的总线性能活动和吞吐量,并对内核和外设进行电源管理。此外,对于带有嵌入式缓冲跟踪器 (ETB) 的所有 ARM 和 DSP 处理器,所有 XDS (...)

TMDSEMU560V2STM-UE ― Spectrum Digital XDS560v2 系统跟踪 USB 和以太网

XDS560v2 System Trace 是 XDS560v2 系列高性能 TI 处理器调试探针(仿真器)的第一种型号。XDS560v2 是 XDS 系列调试探针中性能最高的一款,同时支持传统 JTAG 标准 (IEEE1149.1) 和 cJTAG (IEEE1149.7)。

XDS560v2 System Trace 在其巨大的外部存储器缓冲区中加入了系统引脚跟踪。这种外部存储器缓冲区适用于指定的 TI 器件,通过捕获相关器件级信息,获得准确的总线性能活动和吞吐量,并对内核和外设进行电源管理。此外,对于带有嵌入式缓冲跟踪器 (ETB) 的所有 ARM 和 DSP 处理器,所有 XDS (...)

CCSTUDIO — Code Composer Studio 集成式开发环境 (IDE)

德州仪器 (TI) 数学库是优化的浮点数学函数库,用于使用 TI 浮点器件的 C 编程器。这些例程通常用于计算密集型实时应用,最佳执行速度是这些应用的关键。通过使用这些例程(而不是在现有运行时支持中找到的例程),您可以在无需重写现有代码的情况下获得更快的执行速度。MATHLIB 库包括目前在现有实时支持库中提供的所有浮点数学例程。这些新函数可称为当前实时支持库名称或包含在数学库中的新名称。SPRC265 ― TMS320C6000 DSP 库 (DSPLIB)

TMS320C6000 Digital Signal Processor Library (DSPLIB) is a platform-optimized DSP function library for C programmers. It includes C-callable, general-purpose signal-processing routines that are typically used in computationally intensive real-time applications. With these routines, higher (...)C6713B GDP IBIS Model (Rev. B)

TI has partnered with companies to offer a wide range of software, tools, and SOMs using TI processors to accelerate your path to production. Download this search tool to quickly browse our third-party solutions and find the right third-party to meet your needs. The software, tools and modules (...)