- 制造厂商:TI

- 产品类别:微控制器 (MCU) 和处理器

- 技术类目:处理器 - 数字信号处理器 (DSP)

- 功能描述:C67x 浮点 DSP- 高达 250MHz、McASP、32 位 EMIFA

- 点击这里打开及下载TMS320C6727的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

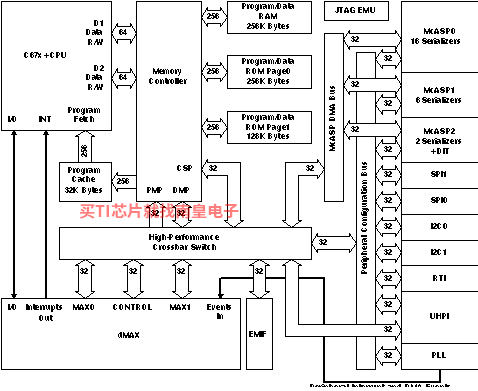

The TMS320C672x is the next generation of Texas Instruments’ C67x™ family of high-performance 32-/64-bit floating-point digital signal processors. The TMS320C672x includes the TMS320C6727, TMS320C6726, and TMS320C6722 devices.(1)

Enhanced C67x+ CPU. The C67x+ CPU is an enhanced version of the C67x CPU used on the C671x DSPs. It is compatible with the C67x CPU but offers significant improvements in speed, code density, and floating-point performance per clock cycle. At 300 MHz, the CPU is capable of a maximum performance of 2400 MIPS/1800 MFLOPS by executing up to eight instructions (six of which are floating-point instructions) in parallel each cycle. The CPU natively supports 32-bit fixed-point, 32-bit single-precision floating-point, and 64-bit double-precision floating-point arithmetic.

Efficient Memory System. The memory controller maps the large on-chip 256K-byte RAM and 384K-byte ROM as unified program/data memory. Development is simplified since there is no fixed division between program and data memory size as on some other devices.

The memory controller supports single-cycle data accesses from the C67x+ CPU to the RAM and ROM. Up to three parallel accesses to the internal RAM and ROM from three of the following four sources are supported:

- Two 64-bit data accesses from the C67x+ CPU

- One 256-bit program fetch from the core and program cache

- One 32-bit data access from the peripheral system (either dMAX or UHPI)

The large (32K-byte) program cache translates to a high hit rate for most applications. This prevents most program/data access conflicts to the on-chip memory. It also enables effective program execution from an off-chip memory such as an SDRAM.

High-Performance Crossbar Switch. A high-performance crossbar switch acts as a central hub between the different bus masters (CPU, dMAX, UHPI) and different targets (peripherals and memory). The crossbar is partially connected; some connections are not supported (for example, UHPI-to-peripheral connections).

Multiple transfers occur in parallel through the crossbar as long as there is no conflict between bus masters for a particular target. When a conflict does occur, the arbitration is a simple and deterministic fixed-priority scheme.

The dMAX is given highest-priority since it is responsible for the most time-critical I/O transfers, followed next by the UHPI, and finally by the CPU.

dMAX Dual Data Movement Accelerator. The dMAX is a module designed to perform Data Movement Acceleration. The Data Movement Accelerator (dMAX) controller handles user-programmed data transfers between the internal data memory controller and the device peripherals on the C672x DSPs. The dMAX allows movement of data to/from any addressable memory space including internal memory, peripherals, and external memory.

The dMAX controller includes features such as the capability to perform three-dimensional data transfers for advanced data sorting, and the capability to manage a section of the memory as a circular buffer/FIFO with delay-tap based reading and writing of data. The dMAX controller is capable of concurrently processing two transfer requests (provided that they are to/from different source/destinations).

External Memory Interface (EMIF) for Flexibility and Expansion. The external memory interface on the C672x supports a single bank of SDRAM and a single bank of asynchronous memory. The EMIF data width is 16 bits wide on the C6726 and C6722, and 32 bits wide on the C6727.

SDRAM support includes x16 and x32 SDRAM devices with 1, 2, or 4 banks.

The C6726 and C6722 support SDRAM devices up to 128M bits.

The C6727 extends SDRAM support to 256M-bit and 512M-bit devices.

Asynchronous memory support is typically used to boot from a parallel non-multiplexed NOR flash device that can be 8, 16, or 32 bits wide. Booting from larger flash devices than are natively supported by the dedicated EMIF address lines is accomplished by using general-purpose I/O pins for upper address lines.

The asynchronous memory interface can also be configured to support 8- or 16-bit-wide NAND flash. It includes a hardware ECC calculation (for single-bit errors) that can operate on blocks of data up to 512 bytes.

Universal Host-Port Interface (UHPI) for High-Speed Parallel I/O. The Universal Host-Port Interface (UHPI) is a parallel interface through which an external host CPU can access memories on the DSP. Three modes are supported by the C672x UHPI:

- Multiplexed Address/Data - Half-Word (16-bit-wide) Mode (similar to C6713)

- Multiplexed Address/Data - Full Word (32-bit-wide) Mode

- Non-Multiplexed Mode - 16-bit Address and 32-bit Data Bus

The UHPI can also be restricted to accessing a single page (64K bytes) of memory anywhere in the address space of the C672x; this page can be changed, but only by the C672x CPU. This feature allows the UHPI to be used for high-speed data transfers even in systems where security is an important requirement.

The UHPI is only available on the C6727.

Multichannel Audio Serial Ports (McASP0, McASP1, and McASP2) - Up to 16 Stereo Channels I2S. The multichannel audio serial port (McASP) seamlessly interfaces to CODECs, DACs, ADCs, and other devices. It supports the ubiquitous IIS format as well as many variations of this format, including time division multiplex (TDM) formats with up to 32 time slots.

Each McASP includes a transmit and receive section which may operate independently or synchronously; furthermore, each section includes its own flexible clock generator and extensive error-checking logic.

As data passes through the McASP, it can be realigned so that the fixed-point representation used by the application code can be independent of the representation used by the external devices without requiring any CPU overhead to make the conversion.

The McASP is a configurable module and supports between 2 and 16 serial data pins. It also has the option of supporting a Digital Interface Transmitter (DIT) mode with a full 384 bits of channel status and user data memory.

McASP2 is not available on the C6722.

Inter-Integrated Circuit Serial Ports (I2C0, I2C1). The C672x includes two inter-integrated circuit (I2C) serial ports. A typical application is to configure one I2C serial port as a slave to an external user-interface microcontroller. The other I2C serial port may then be used by the C672x DSP to control external peripheral devices, such as a CODEC or network controller, which are functionally peripherals of the DSP device.

The two I2C serial ports are pin-multiplexed with the SPI0 serial port.

Serial Peripheral Interface Ports (SPI0, SPI1). As in the case of the I2C serial ports, the C672x DSP also includes two serial peripheral interface (SPI) serial ports. This allows one SPI port to be configured as a slave to control the DSP while the other SPI serial port is used by the DSP to control external peripherals.

The SPI ports support a basic 3-pin mode as well as optional 4- and 5-pin modes. The optional pins include a slave chip-select pin and an enable pin which implements handshaking automatically in hardware for maximum SPI throughput.

The SPI0 port is pin-multiplexed with the two I2C serial ports (I2C0 and I2C1). The SPI1 serial port is pin-multiplexed with five of the serial data pins from McASP0 and McASP1.

Real-Time Interrupt Timer (RTI). The real-time interrupt timer module includes:

- Two 32-bit counter/prescaler pairs

- Two input captures (tied to McASP direct memory access [DMA] events for sample rate measurement)

- Four compares with automatic update capability

- Digital Watchdog (optional) for enhanced system robustness

Clock Generation (PLL and OSC). The C672x DSP includes an on-chip oscillator that supports crystals in the range of 12 MHz to 25 MHz. Alternatively, the clock can be provided externally through the CLKIN pin.

The DSP includes a flexible, software-programmable phase-locked loop (PLL) clock generator. Three different clock domains (SYSCLK1, SYSCLK2, and SYSCLK3) are generated by dividing down the PLL output. SYSCLK1 is the clock used by the CPU, memory controller, and memories. SYSCLK2 is used by the peripheral subsystem and dMAX. SYSCLK3 is used exclusively for the EMIF.

- C672x: 32-/64-Bit 300-MHz Floating-Point DSPs

- Upgrades to C67x+ CPU From C67x? DSP Generation:

- 2X CPU Registers [64 General-Purpose]

- New Audio-Specific Instructions

- Compatible With the C67x CPU

- Enhanced Memory System

- 256K-Byte Unified Program/Data RAM

- 384K-Byte Unified Program/Data ROM

- Single-Cycle Data Access From CPU

- Large Program Cache (32K Byte) Supports RAM, ROM, and External Memory

- External Memory Interface (EMIF) Supports

- 100-MHz SDRAM (16- or 32-Bit)

- Asynchronous NOR Flash, SRAM (8-,16-, or 32-Bit)

- NAND Flash (8- or 16-Bit)

- Enhanced I/O System

- High-Performance Crossbar Switch

- Dedicated McASP DMA Bus

- Deterministic I/O Performance

- dMAX (Dual Data Movement Accelerator) Supports:

- 16 Independent Channels

- Concurrent Processing of Two Transfer Requests

- 1-, 2-, and 3-Dimensional Memory-to-Memory and Memory-to-Peripheral Data Transfers

- Circular Addressing Where the Size of a Circular Buffer (FIFO) is not Limited to 2n

- Table-Based Multi-Tap Delay Read and Write Transfers From/To a Circular Buffer

- Three Multichannel Audio Serial Ports

- Transmit/Receive Clocks up to 50 MHz

- Six Clock Zones and 16 Serial Data Pins

- Supports TDM, I2S, and Similar Formats

- DIT-Capable (McASP2)

- Universal Host-Port Interface (UHPI)

- 32-Bit-Wide Data Bus for High Bandwidth

- Muxed and Non-Muxed Address and Data

- Two 10-MHz SPI Ports With 3-, 4-, and 5-Pin Options

- Two Inter-Integrated Circuit (I2C) Ports

- Real-Time Interrupt Counter/Watchdog

- Oscillator- and Software-Controlled PLL

- Applications:

- Professional Audio

- Mixers

- Effects Boxes

- Audio Synthesis

- Instrument/Amp Modeling

- Audio Conferencing

- Audio Broadcast

- Audio Encoder

- Emerging Audio Applications

- Biometrics

- Medical

- Industrial

- Professional Audio

- Commercial or Extended Temperature

- 144-Pin, 0.5-mm, PowerPAD? Thin Quad Flatpack (TQFP) [RFP Suffix]

- 256-Terminal, 1.0-mm, 16x16 Array Plastic Ball Grid Array (PBGA) [GDH and ZDH Suffixes]

C67x, PowerPAD, TMS320C6000, C6000, DSP/BIOS, XDS, TMS320 are trademarks of Texas Instruments. Philips is a registered trademark of Koninklijki Philips Electronics N.V. All trademarks are the property of their respective owners. (1) Throughout the remainder of the document, TMS320C6727 (or C6727), TMS320C6726 (or C6726), and/or TMS320C6722 (or C6722) will be referred to as TMS320C672x (or C672x).

- DSP

- 1 C67x

- DSP MHz (Max)

- 250

- CPU

- 32-/64-bit

- Operating system

- DSP/BIOS

- Rating

- Catalog

- Operating temperature range (C)

- 0 to 90

TMS320C6727的完整型号有:TMS320C6727BZDH250,以下是这些产品的关键参数及官网采购报价:

TMS320C6727BZDH250,工作温度:0 to 90,封装:BGA (ZDH)-256,包装数量MPQ:90个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:SNAGCU,TI官网TMS320C6727BZDH250的批量USD价格:18.691(1000+)

TMDSEMU560V2STM-U ― Blackhawk XDS560v2 系统跟踪 USB 仿真器

XDS560v2 System Trace 是 XDS560v2 系列高性能 TI 处理器调试探针(仿真器)的第一种型号。XDS560v2 是 XDS 系列调试探针中性能最高的一款,同时支持传统 JTAG 标准 (IEEE1149.1) 和 cJTAG (IEEE1149.7)。

XDS560v2 System Trace 在其巨大的外部存储器缓冲区中加入了系统引脚跟踪。这种外部存储器缓冲区适用于指定的 TI 器件,通过捕获相关器件级信息,获得准确的总线性能活动和吞吐量,并对内核和外设进行电源管理。此外,对于带有嵌入式缓冲跟踪器 (ETB) 的所有 ARM 和 DSP 处理器,所有 XDS (...)

TMDSEMU560V2STM-UE ― Spectrum Digital XDS560v2 系统跟踪 USB 和以太网

XDS560v2 System Trace 是 XDS560v2 系列高性能 TI 处理器调试探针(仿真器)的第一种型号。XDS560v2 是 XDS 系列调试探针中性能最高的一款,同时支持传统 JTAG 标准 (IEEE1149.1) 和 cJTAG (IEEE1149.7)。

XDS560v2 System Trace 在其巨大的外部存储器缓冲区中加入了系统引脚跟踪。这种外部存储器缓冲区适用于指定的 TI 器件,通过捕获相关器件级信息,获得准确的总线性能活动和吞吐量,并对内核和外设进行电源管理。此外,对于带有嵌入式缓冲跟踪器 (ETB) 的所有 ARM 和 DSP 处理器,所有 XDS (...)

FAXLIB — 用于 C66x、C64x+ 和 C55x 处理器的传真库 (FAXLIB)

The Chip Support Library (CSL) provides an application programming interface (API) used for configuring and controlling the DSP on-chip peripherals for ease of use and hardware abstraction. This will shorten development time by providing standardization and portability. The functions listed in the (...)SPRC265 ― TMS320C6000 DSP 库 (DSPLIB)

TMS320C6000 Digital Signal Processor Library (DSPLIB) is a platform-optimized DSP function library for C programmers. It includes C-callable, general-purpose signal-processing routines that are typically used in computationally intensive real-time applications. With these routines, higher (...)SPRC203 ― TMS310C672x ROM C9230C100 启动器系统初始化路径

Patch Code, FastRts(V1.20)/DSPLIB (V2.00) ROM Examples & Libraries, and Boot Configuration Utlities + Boot ExamplesSystem Patch V2.00.00 , FastRts(1.20), DSPLIB (V2.00), genBootCfg(1.0030), genAIS(1.03.06)

C6727 GDH BSDL Model (Rev. B)

TI has partnered with companies to offer a wide range of software, tools, and SOMs using TI processors to accelerate your path to production. Download this search tool to quickly browse our third-party solutions and find the right third-party to meet your needs. The software, tools and modules (...)