- 制造厂商:TI

- 产品类别:微控制器 (MCU) 和处理器

- 技术类目:处理器 - 数字信号处理器 (DSP)

- 功能描述:定点数字信号处理器

- 点击这里打开及下载TMS320VC5502的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

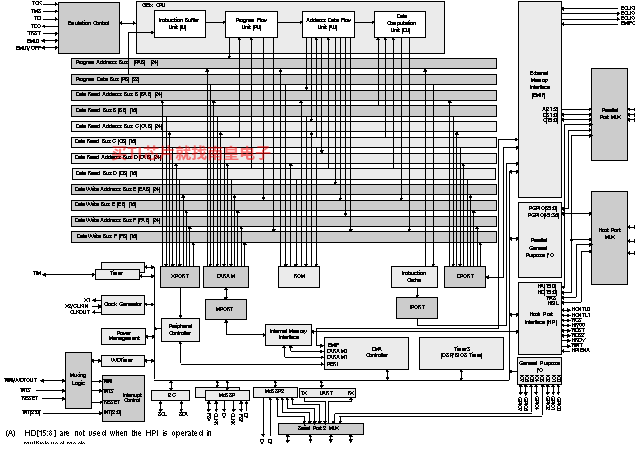

The TMS320VC5502 (5502) fixed-point digital signal processor (DSP) is based on the TMS320C55x™ DSP generation CPU processor core. The C55x™ DSP architecture achieves high performance and low power through increased parallelism and total focus on reduction in power dissipation. The CPU supports an internal bus structure that is composed of one program bus, three data read buses, two data write buses, and additional buses dedicated to peripheral and DMA activity. These buses provide the ability to perform up to three data reads and two data writes in a single cycle. In parallel, the DMA controller can perform data transfers independent of the CPU activity.

The C55x™ CPU provides two multiply-accumulate (MAC) units, each capable of 17-bit × 17-bit multiplication in a single cycle. A central 40-bit arithmetic/logic unit (ALU) is supported by an additional 16-bit ALU. Use of the ALUs is under instruction set control, providing the ability to optimize parallel activity and power consumption. These resources are managed in the Address Unit (AU) and Data Unit (DU) of the C55x CPU.

The C55x DSP generation supports a variable byte width instruction set for improved code density. The Instruction Unit (IU) performs 32-bit program fetches from internal or external memory and queues instructions for the Program Unit (PU). The Program Unit decodes the instructions, directs tasks to AU and DU resources, and manages the fully protected pipeline. Predictive branching capability avoids pipeline flushes on execution of conditional instructions.

The 5502 peripheral set includes an external memory interface (EMIF) that provides glueless access to asynchronous memories like EPROM and SRAM, as well as to high-speed, high-density memories such as synchronous DRAM and synchronous burst RAM. Additional peripherals include UART, watchdog timer, and an I-Cache. Three full-duplex multichannel buffered serial ports (McBSPs) provide glueless interface to a variety of industry-standard serial devices, and multichannel communication with up to 128 separately enabled channels. The host-port interface (HPI) is a 8-/16-bit parallel interface used to provide host processor access to 32K words of internal memory on the 5502. The HPI can be configured in either multiplexed or non-multiplexed mode to provide glueless interface to a wide variety of host processors. The DMA controller provides data movement for six independent channel contexts without CPU intervention. Two general-purpose timers, eight dedicated general-purpose I/O (GPIO) pins, and analog phase-locked loop (APLL) clock generation are also included.

The 5502 is supported by the industry's award-winning eXpress DSP™, Code Composer Studio™ Integrated Development Environment (IDE), DSP/BIOS™, Texas Instruments. algorithm standard, and the industry's largest third-party network. The Code Composer Studio™ IDE features code generation tools that include a C Compiler, Visual Linker, simulator, RTDX™, XDS510™ emulation device drivers, and evaluation modules. The 5502 is also supported by the C55x™ DSP Library, which features more than 50 foundational software kernels (FIR filters, IIR filters, FFTs, and various math functions) as well as chip and board support libraries.

- High-Performance, Low-Power, Fixed-Point TMS320C55x Digital Signal Processor (DSP)

- 3.33-/5-ns Instruction Cycle Time

- 300-/200-MHz Clock Rate

- 16K-Byte Instruction Cache (I-Cache)

- One/Two Instructions Executed per Cycle

- Dual Multipliers [Up to 600 Million Multiply-Accumulates Per Second (MMACS)]

- Two Arithmetic/Logic Units (ALUs)

- One Program Bus, Three Internal Data/Operand Read Buses, and Two Internal Data/Operand Write Buses

- Instruction Cache (16K Bytes)

- 32K x 16-Bit On-Chip RAM That is Composed of Eight Blocks of 4K × 16-Bit Dual-Access RAM (DARAM) (64K Bytes)

- 16K × 16-Bit One-Wait-State On-Chip ROM (32K Bytes)

- 8M × 16-Bit Maximum Addressable External Memory Space

- 32-Bit External Parallel Bus Memory Supporting External Memory Interface (EMIF) With General-Purpose Input/Output (GPIO) Capabilities and Glueless Interface to:

- Asynchronous Static RAM (SRAM)

- Asynchronous EPROM

- Synchronous DRAM (SDRAM)

- Synchronous Burst RAM (SBRAM)

- Emulation/Debug Trace Capability Saves Last 16 Program Counter (PC) Discontinuities and Last 32 PC Values

- Programmable Low-Power Control of Six Device Functional Domains

- On-Chip Peripherals

- Six-Channel Direct Memory Access (DMA) Controller

- Three Multichannel Buffered Serial Ports (McBSPs)

- Programmable Analog Phase-Locked Loop (APLL) Clock Generator

- General-Purpose I/O (GPIO) Pins and a Dedicated Output Pin (XF)

- 8-Bit/16-Bit Parallel Host-Port Interface (HPI)

- Four Timers

- Two 64-Bit General-Purpose Timers

- 64-Bit Programmable Watchdog Timer

- 64-Bit DSP/BIOS Counter

- Inter-Integrated Circuit (I2C) Interface

- Universal Asynchronous Receiver/Transmitter (UART)

- On-Chip Scan-Based Emulation Logic

- IEEE Std 1149.1(1) (JTAG) Boundary Scan Logic

- Packages:

- 176-Terminal LQFP (Low-Profile Quad Flatpack) (PGF Suffix)

- 201-Terminal MicroStar BGA (Ball Grid Array) (GZZ and ZZZ Suffixes)

- 3.3-V I/O Supply Voltage

- 1.26-V Core Supply Voltage

(1)IEEE Standard 1149.1-1990 Standard-Test-Access Port and Boundary Scan Architecture. NOTE: This document is designed to be used in conjunction with the TMS320C55x DSP CPU Reference Guide (literature number SPRU371). TMS320C55x, DSP/BIOS, MicroStar BGA, C55x, eXpressDSP, Code Composer Studio, RTDX, XDS510, TMS320C54x, C54x, TMS320, TMS320C5000 are trademarks of Texas Instruments. I2C bus is a trademark of Koninklijke Philips Electronics N.V. All trademarks are the property of their respective owners.

- DSP

- 1 C55x

- DSP MHz (Max)

- 200, 300

- CPU

- 16-bit

- Operating system

- DSP/BIOS, VLX

- Rating

- Catalog

- Operating temperature range (C)

- -40 to 85

TMS320VC5502的完整型号有:TMS320C5502ZAVR300、TMS320VC5502GBE200、TMS320VC5502GBE300、TMS320VC5502PGF200、TMS320VC5502PGF300、TMS320VC5502ZAV200、TMS320VC5502ZAV300,以下是这些产品的关键参数及官网采购报价:

TMS320C5502ZAVR300,工作温度:-40 to 85,封装:NFBGA (ZAV)-201,包装数量MPQ:1000个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:SNAGCU,TI官网TMS320C5502ZAVR300的批量USD价格:8.203(1000+)

TMS320VC5502GBE200,工作温度:-40 to 85,封装:NFBGA (GBE)-201,包装数量MPQ:126个,MSL 等级/回流焊峰值温度:Level-3-220C-168 HR,引脚镀层/焊球材料:SNPB,TI官网TMS320VC5502GBE200的批量USD价格:6.657(1000+)

TMS320VC5502GBE300,工作温度:-40 to 85,封装:NFBGA (GBE)-201,包装数量MPQ:126个,MSL 等级/回流焊峰值温度:Level-3-220C-168 HR,引脚镀层/焊球材料:SNPB,TI官网TMS320VC5502GBE300的批量USD价格:6.31(1000+)

TMS320VC5502PGF200,工作温度:-40 to 85,封装:LQFP (PGF)-176,包装数量MPQ:40个,MSL 等级/回流焊峰值温度:Level-4-260C-72 HR,引脚镀层/焊球材料:NIPDAU,TI官网TMS320VC5502PGF200的批量USD价格:6.31(1000+)

TMS320VC5502PGF300,工作温度:-40 to 85,封装:LQFP (PGF)-176,包装数量MPQ:40个,MSL 等级/回流焊峰值温度:Level-4-260C-72 HR,引脚镀层/焊球材料:NIPDAU,TI官网TMS320VC5502PGF300的批量USD价格:8.203(1000+)

TMS320VC5502ZAV200,工作温度:-40 to 85,封装:NFBGA (ZAV)-201,包装数量MPQ:126个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:SNAGCU,TI官网TMS320VC5502ZAV200的批量USD价格:6.31(1000+)

TMS320VC5502ZAV300,工作温度:-40 to 85,封装:NFBGA (ZAV)-201,包装数量MPQ:126个,MSL 等级/回流焊峰值温度:Level-3-260C-168 HR,引脚镀层/焊球材料:SNAGCU,TI官网TMS320VC5502ZAV300的批量USD价格:8.203(1000+)

TMDSEMU200-U Spectrum Digital XDS200 USB 仿真器

Spectrum Digital XDS200 是最新 XDS200 系列 TI 处理器调试探针(仿真器)的首个模型。XDS200 系列拥有超低成本 XDS100 与高性能 XDS560v2 之间的低成本与高性能的完美平衡。此外,对于带有嵌入式缓冲跟踪器 (ETB) 的所有 ARM 和 DSP 处理器,所有 XDS 调试探针均支持内核和系统跟踪。

Spectrum Digital XDS200 通过 TI 20 引脚连接器(带有适合 TI 14 引脚、TI 10 引脚和 ARM 20 引脚的多个适配器)连接到目标板,而通过 USB2.0 高速连接 (480Mbps) 连接到主机 PC。要在主机 (...)

TMDSEMU560V2STM-U Blackhawk XDS560v2 系统跟踪 USB 仿真器

XDS560v2 System Trace 是 XDS560v2 系列高性能 TI 处理器调试探针(仿真器)的第一种型号。XDS560v2 是 XDS 系列调试探针中性能最高的一款,同时支持传统 JTAG 标准 (IEEE1149.1) 和 cJTAG (IEEE1149.7)。

XDS560v2 System Trace 在其巨大的外部存储器缓冲区中加入了系统引脚跟踪。这种外部存储器缓冲区适用于指定的 TI 器件,通过捕获相关器件级信息,获得准确的总线性能活动和吞吐量,并对内核和外设进行电源管理。此外,对于带有嵌入式缓冲跟踪器 (ETB) 的所有 ARM 和 DSP 处理器,所有 XDS (...)

TMDSEMU560V2STM-UE Spectrum Digital XDS560v2 系统跟踪 USB 和以太网

XDS560v2 System Trace 是 XDS560v2 系列高性能 TI 处理器调试探针(仿真器)的第一种型号。XDS560v2 是 XDS 系列调试探针中性能最高的一款,同时支持传统 JTAG 标准 (IEEE1149.1) 和 cJTAG (IEEE1149.7)。

XDS560v2 System Trace 在其巨大的外部存储器缓冲区中加入了系统引脚跟踪。这种外部存储器缓冲区适用于指定的 TI 器件,通过捕获相关器件级信息,获得准确的总线性能活动和吞吐量,并对内核和外设进行电源管理。此外,对于带有嵌入式缓冲跟踪器 (ETB) 的所有 ARM 和 DSP 处理器,所有 XDS (...)

C55XCODECSAUD — 用于 C55x 的音频编解码器 - 软件和文档

The DSP Library (DSPLIB) is a collection of high-level optimized DSP function modules for the C55x DSP platform. This source-code library includes C-callable functions (ANSI-C language compatible) for general signal processing math and vector functions that have been ported to C55x DSPs. The (...)TELECOMLIB 用于 TMS320C64x+ 和 TMS320C55x 处理器的电信和媒体库 - FAXLIB、VoLIB 和 AEC/AER

Voice Library- VoLIBprovides components that, together, facilitate the development of the signal processing chain for Voice over IP applications such as infrastructure, enterprise, residential gateways and IP phones. Together with optimized implementations of ITU-T voice codecs, that can be (...)C5502 PGF BSDL Model (Rev. A)

TI has partnered with companies to offer a wide range of software, tools, and SOMs using TI processors to accelerate your path to production. Download this search tool to quickly browse our third-party solutions and find the right third-party to meet your needs. The software, tools and modules (...)