- 制造厂商:TI

- 产品类别:电源管理

- 技术类目:直流/直流开关稳压器 - 降压稳压器

- 功能描述:2.95V 至 6V 输入 3A SWIFT 同步降压转换器

- 点击这里打开及下载TPS54318的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

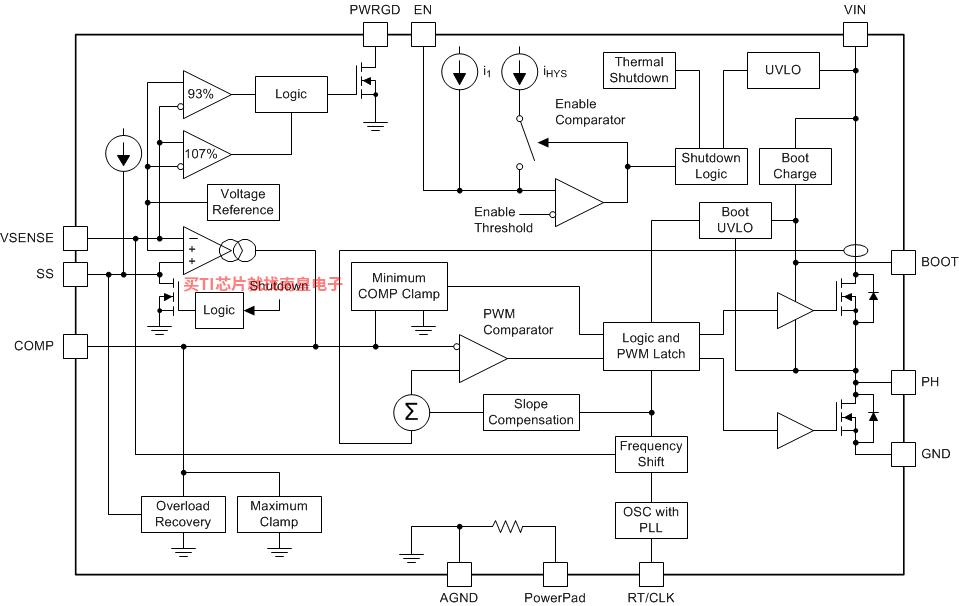

TPS54318 器件一款全功能 6V、3A 同步降压电流模式转换器,具有两个集成的 MOSFET。

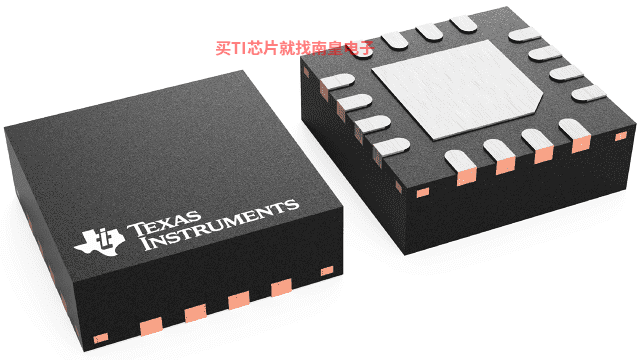

TPS54318 器件集成了 MOSFET、通过实施电流模式控制来减少外部组件数量、通过启用高达 2MHz的开关频率来减小电感尺寸,并借助小型 3mm x 3mm 热增强型 QFN 封装尽量减小器件封装尺寸,从而实现小型设计。

TPS54318 器件可在整个温度范围内为多种负载提供电压基准 (VREF) 精度达 ±1% 的精确调节。

通过集成型 30mΩ MOSFET 和典型值为 350µA 的电源电流可使效率得到最大限度提升。通过使用 EN 引脚进入关断模式,关断电源电流可减少至 2µA。

欠压闭锁在内部设定为 2.6V,但可通过使能引脚上的电阻网络设定阈值将之提高。输出电压启动斜坡由软启动引脚控制。一个开漏电源正常信号表示输出处于其标称电压值的 93% 至 107% 之内。频率折返和热关断功能在过流情况下保护器件不受损坏。

要获得更多 SWIFT ™文档,请参见 TI 网站 www.ti.com.cn/swift。

- 两个可在 3A 负载下获得高效率的 30m?(典型值)MOSFET

- 开关频率:200kHz 至 2MHz

- 整个温度范围内的电压基准:0.8V ± 1%

- 同步至外部时钟

- 可调软启动/定序

- 欠压 (UV) 和过压 (OV) 电源正常输出

- 低运行和关断静态电流

- 安全启动至预偏置输出电压

- 逐周期电流限制、过热和频率折返保护

- 工作结温范围:-40°C 至 150°C

- 耐热增强型 3mm x 3mm 16 引脚超薄型四方扁平无引线 (WQFN) 封装

- 使用 TPS54318 并借助 WEBENCH? 电源设计器创建定制设计方案

- Vin (Min) (V)

- 2.95

- Vin (Max) (V)

- 6

- Vout (Min) (V)

- 0.8

- Vout (Max) (V)

- 4.5

- Iout (Max) (A)

- 3

- Iq (Typ) (uA)

- 350

- Switching frequency (Min) (kHz)

- 200

- Switching frequency (Max) (kHz)

- 2000

- Features

- Enable, Frequency Synchronization, Power Good, Pre-Bias Start-Up, Synchronous Rectification, UVLO Adjustable, Soft Start Adjustable

- Rating

- Catalog

- Regulated outputs (#)

- 1

- Control mode

- Current Mode

- Duty cycle (Max) (%)

- 98

TPS54318的完整型号有:TPS54318RTER、TPS54318RTET,以下是这些产品的关键参数及官网采购报价:

TPS54318RTER,工作温度:-40 to 150,封装:WQFN (RTE)-16,包装数量MPQ:3000个,MSL 等级/回流焊峰值温度:Level-2-260C-1 YEAR,引脚镀层/焊球材料:NIPDAU,TI官网TPS54318RTER的批量USD价格:.627(1000+)

TPS54318RTET,工作温度:-40 to 150,封装:WQFN (RTE)-16,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-2-260C-1 YEAR,引脚镀层/焊球材料:NIPDAU,TI官网TPS54318RTET的批量USD价格:.752(1000+)

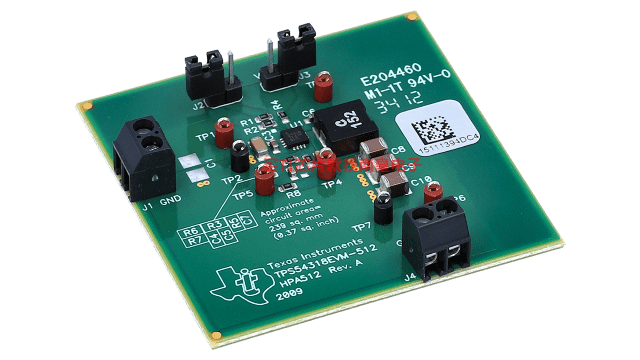

TPS54318EVM-512 ― TPS54318 6V 输入、1.8 输出、3A SWIFT™ 转换器评估模块

TPS54318EVM-512 评估模块旨在演示使用 TPS54318 稳压器进行设计时可实现的小印制电路板面积。TPS54318 dc/dc 转换器设计用于以 2.95V 至 6V 的输入电压提供 3A 的输出电流。用户指南的表 1 中列出了评估模块的额定输入电压和输出电流范围。开关频率被外部设置为 1000kHz 的额定频率。TPS54318 封装内部采用了高端和低端 MOSFET 以及栅极驱动器电路。MOSFET 的漏源电阻能使 TPS54318 实现高效率,并在高输出电流的情况下帮助保持低结温。补偿组件位于集成电路 (IC) (...)TPS54318 Unencrypted PSpice Transient Model Package (Rev. A)

PSpice for TI 可提供帮助评估模拟电路功能的设计和仿真环境。此功能齐全的设计和仿真套件使用 Cadence 的模拟分析引擎。PSpice for TI 可免费使用,包括业内超大的模型库之一,涵盖我们的模拟和电源产品系列以及精选的模拟行为模型。借助?PSpice for TI 的设计和仿真环境及其内置的模型库,您可对复杂的混合信号设计进行仿真。创建完整的终端设备设计和原型解决方案,然后再进行布局和制造,可缩短产品上市时间并降低开发成本。

在?PSpice for TI 设计和仿真工具中,您可以搜索 TI (...)

TPS54620DESIGN-CALC ― TPS54620 & TPS54XXX 电流型降压转换器设计计算器

设计计算器与应用手册 (SLVA352A) 计算器工具可以计算 TPS54620/TPS54622/TPS54521/TPS54320/TPS54618/TPS54418/TPS54318/TPS54218/TPS54319 的临界外部组件值。此计算器包括功率级设计、功能设计以及类型 II 和类型 III 补偿设计,并且使用数据表方程和应用手册 (SLVA352A) 方程。此计算器利用常规功率级和补偿设计代数,可对大多数电流模式降压 DC/DC 转换器进行修改Power Distribution for Altera Arria II GX, Option 2

相控阵雷达、无线通信测试仪和电子战等高速终端设备的模拟前端需要同步的多收发器信号链。每个收发器信号链都包括高速模数转换器 (ADC)、数模转换器 (DAC) 和时钟子系统。时钟子系统提供低噪声采样时钟,具备精细的延迟调节功能,可实现最低的通道间偏差和最佳的系统性能,如信噪比 (SNR)、无杂散动态范围 (SFDR)、IMD3 和有效位数 (ENOB) 等。此参考设计通过 AFE7444 EVM 展示了多通道 JESD204B 时钟生成和系统性能。通过高达 2.6GHz 射频的 6GSPS/3GSPS DAC/ADC 时钟实现的优于 10ps 的通道间偏差以及 SNR 和 SFDR (...)TIDA-01021 ― 适用于 DSO、雷达和 5G 无线测试仪的多通道 JESD204B 15GHz 时钟参考设计

High speed multi-channel applications require precise clocking solutions capable of managing channel-to-channel skew in order to achieve optimal system SNR, SFDR, and ENOB. This reference design is capable of supporting two high speed channels on separate boards by utilizing TI’s LMX2594 (...)TIDA-01024 ― 适用于雷达和 5G 无线测试仪的高通道数 JESD204B 菊链时钟参考设计

高速多通道应用需要低噪声、可扩展且可进行精确通道间偏斜调节的时钟解决方案,以实现最佳系统 SNR、SFDR 和 ENOB。此参考设计支持在菊链配置中增加 JESD204B 同步时钟。此设计可提供多通道 JESD204B 时钟,采用 TI LMK04828 时钟抖动清除器和带有集成式 VCO 的 LMX2594 宽带 PLL,能够实现低于 10ps 的时钟间偏斜。此设计经过 TI ADC12DJ3200 EVM 在 3GSPS 环境中检测,具有改善的 SNR 性能,通道间偏斜低于 (...)TIDA-01023 ― 适用于雷达和 5G 无线测试仪的高通道数 JESD204B 时钟生成参考设计

高速多通道应用需要低噪声、可扩展且可进行精确通道间偏差调节的时钟解决方案,以实现最佳系统 SNR、SFDR 和 ENOB。此参考设计使用一个主时钟器件和多个从时钟器件,支持高通道数 JESD204B 同步时钟。此设计可提供多通道 JESD204B 时钟,采用 TI LMK04828 时钟抖动清除器和带有集成式 VCO 的 LMX2594 宽带 PLL,能够实现低于 10ps 的时钟间偏差。此设计经过 TI ADC12DJ3200 EVM 在 3GSPS 环境中检测,具有改善的 SNR 性能,通道间偏差低于 (...)