- ���쳧�̣�TI

- ��Ʒ�����Դ����

- ������Ŀ��ֱ��/ֱ��������ѹ�� - ��ѹ��ѹ��

- ����������4.5V �� 18V ���룬3A ͬ����ѹת����

- ������������TPS54327�ļ����ĵ�����

- TI�����������ṩ���շ������ϸ������������������Ŀ��۸�

The TPS54327 device is an adaptive on-time D-CAP2™ mode synchronous buck converter. TheTPS54327 enables system designers to complete the suite of various end equipment’s power bus regulators with a cost effective, low component count, low standby current solution. The main control loop for the TPS54327 uses the D-CAP2 mode control which provides a fast transient response with no external compensation components. The TPS54327 also has a proprietary circuit that enables the device to adopt to both low equivalent series resistance (ESR) output capacitors, such as POSCAP or SP-CAP, and ultra-low ESR ceramic capacitors. The device operates from 4.5-V to 18-V VIN input. The output voltage can be programmed between 0.76 V and 7 V. The device also features an adjustable soft start time. The TPS54327 is available in the 8-pin DDA package and 10-pin DRC, and is designed to operate from –40°C to 85°C.

- D-CAP2? Mode Enables Fast Transient Response

- Low-Output Ripple and Allows Ceramic Output Capacitor

- Wide VIN Input Voltage Range: 4.5 V to 18 V

- Output Voltage Range: 0.76 V to 7 V

- Highly Efficient Integrated FETs Optimized for Lower Duty Cycle Applications �C 100 m�� (High-Side) and 70 m�� (Low-Side)

- High Efficiency, Less Than 10 ��A at shutdown

- High Initial Bandgap Reference Accuracy

- Adjustable Soft Start

- Prebiased Soft Start

- 700-kHz Switching Frequency (fSW)

- Cycle-By-Cycle Overcurrent Limit

- APPLICATIONS

- Wide Range of Applications for Low Voltage System

- Digital TV Power Supply

- High Definition Blu-ray Disc? Players

- Networking Home Terminal

- Digital Set Top Box (STB)

- Wide Range of Applications for Low Voltage System

All other trademarks are the property of their respective owners

- Vin (Min) (V)

- 4.5

- Vin (Max) (V)

- 18

- Vout (Min) (V)

- 0.76

- Vout (Max) (V)

- 7

- Iout (Max) (A)

- 3

- Iq (Typ) (uA)

- 800

- Switching frequency (Min) (kHz)

- 700

- Switching frequency (Max) (kHz)

- 700

- Features

- Enable, Synchronous Rectification, Soft Start Adjustable

- Rating

- Catalog

- Regulated outputs (#)

- 1

- Control mode

- D-CAP2

- Duty cycle (Max) (%)

- 65

TPS54327�������ͺ��У�TPS54327DDA��TPS54327DDAR��TPS54327DRCR��TPS54327DRCT����������Щ��Ʒ�Ĺؼ������������ɹ����ۣ�

TPS54327DDA�������¶ȣ�-40 to 85����װ��SO PowerPAD (DDA)-8����װ����MPQ��75����MSL �ȼ�/��������ֵ�¶ȣ�Level-2-260C-1 YEAR�����ŶƲ�/������ϣ�NIPDAU��TI����TPS54327DDA������USD�۸�.502��1000+��

TPS54327DDAR�������¶ȣ�-40 to 85����װ��SO PowerPAD (DDA)-8����װ����MPQ��2500����MSL �ȼ�/��������ֵ�¶ȣ�Level-2-260C-1 YEAR�����ŶƲ�/������ϣ�NIPDAU��TI����TPS54327DDAR������USD�۸�.418��1000+��

TPS54327DRCR�������¶ȣ�-40 to 85����װ��VSON (DRC)-10����װ����MPQ��3000����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�NIPDAU��TI����TPS54327DRCR������USD�۸�.468��1000+��

TPS54327DRCT�������¶ȣ�-40 to 85����װ��VSON (DRC)-10����װ����MPQ��250����MSL �ȼ�/��������ֵ�¶ȣ�Level-1-260C-UNLIM�����ŶƲ�/������ϣ�NIPDAU��TI����TPS54327DRCT������USD�۸�.552��1000+��

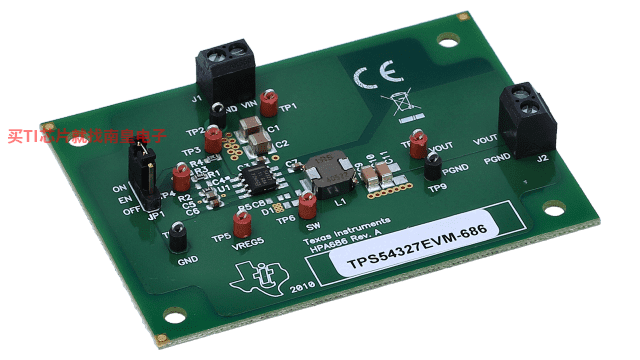

TPS54327EVM-686 �� ���� TPS54327 3A ͬ����ѹת����������ģ��

TPS54327EVM-686 ��һ����װ�걸�Ҿ������Եĵ�·���������� TPS54327 ͬ����ѹת������TPS54327EVM-686 �� 4.5V �� 18V �����ѹ��Χ�����У��ҿ������ 3A �ĸ������ṩ 1.05V �������ѹ��TPS54327 �������ƻ�·���� D-CAP2™ ģʽ���ƣ���������λ������ʹ���ⲿ�������ʵ�ֳ����˲̬��Ӧ��

TPS54327 PSPICE (Transient) Model

PSpice for TI ���ṩ��������ģ���·���ܵ���ƺͷ��滷�����˹�����ȫ����ƺͷ�����ʹ�� Cadence ��ģ��������档PSpice for TI �����ʹ�ã�����ҵ�ڳ����ģ�Ϳ�֮һ���������ǵ�ģ��͵�Դ��Ʒϵ���Լ���ѡ��ģ����Ϊģ�͡�����?PSpice for TI ����ƺͷ��滷���������õ�ģ�Ϳ⣬���ɶԸ��ӵĻ���ź���ƽ��з��档�����������ն��豸��ƺ�ԭ�ͽ��������Ȼ���ٽ��в��ֺ����죬�����̲�Ʒ����ʱ�䲢���Ϳ����ɱ���

��?PSpice for TI ��ƺͷ��湤���У����������� TI (...)

TIDA-00431 �� �ο���� - ���� 8GHz ֱ�����ȫ��ַŴ����� RF ���� 4GSPS ADC

������Ƶ (RF) �����������ڼ����������ߵ�����е�����ԡ��Ͽ���˲ʱ����֧�������ڶ�����Ķ�Ӳ�����ܹ��Լ���ϴ��Ƶ�ʲ�����ͨ�����˲ο���ƽ�����һ��������Ƶ���������ý��������� 4 GSPS ģ��ת���� (ADC) ������һ�� 8GHz ֱ�����ȫ��Ŵ���ǰ�ˡ��Ŵ���ǰ���ṩ�ź����沢�����ɼ����е�ֱ�����źţ���ƽ��-��ƽ���ѹ�������������������һ�㡣

TIDA-01017 �� ������ʾ���������߲��������״�ĸ��ٶ�ͨ�� ADC ʱ�Ӳο����

TIDA-01017 �ο����չʾ�������ڸ��ٶ�ͨ��ϵͳ��ʱ�ӽ�����������ܣ�ͨ��������Ƶ���� ADC ����������Ƶ�ʷ�Χ��ͨ����ƫ����з�����ͨ����ƫ�����������״��ʾ����Ӧ��������Ҫ��ADC12J4000 ��һ����ġ�12 λ��4GSPS ��Ƶ����ģ��ת���� (ADC)�����л���ģ�����롢����ʽ�����±�Ƶ�������� JESD204B �ӿڣ����ɲ���ߴ� 4GHz ���źš������չʾ��ʹ�� LMK04828 ��ʱ�ӽ����������ʹ��ͬ�� SYSREF �ڶ�� ADC12J4000 �ź���֮��ʵ��ͬ����TIDA-01015 �� ����������ʾ���������߲������е� 12 λ���� ADC �� 4GHz ʱ�Ӳο����

TIDA-01015 ��һ���ʺϸ���ֱ����Ƶ���� GSPS ADC ��ʱ�ӽ�������ο���ơ��òο����չʾ�˲���ʱ����Ϊ�ڶ��ο�˹�����������ź�Ƶ��ʵ�ָ� SNR �������Ҫ�ԡ�ADC12J4000 ��һ�� 12 λ 4GSPS ��Ƶ���� ADC������ 3.2GHz �� 3dB ����������ܹ�����ߴ� 4GHz ���źš��˲ο����ͻ����һ���ʺ� ADC12J4000 ��ʱ�ӽ������������������ TRF3765�����ڸ�����Ƶ��������ʵ�ָ� SNR ���ܣ����������ִ洢ʾ���� (DSO) �����߲����ǵ�Ӧ�á�TIDA-00826 �� 50�� 2GHz ʾ����ǰ�˲ο����

�˲ο������ 50�� ����ʾ����Ӧ�õ�ģ��ǰ�˵�һ���֡�ϵͳ�����Ա������ʹ�ô�����ƽ̨������Ƶ���ʱ��Ӧ���е�ֱ���� 2GHz �������źš�TIDA-00432 �� �� Xilinx ƽ̨Ӧ������λ�����״�ϵͳ��ʵ�� JESD204B ǧ�״β��� ADC ��ͬ��

��ϵͳ�����չʾ�����ʹ�� Xilinx VC707 ƽ̨һ��ͬ������ ADC12J4000 ����ģ�� (EVM)��������ĵ������˱�Ҫ��Ӳ���ĺ��������ã�����ʱ�ӷ������������ʾ��ÿ�� EVM ��ʾ�������ļ�������ƽ����� FPGA �̼�������ʾ��ص� Xilinx IP �����ò����������ʾ����������ʵ��Ӳ���ϲɼ������ݣ����Խ����ʾ�� 50ps �ڵ�ͬ����δʹ�����Ի����£�ҲδУ�����ӳ١�TIDA-00359 �� ���� GSPS ADC ��ʱ�ӽ�������ο����

������ GSPS ����ת�����ĵͳɱ���������ʱ�ӽ���������˲ο�����������ʹ�õ�����Ƶ�ʺϳ��� TRF3765 Ϊ 4 GSPS ģ��ת���� (ADC12J4000) ���ɲ���ʱ�ӡ�ʵ��չʾ�������ݱ��൱�� SNR �� SFDR ���ܡ�PMP6638 �� Sync Buck Regulators

�˲ο�����ǻ������ڵ�Դ����ʾ�������� 12V ��Դִ�� DC-DC ת�����Ի�� 1.0V/1.2V/1.8V/2.5V/3.3V/5V ��Դ�졣