- 制造厂商:TI

- 产品类别:电源管理

- 技术类目:线性和低压降 (LDO) 稳压器

- 功能描述:3A、低输入电压 (0.8V)、低噪声、高 PSRR、可调节超低压降稳压器

- 点击这里打开及下载TPS74401的技术文档资料

- TI代理渠道,提供当日发货、严格的质量标准,满足您的目标价格

TPS74401 低压降 (LDO) 线性稳压器提供了一套面向多种应用的易用稳健型电源管理 解决方案。用户可编程的软启动功能可降低器件启动时的电容浪涌电流,从而以最大限度减小输入电源的应力。软启动具有单调性,非常适合为各类处理器和专用集成电路 (ASIC) 供电。借助使能输入和电源正常输出,可通过外部稳压器轻松实现上电排序。凭借全方位的灵活性,用户可为现场可编程门阵列 (FPGA)、数字信号处理器 (DSP) 等具有特殊启动要求的应用配置出一套可满足其 排序要求的 解决方案。

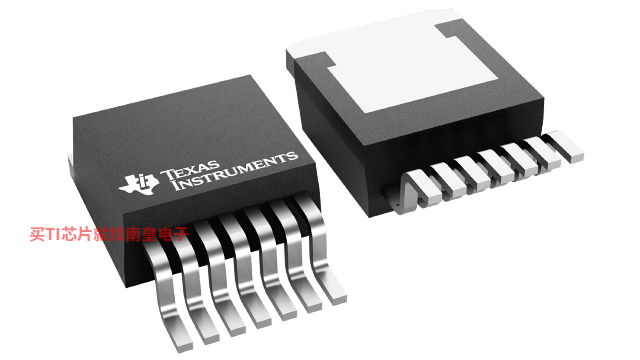

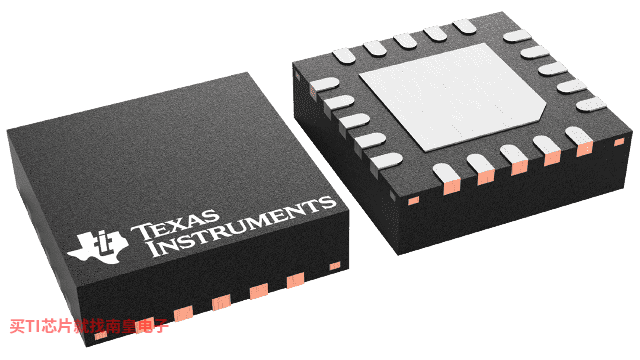

该器件还具有高精度的参考电压电路和误差放大器,可在整个负载、线路、温度和过程范围内提供 1% 精度。TPS74401 系列 LDO 在不使用输出电容或搭配使用陶瓷输出电容时都可以稳定运行。该器件系列的额定工作温度范围为 TJ = –40°C 至 125°C。 TPS74401 可提供两种 20 引脚小型 VQFN 封装(一个 5mm × 5mm RGW 和一个

3.5mm × 3.5mm RGR 封装),因此总体解决方案尺寸高度紧凑。对于 要求 额外功率耗散的应用,还提供了 DDPAK (KTW) 封装。

- 输入电压范围:1.1V 至 5.5V

- 软启动 (SS) 引脚可借助由外部电容器设置的斜坡时间实现线性启动

- 线路、负载和温度上精度 1%

- 借助外部偏置电源可支持低至 0.9V 的输入电压

- 可调节输出电压范围:0.8V 至 3.6V

- 超低压降:3.0A 时为 115mV(典型值)

- 搭配使用任意输出电容或不使用输出电容时均可保持稳定

- 出色的瞬态响应

- 漏极开路电源正常输出(仅限 VQFN)

- 封装:5mm × 5mm × 1mm VQFN (RGW),3.5mm × 3.5mm VQFN (RGR) 和 DDPAK

- Output options

- Adjustable Output

- Iout (Max) (A)

- 3

- Vin (Max) (V)

- 5.5

- Vin (Min) (V)

- 0.8

- Vout (Max) (V)

- 3.6

- Vout (Min) (V)

- 0.8

- Noise (uVrms)

- 13

- Iq (Typ) (mA)

- 3

- Thermal resistance θJA (°C/W)

- 27

- Rating

- Catalog

- Load capacitance (Min) (μF)

- 0

- Regulated outputs (#)

- 1

- Features

- Enable, Power good, Soft start

- Accuracy (%)

- 1

- PSRR @ 100 KHz (dB)

- 50

- Dropout voltage (Vdo) (Typ) (mV)

- 115

- Operating temperature range (C)

- -40 to 125

TPS74401的完整型号有:TPS74401KTWR、TPS74401RGRR、TPS74401RGRT、TPS74401RGWR、TPS74401RGWT,以下是这些产品的关键参数及官网采购报价:

TPS74401KTWR,工作温度:-40 to 125,封装:DDPAK/TO-263 (KTW)-7,包装数量MPQ:500个,MSL 等级/回流焊峰值温度:Level-3-245C-168 HR,引脚镀层/焊球材料:Call TI,TI官网TPS74401KTWR的批量USD价格:2.856(1000+)

TPS74401RGRR,工作温度:-40 to 125,封装:VQFN (RGR)-20,包装数量MPQ:3000个,MSL 等级/回流焊峰值温度:Level-2-260C-1 YEAR,引脚镀层/焊球材料:NIPDAU,TI官网TPS74401RGRR的批量USD价格:2.42(1000+)

TPS74401RGRT,工作温度:-40 to 125,封装:VQFN (RGR)-20,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-2-260C-1 YEAR,引脚镀层/焊球材料:NIPDAU,TI官网TPS74401RGRT的批量USD价格:2.904(1000+)

TPS74401RGWR,工作温度:-40 to 125,封装:VQFN (RGW)-20,包装数量MPQ:3000个,MSL 等级/回流焊峰值温度:Level-2-260C-1 YEAR,引脚镀层/焊球材料:NIPDAU,TI官网TPS74401RGWR的批量USD价格:2.928(1000+)

TPS74401RGWT,工作温度:-40 to 125,封装:VQFN (RGW)-20,包装数量MPQ:250个,MSL 等级/回流焊峰值温度:Level-2-260C-1 YEAR,引脚镀层/焊球材料:NIPDAU,TI官网TPS74401RGWT的批量USD价格:3.514(1000+)

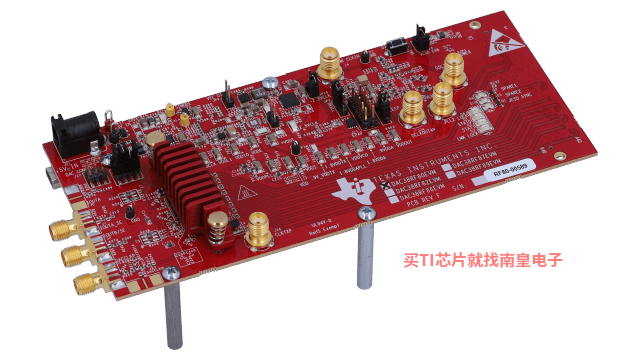

DAC38RF80EVM ― DAC38RF80 评估模块

DAC38RF80EVM 是用于评估 DAC38RF80/84/90 数模转换器 (DAC) 的电路板。该 EVM 可用于对采样率高达 9GSPS 的 DAC 进行性能评估。它适合与基于 FPGA 的图形发生器卡 TSW14J56EVM(修订版 B 及以上版本)搭配使用。该 EVM 上提供的 FMC 连接器还可以将 DAC 与第三方供应商的 FPGA 开发板相连接。此外,借助易于使用的软件界面,还可通过 SPI 来控制 DAC 和板载 LMK04828 时钟芯片。

DAC38RF82EVM ― DAC38RF82 双通道 14 位 9GSPS 1x-24x 内插 6GHz 和 9GHz PLL DAC 评估模块

DAC38RF82EVM 是用于评估 DAC38RF82/83/85/93 数模转换器 (DAC) 的电路板。该 EVM 可用于对采样率高达 9GSPS 的 DAC 进行性能评估,专为与 TSW14J56 EVM 配合使用而设计。此外,借助所提供的 FMC 连接器还可将 DAC 连接到来自第三方供应商的 FPGA 开发板。此外,借助易于使用的软件界面,还可通过 SPI 来控制 DAC 和板载 LMK04828 时钟芯片。DAC38RF89EVM ― DAC38RF89 双通道 14 位 8.4GSPS 1x-24x 插值 5GHz 和 7.5GHz PLL DAC 评估模块

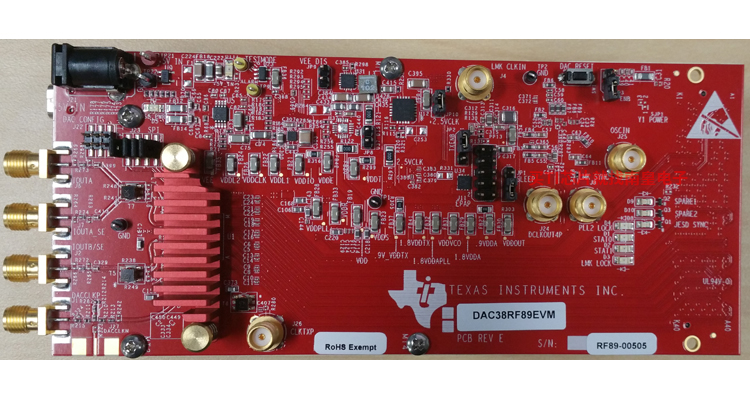

DAC38RF89 评估模块 (EVM) 是用于评估 DAC38RF89 数模转换器 (DAC) 的电路板。该 DAC38RFEVM 可用于对采样率高达 9GSPS 的 DAC 进行性能评估,同时还设计用于与 TSW14J56EVM(修订版 B 及更高版本)搭配使用。提供的 FMC 连接器还可以将 DAC 与第三方供应商的 FPGA 开发板相连接。此外,借助易于使用的软件界面,还可通过 SPI 来控制 DAC 和板载 LMK04828 时钟芯片。

TPS74401EVM-118 ― TPS74401 Evaluation Module

The TPS74401EVM-118 evaluation module (EVM) is designed to help the user easily evaluate and test the operation and functionality of the TPS74401 LDO linear regulator. The EVM uses the TPS74401, 3A linear regulator with programmable soft-start and integrated power good (PG). Refer to (...)

TPS74401 Unencrypted PSpice Transient Model

此参考设计在不牺牲性能的情况下为射频采样 DAC38RF8x 数模转换器 (DAC) 的加电启动提供了一种高效电源方案,并且可以降低板面积和 BOM。该参考设计使用直流/直流开关和 LDO 为 DAC38RF8x 加电,同时实现高的模拟性能(杂散噪声和相位噪声)并最大限度地减少电源效率折衷。可以将此处概括的设计方法扩展到其他射频采样数据转换器的电源设计。TIDA-01240 ― 射频采样 S 频带雷达发送器参考设计

借助使用 DAC38RF80(一种 9GSPS 16 位数模转换器 (DAC))的射频采样架构,对适用于 S 频带多功能相控阵雷达 (MPAR) 的波形合成进行了展示。该射频采样发送架构可简化信号链,拉近数据转换器与天线之间的距离,从而实现灵活性和高性能。TIDA-01084 ― 连续波相位对齐型多音调发生器:直流转 6GHz 射频采样 DAC 参考设计

TIDA-01084 参考设计演示了如何使用射频采样 DAC 来生成连续相位对齐多音波形。14 位的 9GSPS DAC38RF83 具有四个 48 位独立 NCO,可以生成四个置于第一个奈奎斯特区域内任何位置的 CW 音调,或者在第二个奈奎斯特区域中支持高达 6 GHz。此参考设计涵盖操作理论、GUI 介绍以及关于通过 NCO 编程生成音调而不需要外部信号发生器的说明。此设计展示了一种易于使用的方法,通过这种方法极大地简化和缩减了生成连续波形所需的物料清单 (BOM)。

TIDA-00352 ― SDI 视频聚合参考设计

这款经过验证的参考设计是一个完整的四通道 SDI 聚合与解聚解决方案。使用一个 TLK10022 将四个同步 HD-SDI 源聚合到一条 5.94 Gbps 串行链路中。串行数据经由铜缆或光缆传输;使用另一个 TLK10022 来解聚并无缝重现原始视频内容。TIDA-00309 ― DisplayPort 视频 4:1 聚合参考设计

这款经过验证的参考设计是一个完整的四通道 DisplayPort 聚合与解聚解决方案。其中使用一个 TLK10022 将四个同步 DisplayPort (DP) 源一起聚合到一条 10.8 Gbps 串行链路中。串行数据经由铜缆或光缆传输,其中使用另一个 TLK10022 来解聚并无缝重现原始视频内容。TIDA-00270 ― 电流均流双路 LDO

此电源拓扑能够通过两个并联工作的 LDO 提供 6A 电流。此解决方案在两个 TPS74401 之间均匀提供电流,每个能够提供 3A 电流。此设计可提供的电流高于通常使用单个 LDO 能够提供的电流。另外,此设计还允许额外的热同步,这是单个 LDO 无法提供的。TIDA-00269 ― 千兆以太网链路聚合器参考设计

千兆位以太网链路聚合器参考设计采用了 TLK10081 器件,这是一种多速率链路聚合器,用于高速双向点对点数据传输系统,可将低速串行链路多路复用为高速串行链路,从而降低物理链路的数目。此参考设计帮助客户降低需要在应用中实施和管理的串行链路的数目。TLK10081 让客户可以聚合与解聚多个串行链路 - 所有类型的串行链路,包括原始数据类型。此外,还采用 CDCM6208 器件,该器件可以向没有极低抖动时钟输入(或不符合系统的抖动要求)的客户系统中的 TLK10081 提供该时钟输入。通道 A 的高速信号已经被路由到 SFP+ 模块,以便在实施光缆配置的系统中轻松评估。通道 B (...)TIDA-00234 ― 用于具有两个或更多 SFP+ 光纤端口的系统的双通道 XAUI 转 SFI 参考设计

TIDA-00234 XAUI 至 SFI 参考设计适用于企业和服务提供商网络应用,如实现多个 10G 以太网兼容光学 (SFP+) 端口的以太网交换机和路由器等。该参考设计采用 TLK10232 器件,该器件是最紧凑型双通道 XAUI 至 SFI 收发器,在同类产品中具有最低的功耗。此参考设计允许访问由 TLK10232(通过 SMA 连接器)或 SFP+ 模块(通过 SFP+ 光学模块仓)生成的高速信号(高达 10Gbps)。此外,还采用 CDCM6208 器件,该器件可以向没有极低抖动时钟输入(或不符合系统的抖动要求)的客户系统中的 TLK10232 提供该时钟输入。TIDA-00069 ― FPGA 固件示例,说明如何将 Altera FPGA 连接到高速 LVDS 接口数据转换器

该参考设计和相关的示例 Verilog 代码可用作将 Altera FPGA 连接到德州仪器 (TI) 高速 LVDS 接口模数转换器 (ADC) 和数模转换器 (DAC) 的起点。其中说明了固件实施并介绍了所需的计时限制。